BYLink System Power Platform

This platform facilitates the design of safe power management systems thanks to a portfolio of configurable and linkable devices. It simplifies complex power supply subsystems into a single smart solution.

Sign in for a personalized NXP experience.

Click over video to play

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

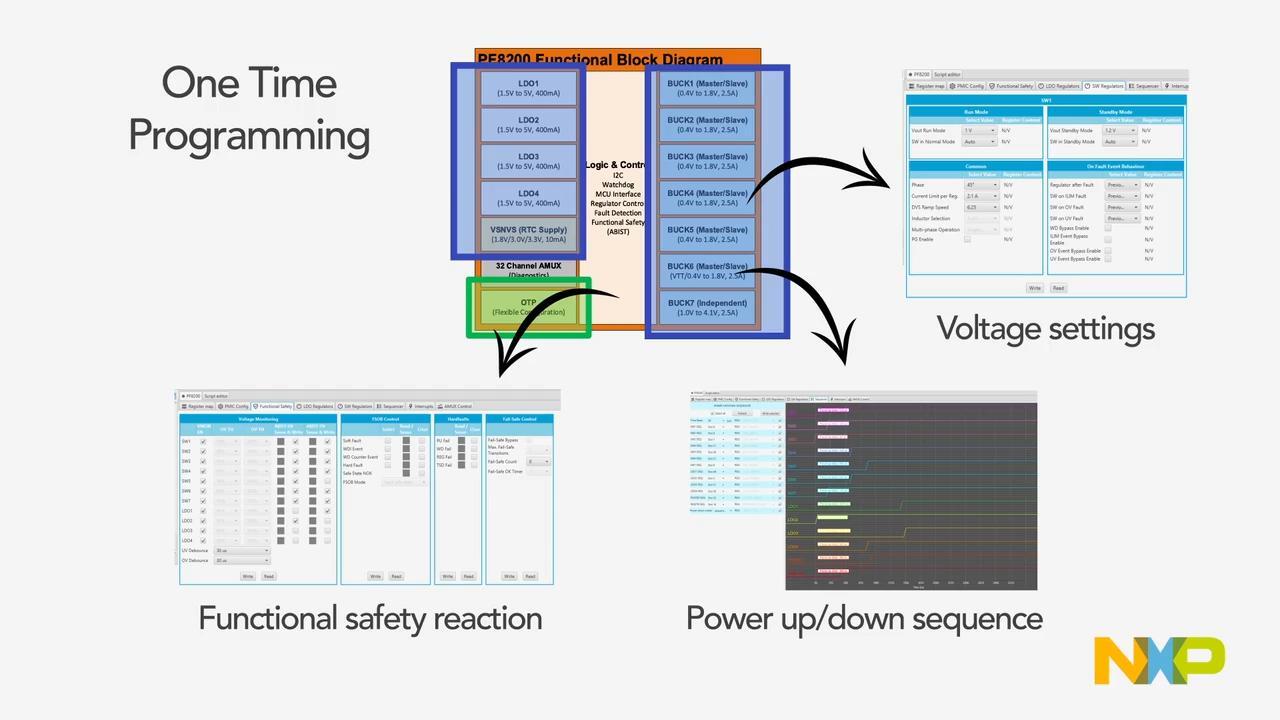

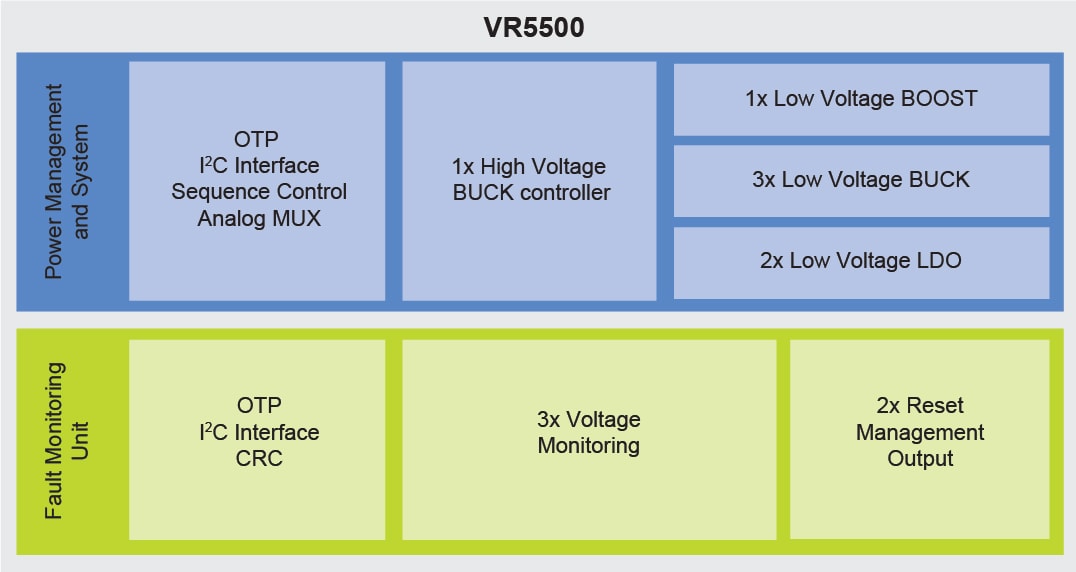

The VR55 is an automotive high voltage multi-output power supply integrated circuit, with focus on radio, telematics and infotainment applications. It includes multiple switch mode and linear voltage regulators.

This PMIC is part of a complete family of devices offering scalability in power and safety FS84 (ASIL B) and FS85 (ASIL D), pin to pin and software compatible.

Note: To see the product features close this window.

| Part number | Buck 1 | Buck 2 | Buck 3 | Vpre | Boost | Safety level |

|---|---|---|---|---|---|---|

| VR5500 | 0.8 V - 1.8 V 2.5 A Multi-phase and SVS option |

12 / 24 V HV BUCK - 10 A |

5 V - 5.74 V 1.5 A peak |

Quality Mgt (QM) | ||

| FS8400 | N/A | N/A | Fit for ASIL B | |||

| FS8500 | Fit for ASIL D | |||||

| FS5502 | 1.0 V - 4.1 V 3.6 A peak |

N/A | Quality Mgt (QM) | |||

| FS8410 | 5 V - 5.74 V 1.5 A peak |

Fit for ASIL B | ||||

| FS8510 | Fit for ASIL D | |||||

| FS8420 | 0.8 V - 1.8 V 2.5 A Multi-phase and SVS option |

N/A | Fit for ASIL B | |||

| FS8520 | Fit for ASIL D | |||||

| FS8430 | 1.0 V - 3.3 V 2.5 A |

Fit for ASIL B | ||||

| FS8530 | Fit for ASIL D | |||||

| FS6600 | Fit for ASIL D |

This platform facilitates the design of safe power management systems thanks to a portfolio of configurable and linkable devices. It simplifies complex power supply subsystems into a single smart solution.

| | | | | |

|---|---|---|---|---|---|

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

Quick reference to our documentation types.

5 documents

Compact List

There are no results for this selection.

Sign in to access authorized secure files. Learn more about secure access rights.

Please wait while your secure files are loading.

5 documents

Compact List

1 design file

Sign in to access authorized secure files. Learn more about secure access rights.

Please wait while your secure files are loading.

1 design file

2 hardware offerings

Sign in to access authorized secure files. Learn more about secure access rights.

1 hardware offering

To find additional partner offerings that support this product, visit our Partner Marketplace.

2 hardware offerings

Quick reference to our software types.

1 software file

Note: For better experience, software downloads are recommended on desktop.

Sign in to access authorized secure files. Learn more about secure access rights.

Please wait while your secure files are loading.

2 trainings

2 trainings

There are no recently viewed products to display.

Help us improve your experience on our site. We invite you to take our five-question survey.