Low-Ohmic Four-Pole Double-Throw Analog Switch

Sign in for a personalized NXP experience.

Click over video to play

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

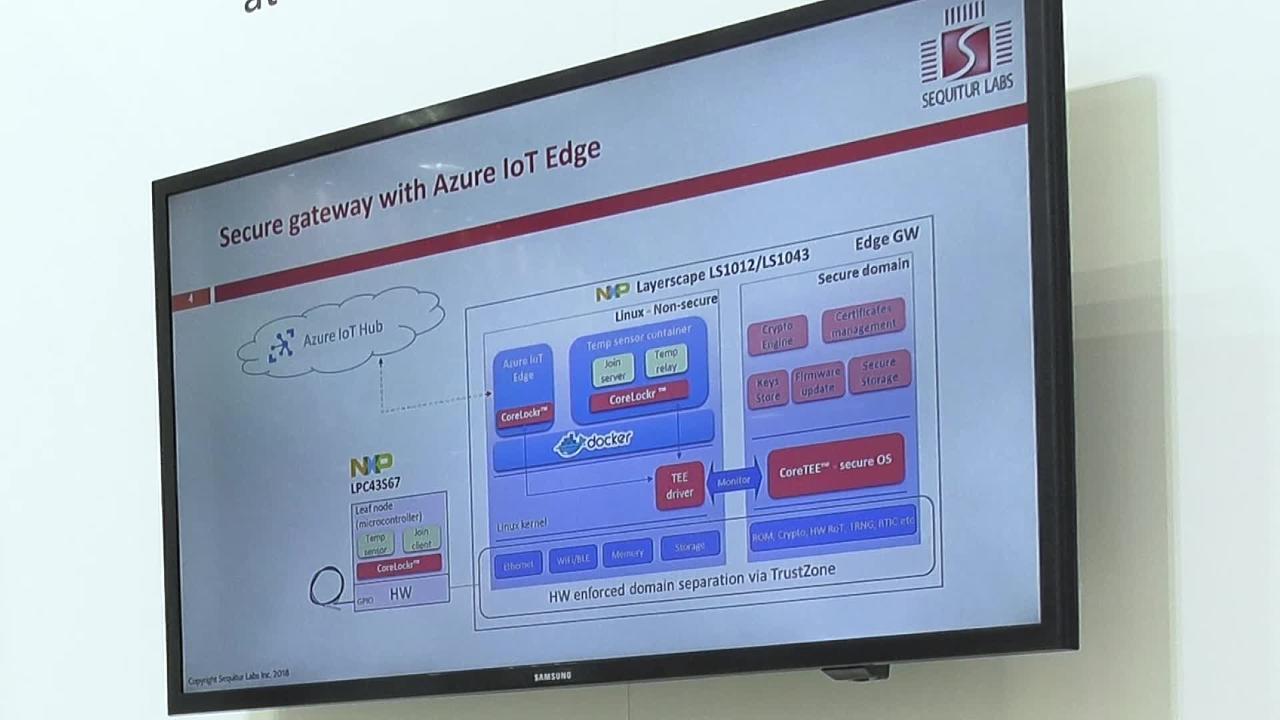

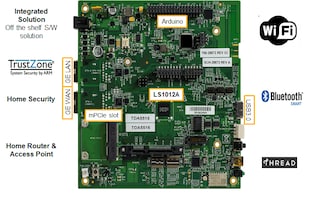

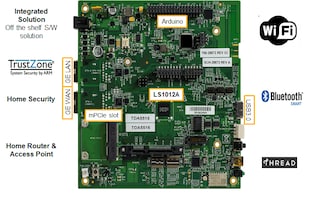

The LS1012A processor, optimized for battery-backed or USB-powered, space-constrained networking and IoT applications, integrates a single Arm® Cortex®-A53 core running up to 1GHz with a hardware packet forwarding engine and high-speed interfaces to deliver line-rate networking performance in an ultra-small size envelope at 1W typical power dissipation. The LS1012A incorporates the same Trust Architecture and software compatibility of higher-tier LS family devices, enabling scalable, secure applications that leverage a common 64-bit software platform.

Layerscape processors are part of NXP's EdgeVerse™ edge computing platform.

Are you working with NXP processors or microcontrollers?

Don’t spend your money solving issues that NXP has already solved.

With NXP’s Premium Support, you’re getting expert help and a contractually obligated agreement for high-quality technical assistance. Enjoy guaranteed response times and direct access to NXP engineers who have likely already solved the issues you are facing.

Benefits include:Click here to discover how Premium Support can optimize your next design.

Low-Ohmic Four-Pole Double-Throw Analog Switch

3.3 V, Two Differential Channel, 2-1 Multiplexer/Demultiplexer Switch

Bidirectional Voltage Level Translator for Open-Drain and Push-Pull Applications

16-Bit I²C-Bus and SMBus I/O Port with Interrupt

Bidirectional High-Side Power Switch for Charger and USB‑OTG Combined Applications

USB PD and Type-C Current-Limited Power Switch

1-10 of 12 results

Include 8 NRND

Part | Order | CAD Model | Silicon Rev | Family | Status | Development Tools | Qualification tier | Budgetary Price excluding tax | Package Termination Count | Package Type | Package Pitch (mm) | Core Type | Core: Number of cores (SPEC) | Operating Frequency [Max] (MHz) | Typical Power | Cache (KB) | L1 Cache (KB) | L2 Cache (Max) (KB) | SRAM (kB) | External Memory Supported | DRAM frequency (max)(MHz) | Serial Audio Interface (SAI) | I2S | SPI | QSPI | UART | I2C | USB Controllers | Ethernet Ports | Ethernet Type | PCIe | SATA | Encryption | Watchdog timer | Timers | Debug & Trace | Junction Temperature (Min to Max) (℃) |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

Rev 2 | QorIQ LS1012A | Active | LS1012A-RDB | Industrial | 1K @ US$13.22 | 211 | VFLGA211 | 0.5 | Arm Cortex-A53 | 1 | 600 | 1.14 | 32 | 32 | 256 | 128 | DDR3L SDRAM | 1000 | 5 | 5 | 1 | 1 | 2 | 2 | 2 | 2 | 100M, 10M, 1G, 2.5G | 1 | 1 x SATA 3.0 | Y | Y | 2 | JTAG | 0 to 105 | |||

Rev 2 | QorIQ LS1012A | Active | LS1012A-RDB | Industrial | 1K @ US$14.55 | 211 | VFLGA211 | 0.5 | Arm Cortex-A53 | 1 | 800 | 1.17 | 32 | 32 | 256 | 128 | DDR3L SDRAM | 1000 | 5 | 5 | 1 | 1 | 2 | 2 | 2 | 2 | 100M, 10M, 1G, 2.5G | 1 | 1 x SATA 3.0 | Y | Y | 2 | JTAG | 0 to 105 | |||

Rev 2 | QorIQ LS1012A | Active | LS1012A-RDB | Industrial | 1K @ US$16.01 | 211 | VFLGA211 | 0.5 | Arm Cortex-A53 | 1 | 1000 | 1.26 | 32 | 32 | 256 | 128 | DDR3L SDRAM | 1000 | 5 | 5 | 1 | 1 | 2 | 2 | 2 | 2 | 100M, 10M, 1G, 2.5G | 1 | 1 x SATA 3.0 | Y | Y | 2 | JTAG | 0 to 105 | |||

Rev 2 | QorIQ LS1012A | Active | LS1012A-RDB | Industrial | 1K @ US$12.60 | 211 | VFLGA211 | 0.5 | Arm Cortex-A53 | 1 | 600 | 1.14 | 32 | 32 | 256 | 128 | DDR3L SDRAM | 1000 | 5 | 5 | 1 | 1 | 2 | 2 | 2 | 2 | 100M, 10M, 1G, 2.5G | 1 | 1 x SATA 3.0 | N | Y | 2 | JTAG | 0 to 105 | |||

Rev 2 | QorIQ LS1012A | Active | LS1012A-RDB | Industrial | 1K @ US$13.87 | 211 | VFLGA211 | 0.5 | Arm Cortex-A53 | 1 | 800 | 1.17 | 32 | 32 | 256 | 128 | DDR3L SDRAM | 1000 | 5 | 5 | 1 | 1 | 2 | 2 | 2 | 2 | 100M, 10M, 1G, 2.5G | 1 | 1 x SATA 3.0 | N | Y | 2 | JTAG | 0 to 105 | |||

Rev 2 | QorIQ LS1012A | Active | LS1012A-RDB | Industrial | 1K @ US$15.24 | 211 | VFLGA211 | 0.5 | Arm Cortex-A53 | 1 | 1000 | 1.26 | 32 | 32 | 256 | 128 | DDR3L SDRAM | 1000 | 5 | 5 | 1 | 1 | 2 | 2 | 2 | 2 | 100M, 10M, 1G, 2.5G | 1 | 1 x SATA 3.0 | N | Y | 2 | JTAG | 0 to 105 | |||

Rev 2 | QorIQ LS1012A | Active | LS1012A-RDB | Industrial | 1K @ US$14.55 | 211 | VFLGA211 | 0.5 | Arm Cortex-A53 | 1 | 600 | 1.14 | 32 | 32 | 256 | 128 | DDR3L SDRAM | 1000 | 5 | 5 | 1 | 1 | 2 | 2 | 2 | 2 | 100M, 10M, 1G, 2.5G | 1 | 1 x SATA 3.0 | Y | Y | 2 | JTAG | -40 to 105 | |||

Rev 2 | QorIQ LS1012A | Active | LS1012A-RDB | Industrial | 1K @ US$16.01 | 211 | VFLGA211 | 0.5 | Arm Cortex-A53 | 1 | 800 | 1.17 | 32 | 32 | 256 | 128 | DDR3L SDRAM | 1000 | 5 | 5 | 1 | 1 | 2 | 2 | 2 | 2 | 100M, 10M, 1G, 2.5G | 1 | 1 x SATA 3.0 | Y | Y | 2 | JTAG | -40 to 105 | |||

Rev 2 | QorIQ LS1012A | Active | LS1012A-RDB | Industrial | 1K @ US$17.61 | 211 | VFLGA211 | 0.5 | Arm Cortex-A53 | 1 | 1000 | 1.26 | 32 | 32 | 256 | 128 | DDR3L SDRAM | 1000 | 5 | 5 | 1 | 1 | 2 | 2 | 2 | 2 | 100M, 10M, 1G, 2.5G | 1 | 1 x SATA 3.0 | Y | Y | 2 | JTAG | -40 to 105 | |||

Rev 2 | QorIQ LS1012A | Active | LS1012A-RDB | Industrial | 1K @ US$13.87 | 211 | VFLGA211 | 0.5 | Arm Cortex-A53 | 1 | 600 | 1.14 | 32 | 32 | 256 | 128 | DDR3L SDRAM | 1000 | 5 | 5 | 1 | 1 | 2 | 2 | 2 | 2 | 100M, 10M, 1G, 2.5G | 1 | 1 x SATA 3.0 | N | Y | 2 | JTAG | -40 to 105 |

Quick reference to our documentation types.

1-10 of 26 documents

Compact List

There are no results for this selection.

Sign in to access authorized secure files. Learn more about secure access rights.

Please wait while your secure files are loading.

1-10 of 26 documents

Compact List

Receive the full breakdown. See the product footprint and more in the eCad file.

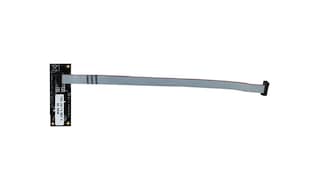

5 hardware offerings

Additional hardware available. View our featured partner solutions.

Sign in to access authorized secure files. Learn more about secure access rights.

1-5 of 10 hardware offerings

To find additional partner offerings that support this product, visit our Partner Marketplace.

5 hardware offerings

Additional hardware available. View our featured partner solutions.

Quick reference to our software types.

1-5 of 6 software files

Additional software available. View our featured partner solutions.

Note: For better experience, software downloads are recommended on desktop.

Sign in to access authorized secure files. Learn more about secure access rights.

Please wait while your secure files are loading.

1-5 of 28 software offerings

To find additional partner offerings that support this product, visit our Partner Marketplace.

1-5 of 6 software files

Additional software available. View our featured partner solutions.

Note: For better experience, software downloads are recommended on desktop.

1-5 of 23 engineering services

There are no results for this selection.

There are no results for this selection.

To find additional partner offerings that support this product, visit our Partner Marketplace.

4 trainings

Additional trainings are available. View our featured partner trainings.

4 trainings

Additional trainings are available. View our featured partner trainings.

5 trainings

To find additional partner offerings that support this product, visit our Partner Marketplace.

There are no recently viewed products to display.

Help us improve your experience on our site. We invite you to take our five-question survey.