USB PD and Type-C Current-Limited Power Switch

Sign in for a personalized NXP experience.

Click over video to play

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

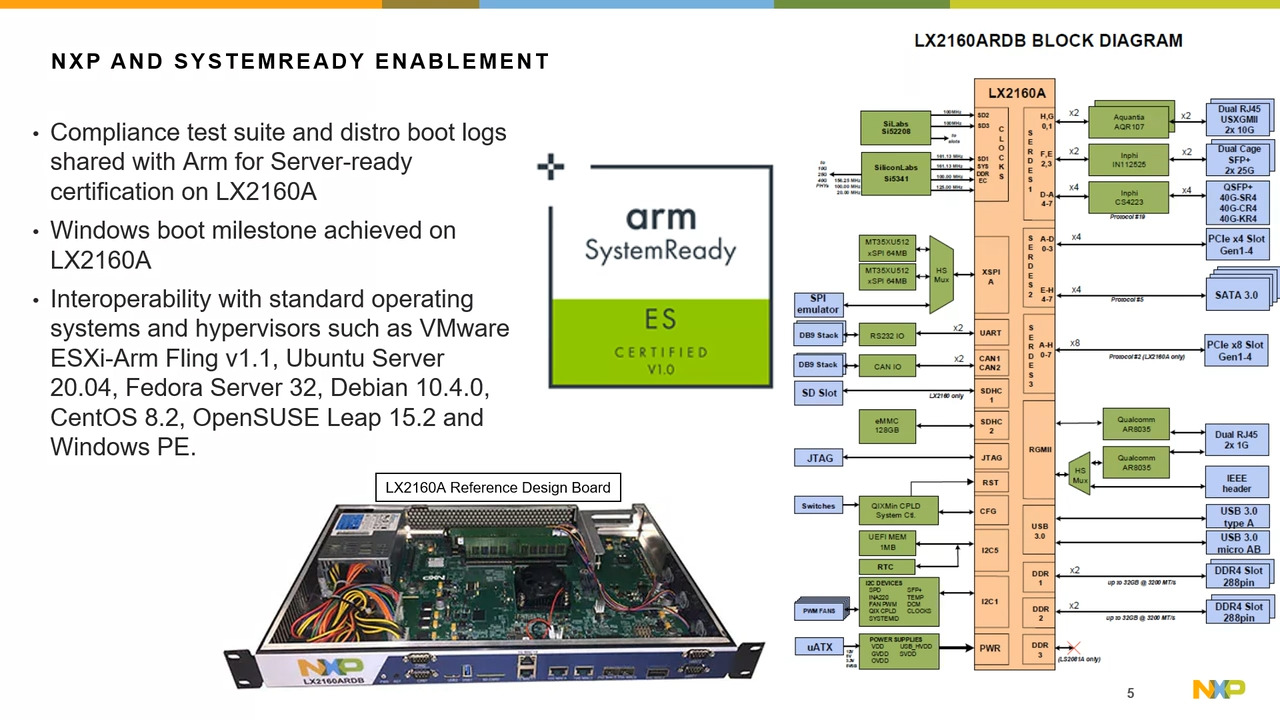

The LX2160A multicore processor, the highest-performance member of the Layerscape family, combines FinFET process technology's low power and sixteen Arm® Cortex®-A72 cores with datapath acceleration optimized for L2/3 packet processing, together with security offload, robust traffic management and quality of service.

This advanced sixteen-core 64-bit Arm processor is ideal for applications such as 5G packet processing, network function virtualization (NFV), white-box switching, high-processing industrial computers, machine learning and smart Network Interface Cards. The high level of integration delivers significant performance benefits such as 100 GbE, hardware L2 switching, DPAA2 with 100 Gbps decompression/compression and 50 Gbps SEC and multiple PCIe Gen3.0 and SATA controllers.

For Edge Computing, this processor offers outstanding computing performance with a powerful packet offload and Ethernet controllers. You can have high-end and high-speed communications in one device, with low-speed peripherals such as sensors and the computing power to process and act upon all received information.

Layerscape processors are part of NXP's EdgeVerse™ edge computing platform.

Note: To see the product features close this window.

| LX2160A | LX2120A | LX2080A | |

|---|---|---|---|

| Cores | 16 | 12 | 8 |

| L2 cache | 8MB | 6MB | 8MB |

| SerDes | 24 | ||

| PCIe | Up to 6x Gen3 | ||

| DDR | 2x DDR4, Up to 3200MT/s, 256GB capacity | ||

| Plat cache + PEB | 10MB | ||

| WRIOP | 16 simultaneous MACs; combos of up to 16x 1GE, 10x 1/2.5/10GE, 6x 25GE, or 2x 40/50/100GE; L2 switching up to 114Gbps | ||

| SEC | Up to 50Gbps | ||

| DCE | Up to 100Gbps | ||

| Package | 40 x 40 mm, 1517 pins | ||

USB PD and Type-C Current-Limited Power Switch

Layerscape® 2088A and 2048A Processors

1-10 of 60 results

Include 0 NRND

Part | Order | CAD Model | Silicon Rev | Family | Status | Development Tools | Qualification tier | Budgetary Price excluding tax | Package Termination Count | Package Type | Package Pitch (mm) | Core Type | Core: Number of cores (SPEC) | Operating Frequency [Max] (MHz) | Typical Power | Cache (KB) | L1 Cache (KB) | L2 Cache (Max) (KB) | SRAM (kB) | External Memory Supported | DRAM frequency (max)(MHz) | SPI | QSPI | UART | I2C | USB Controllers | CAN | Ethernet Ports | Ethernet Type | PCIe | PCIe version | SATA | Encryption | Watchdog timer | Timers | Debug & Trace | Junction Temperature (Min to Max) (℃) |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

Rev 2 | LX2160 family | Active | BLBX3-T2 | Automotive | 10K @ US$297.91 | 1517 | BGA1517 | 1.0 | Arm Cortex-A72 | 8 | 2200 | — | 32, 48 | 32, 48 | 8192 | 256 | DDR4 SDRAM | 3200 | 3 | 2 | 4 | 8 | 2 | 2 | 18 | 100G, 10G, 1G | 6 | PCIe 3.0 | 4 x SATA 3.0 | N | Y | 2 | JTAG | -40 to 105 | |||

Rev 2 | LX2160 family | Active | BLBX3-T2 | Automotive | 10K @ US$312.80 | 1517 | BGA1517 | 1.0 | Arm Cortex-A72 | 8 | 2200 | — | 32, 48 | 32, 48 | 8192 | 256 | DDR4 SDRAM | 3200 | 3 | 2 | 4 | 8 | 2 | 2 | 18 | 100G, 10G, 1G | 6 | PCIe 3.0 | 4 x SATA 3.0 | Y | Y | 2 | JTAG | -40 to 105 | |||

Rev 2 | LX2160 family | Active | LX2160A-RDB-B | Industrial | 100 @ US$279.82 | 1517 | BGA1517 | 1.0 | Arm Cortex-A72 | 8 | 1800 | 11 | 32, 48 | 32, 48 | 8192 | 256 | DDR4 SDRAM | 2600 | 3 | 2 | 4 | 8 | 2 | 2 | 18 | 100G, 10G, 1G, 25 Gbit/s | 6 | PCIe 3.0 | 4 x SATA 3.0 | Y | Y | 2 | JTAG | 0 to 105 | |||

Rev 2 | LX2160 family | Active | LX2160A-RDB-B | Industrial | 100 @ US$317.12 | 1517 | BGA1517 | 1.0 | Arm Cortex-A72 | 8 | 2000 | 15.7 | 32, 48 | 32, 48 | 8192 | 256 | DDR4 SDRAM | 2900 | 3 | 2 | 4 | 8 | 2 | 2 | 18 | 100G, 10G, 1G, 25 Gbit/s | 6 | PCIe 3.0 | 4 x SATA 3.0 | Y | Y | 2 | JTAG | 0 to 105 | |||

Rev 2 | LX2160 family | Active | LX2160A-RDB-B | Industrial | 100 @ US$373.10 | 1517 | BGA1517 | 1.0 | Arm Cortex-A72 | 8 | 2200 | 21.8 | 32, 48 | 32, 48 | 8192 | 256 | DDR4 SDRAM | 3200 | 3 | 2 | 4 | 8 | 2 | 2 | 18 | 100G, 10G, 1G, 25 Gbit/s | 6 | PCIe 3.0 | 4 x SATA 3.0 | Y | Y | 2 | JTAG | 0 to 105 | |||

Rev 2 | LX2160 family | Active | LX2160A-RDB-B | Industrial | 100 @ US$266.49 | 1517 | BGA1517 | 1.0 | Arm Cortex-A72 | 8 | 1800 | 11 | 32, 48 | 32, 48 | 8192 | 256 | DDR4 SDRAM | 2600 | 3 | 2 | 4 | 8 | 2 | 2 | 18 | 100G, 10G, 1G, 25 Gbit/s | 6 | PCIe 3.0 | 4 x SATA 3.0 | Y | Y | 2 | JTAG | 0 to 105 | |||

Rev 2 | LX2160 family | Active | LX2160A-RDB-B | Industrial | 100 @ US$302.03 | 1517 | BGA1517 | 1.0 | Arm Cortex-A72 | 8 | 2000 | 15.7 | 32, 48 | 32, 48 | 8192 | 256 | DDR4 SDRAM | 2900 | 3 | 2 | 4 | 8 | 2 | 2 | 18 | 100G, 10G, 1G, 25 Gbit/s | 6 | PCIe 3.0 | 4 x SATA 3.0 | Y | Y | 2 | JTAG | 0 to 105 | |||

Rev 2 | LX2160 family | Active | LX2160A-RDB-B | Industrial | 100 @ US$355.32 | 1517 | BGA1517 | 1.0 | Arm Cortex-A72 | 8 | 2200 | 21.8 | 32, 48 | 32, 48 | 8192 | 256 | DDR4 SDRAM | 3200 | 3 | 2 | 4 | 8 | 2 | 2 | 18 | 100G, 10G, 1G, 25 Gbit/s | 6 | PCIe 3.0 | 4 x SATA 3.0 | Y | Y | 2 | JTAG | 0 to 105 | |||

Rev 2 | LX2160 family | Active | LX2160A-RDB-B | Industrial | 100 @ US$253.17 | 1517 | BGA1517 | 1.0 | Arm Cortex-A72 | 8 | 1800 | 11 | 32, 48 | 32, 48 | 8192 | 256 | DDR4 SDRAM | 2600 | 3 | 2 | 4 | 8 | 2 | 2 | 18 | 100G, 10G, 1G, 25 Gbit/s | 6 | PCIe 3.0 | 4 x SATA 3.0 | N | Y | 2 | JTAG | 0 to 105 | |||

Rev 2 | LX2160 family | Active | LX2160A-RDB-B | Industrial | 100 @ US$286.93 | 1517 | BGA1517 | 1.0 | Arm Cortex-A72 | 8 | 2000 | 15.7 | 32, 48 | 32, 48 | 8192 | 256 | DDR4 SDRAM | 2900 | 3 | 2 | 4 | 8 | 2 | 2 | 18 | 100G, 10G, 1G, 25 Gbit/s | 6 | PCIe 3.0 | 4 x SATA 3.0 | N | Y | 2 | JTAG | 0 to 105 |

LX2160AQuick reference to our documentation types.

1-10 of 34 documents

Compact List

There are no results for this selection.

Sign in to access authorized secure files. Learn more about secure access rights.

Please wait while your secure files are loading.

1-10 of 34 documents

Compact List

Receive the full breakdown. See the product footprint and more in the eCad file.

1-5 of 6 hardware offerings

Additional hardware available. View our featured partner solutions.

Sign in to access authorized secure files. Learn more about secure access rights.

1-5 of 22 hardware offerings

To find additional partner offerings that support this product, visit our Partner Marketplace.

1-5 of 6 hardware offerings

Additional hardware available. View our featured partner solutions.

Quick reference to our software types.

1-5 of 6 software files

Additional software available. View our featured partner solutions.

Note: For better experience, software downloads are recommended on desktop.

Sign in to access authorized secure files. Learn more about secure access rights.

Please wait while your secure files are loading.

1-5 of 18 software offerings

To find additional partner offerings that support this product, visit our Partner Marketplace.

1-5 of 6 software files

Additional software available. View our featured partner solutions.

Note: For better experience, software downloads are recommended on desktop.

1-5 of 18 engineering services

There are no results for this selection.

There are no results for this selection.

To find additional partner offerings that support this product, visit our Partner Marketplace.

5 trainings

Additional trainings are available. View our featured partner trainings.

5 trainings

Additional trainings are available. View our featured partner trainings.

5 trainings

To find additional partner offerings that support this product, visit our Partner Marketplace.

There are no recently viewed products to display.

View or edit your browsing history

Help us improve your experience on our site. We invite you to take our five-question survey.