EdgeLock® Assurance

The TJA1153, part of the EdgeLock Assurance program, is designed to meet industry standards and follows NXP's security-by-design approach.

Sign in for a personalized NXP experience.

Roll over image to zoom in

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

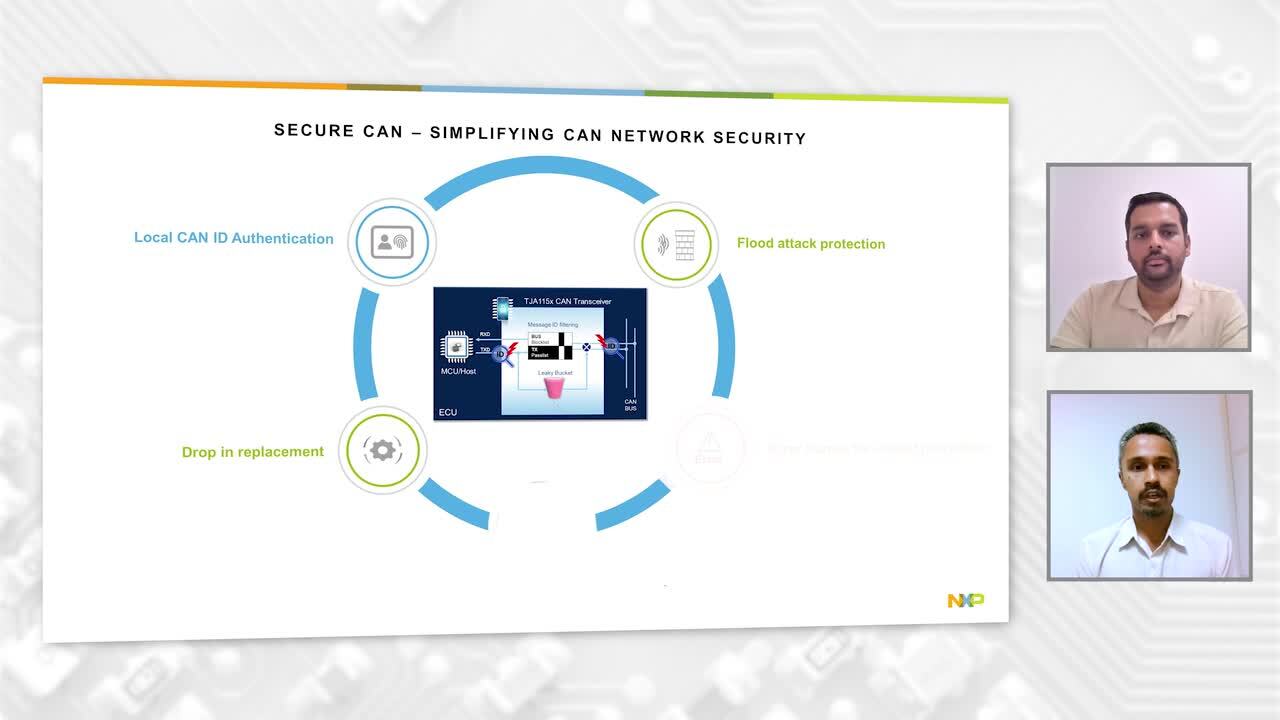

NXP's new secure CAN transceiver TJA1153A provides a seamless and very cost-effective solution for securing classical CAN and CAN FD communication without cryptography. The TJA1153A belongs to a new generation of automotive high-speed CAN/CAN FD transceivers, offering security functions. It provides an interface between a classical CAN or CAN FD protocol controller and the physical two-wire CAN bus. As long as no security incidents have been detected, the TJA1153A behaves like a standard CAN transceiver with Sleep mode.

The security incidents that can be detected and contained are:

Note: To see the product features close this window.

The TJA1153, part of the EdgeLock Assurance program, is designed to meet industry standards and follows NXP's security-by-design approach.

1 result

Include 0 NRND

Part | Order | CAD Model | Status | Package Type | Package Pitch (mm) | Recommended Orderable Part Number | MCU I/O Interface (V) | VIO Option Available | Low Power Modes | Data Rate [max] kbps | CAN Channels | Product Category | Supply Voltage [Min to Max] (V) | Data Rate [min] kbps | Voltage on bus pins [Min-Max] (V) | VESD IEC on bus pins (+/- kV) | VESD HBM on bus pins (+/- kV) | Junction Temperature (Max) (℃) | Protection | Wake-Up Pin | Min High Input Levels (V) [Vio] | Supported standards | SPLIT Pin | Thermal Resistance (Spec) (℃/W) | Product Application |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

Active | HVSON14 | 0.65 | TJA1153ATK/0Z | 3.3, 5.0 | Y | Sleep Mode, Standby Mode | 5000.0 | 1 | Secure CAN / High-Speed CAN / CAN FD | 4.75 to 5.25 | 40.0 | -58 to 58 | 0 to 0 | 0 to 0 | 150 | TXD dominant timeout, overtemperature, undervoltage | Y | 2.1 | ISO-11898-2:2016, SAE J2284-1, SAE J2284-2, SAE J2284-3, SAE J2284-4, SAE J2284-5 | N | 50 | Automotive, Industrial |

Quick reference to our documentation types.

3 documents

Compact List

There are no results for this selection.

Sign in to access authorized secure files. Learn more about secure access rights.

Please wait while your secure files are loading.

3 documents

Compact List

Receive the full breakdown. See the product footprint and more in the eCad file.

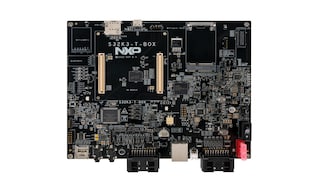

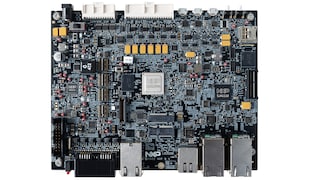

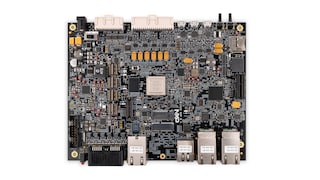

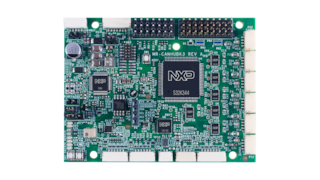

1-5 of 14 hardware offerings

Sign in to access authorized secure files. Learn more about secure access rights.

1-5 of 14 hardware offerings

Quick reference to our software types.

1 software offerings

To find additional partner offerings that support this product, visit our Partner Marketplace.

Sign in to access authorized secure files. Learn more about secure access rights.

Please wait while your secure files are loading.

1 software offerings

To find additional partner offerings that support this product, visit our Partner Marketplace.

There are no recently viewed products to display.

Help us improve your experience on our site. We invite you to take our five-question survey.