Product Longevity

Participating products are available for a minimum of 10 years. Designated participating products developed for the automotive, telecom and medical segments are available for a minimum of 15 years.

Sign in for a personalized NXP experience.

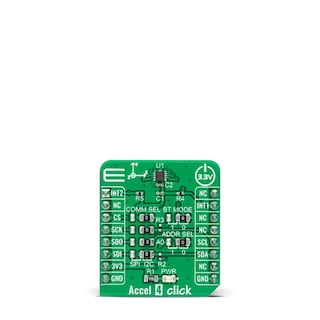

FXLS8964AF is a compact 3-axis accelerometer designed for applications requiring ultra-low power wake up on motion. With AEC-Q100 qualification and an extended temperature range, this device is an ideal choice for Automotive Key Fob application.

This smart sensor includes advanced digital features such as the SDCD block for inertial event detection, auto wake sleep, 32 sample FIFO/LIFO buffer and a single wire interface, ensuring overall power savings and simplified host data collection.

Sensor Development Toolbox is the complete ecosystem for product development with NXP’s motion and pressure sensors targeted toward IoT, Industrial, Medical applications. It encompasses a wide spectrum of sensor evaluation hardware and software tools making our sensors easy to use.

Participating products are available for a minimum of 10 years. Designated participating products developed for the automotive, telecom and medical segments are available for a minimum of 15 years.

±2g/±4g/±8g/±16g, Low Power 12-bit Digital Accelerometer

±2g/±4g/±8g/±16g, Low Power 12-bit Digital Accelerometer

±2g/±4g/±8g/±16g, Low-Power 12-Bit Digital IoT Accelerometer

| | | | | |

|---|---|---|---|---|---|

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

FXLS8964AFQuick reference to our documentation types.

4 documents

Compact List

There are no results for this selection.

Sign in to access authorized secure files. Learn more about secure access rights.

Please wait while your secure files are loading.

4 documents

Compact List

Receive the full breakdown. See the product footprint and more in the eCad file.

3 hardware offerings

Sign in to access authorized secure files. Learn more about secure access rights.

1 hardware offering

To find additional partner offerings that support this product, visit our Partner Marketplace.

3 hardware offerings

Quick reference to our software types.

1-5 of 6 software files

Note: For better experience, software downloads are recommended on desktop.

Sign in to access authorized secure files. Learn more about secure access rights.

Please wait while your secure files are loading.

1-5 of 6 software files

Note: For better experience, software downloads are recommended on desktop.

3 trainings

3 trainings

There are no recently viewed products to display.

View or edit your browsing history

Help us improve your experience on our site. We invite you to take our five-question survey.