Low-Ohmic Four-Pole Double-Throw Analog Switch

Sign in for a personalized NXP experience.

Click over video to play

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

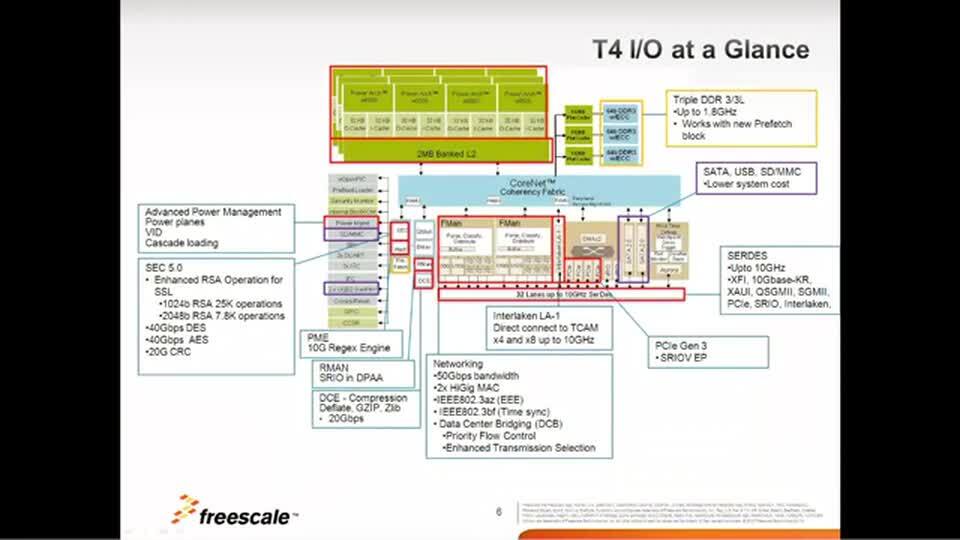

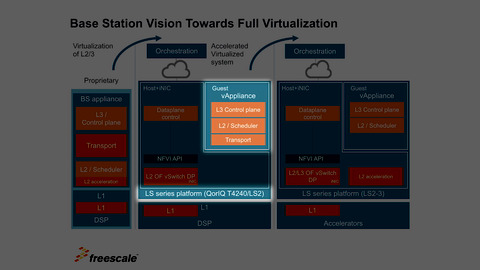

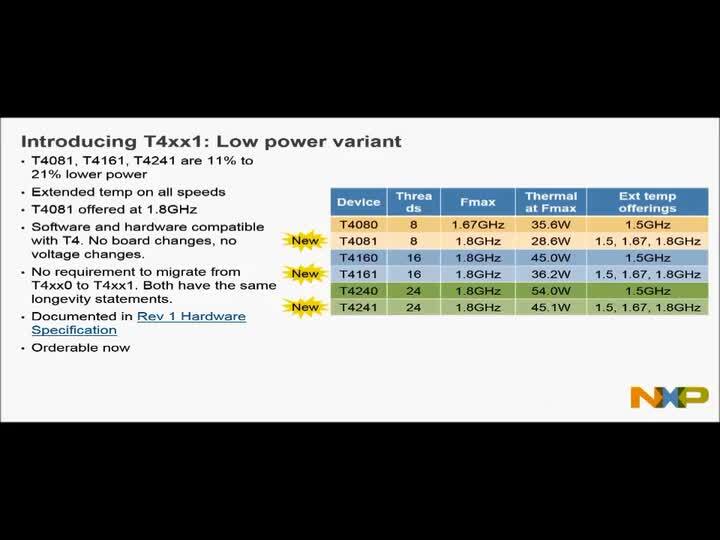

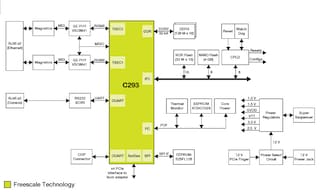

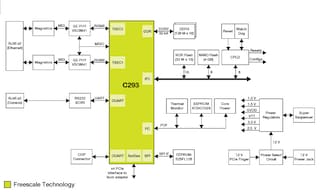

The T4240, with 24 virtual cores, is the flagship of the QorIQ® T series. With the T4160 (16 virtual cores) and T4080 (8 virtual cores), the T4 family has a 3x performance scaling factor within a pin-compatible package. Low-power variants are also available: T4241 (24 threads), T4161 (16 threads), and T4081 (8 threads).

With frequencies scaling to 1.8 GHz, integrated 1Gbps and 10Gpbs Ethernet, hardware acceleration and advanced system peripherals, these products target applications that benefit from consolidation of control and data plane processing in a single SoC, such as services cards, microservers, ADCs, WOCs, intelligent NICS, RNCs.

Note: To see the product features close this window.

| T4080 | T4081 | T4160 | T4161 | T4240 | T4241 | |

|---|---|---|---|---|---|---|

| Power Variant | Standard | Low | Standard | Low | Standard | Low |

| Cores (Dual Threaded) | 4 | 8 | 12 | |||

| L2 Cache | 2MB | 4MB | 6MB | |||

| CoreNet Platform Cache | 1MB | 1MB | 1.5MB | |||

| DDR Controllers | 2 | 2 | 3 | |||

| SerDes Lanes | 24 | 24 | 36 | |||

| Max 10Gbps Ethernet | 2 | 2 | 4 | |||

| Max 1Gbps Ethernet | 13 | 13 | 16 | |||

| PCIe ports | 3 | 3 | 4 | |||

| F104S8A | F104X8A | |

|---|---|---|

| Description | QSGMII PHY Standard Temperature | QSGMII PHY Extended Temperature |

| Operating Temperature (°C) | 0 - 125 | -40 - 125 |

| Package Type | 12x12, QFN, 138-pin, 0.65mm pin pitch | 12x12, QFN, 138-pin, 0.65mm pin pitch |

| Read More | Product Detail | |

Low-Ohmic Four-Pole Double-Throw Analog Switch

3.3 V, Two Differential Channel, 2-1 Multiplexer/Demultiplexer Switch

Bidirectional Voltage Level Translator for Open-Drain and Push-Pull Applications

16-Bit I²C-Bus and SMBus I/O Port with Interrupt

Dual-Supply Translating Transceiver (Auto-Direction Sensing, Three-State)

USB PD and Type-C Current-Limited Power Switch

Bidirectional High-Side Power Switch for Charger and USB‑OTG Combined Applications

Dual-Supply Translating Transceiver (Open-Drain, Auto-Direction Sensing)

| | | | | |

|---|---|---|---|---|---|

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

T4240Quick reference to our documentation types.

1-10 of 34 documents

Compact List

There are no results for this selection.

Please wait while your secure files are loading.

1-10 of 34 documents

Compact List

Receive the full breakdown. See the product footprint and more in the eCad file.

5 hardware offerings

Additional hardware available. View our featured partner solutions.

1-5 of 7 hardware offerings

.png?imwidth=300)

.png?imwidth=300)

To find additional partner offerings that support this product, visit our Partner Marketplace.

5 hardware offerings

Additional hardware available. View our featured partner solutions.

Quick reference to our software types.

5 software files

Additional software available. View our featured partner solutions.

Note: For better experience, software downloads are recommended on desktop.

Please wait while your secure files are loading.

1-5 of 16 software offerings

To find additional partner offerings that support this product, visit our Partner Marketplace.

5 software files

Additional software available. View our featured partner solutions.

Note: For better experience, software downloads are recommended on desktop.

1-5 of 15 engineering services

There are no results for this selection.

There are no results for this selection.

To find additional partner offerings that support this product, visit our Partner Marketplace.

2 trainings

2 trainings

4 trainings

To find additional partner offerings that support this product, visit our Partner Marketplace.

There are no recently viewed products to display.

View or edit your browsing history

Help us improve your experience on our site. We invite you to take our five-question survey.