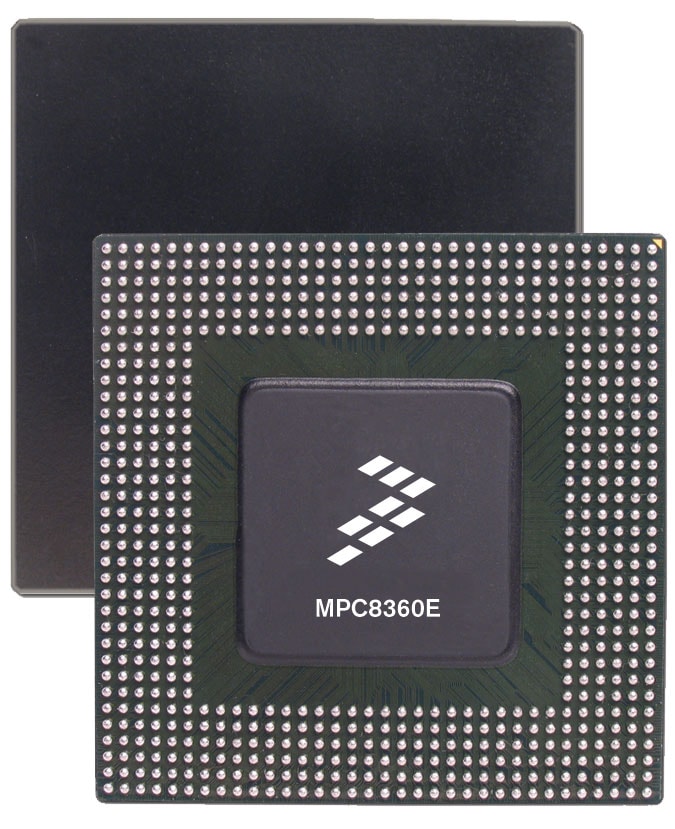

PowerQUICC® II Pro Processor with DDR2, Dual PCI, 1 GB Ethernet, Dual USB, Security

Sign in for a personalized NXP experience.

NXP® Semiconductors's MPC8360E PowerQUICC® II™ Pro family of integrated communications processors is a next-generation extension of the popular PowerQUICC II line containing cores built on Power Architecture technology. The MPC8360E family incorporates a next-generation communications engine, the QUICC™ Engine, supporting a wide range of protocols, including Gigabit Ethernet and OC-12 asynchronous transfer mode (ATM)/Packet over Sonet (POS). Additional enhancements include the e300 core (enhanced version of the 603e™ core with larger caches), scaling up to 667 MHz, a DDR memory controller and the integrated security engine.

The MPC8360E PowerQUICC II Pro communications processor's advanced features make it suitable for today's and tomorrow's wired and wireless access equipment, as well as small and medium enterprise networking equipment. Target applications include multitenant units (MTUs), digital subscriber line access multiplexers (DSLAMs), wireless basestations, multi and fixed subscriber access nodes, add/drop multiplexers and routers.

The MPC8358E processor, a member of the MPC8360E PowerQUICC II Pro family, is pin-compatible with the MPC8360E (TBGA only). The MPC8358E offers a cost-effective, low-power processing solution that meets the performance requirements for broadband access applications, such as small-to-medium enterprise (SME) routers, low-end DSLAMs and IP private automatic branch exchange (PABX) systems.

| MPC8358E | MPC8360E | |

|---|---|---|

| CPU | e300 | e300 |

| I-Cache/D-Cache (KB) | 32/32 | 32/32 |

| Available clock frequencies | Up to 400 MHz | Up to 667 MHz |

| QUICC Engine | 2 x RISC core | 2 x RISC core |

| Available clock frequencies | Up to 400 MHz | Up to 500 MHz |

| Ethernet | Up to 2 x 10/100/1,000 Up to 6 x 10/100 |

Up to 2 x 10/100/1,000 Up to 8x 10/100 |

| ATM | 1 x UTOPIA L2 | 2 x UTOPIA L2 |

| MPHY | Single 31/128 port | 128 per UTOPIA port |

| POS | Yes | Yes |

| TDM | Up to 4 TDM interfaces (QMC) Up to 256 channels at 16 Mbps on a single interface Up to four clear channel T3/E3 |

Up to 8 TDM interfaces (MCC) Up to 256 channels at 16 Mbps on a single interface Up to eight clear channel T3/E3 |

| Memory controller | 1 x 32/64-bit DDR | 1 x 32/64-bit or 2 x 32-bit DDR |

| Local bus | Yes | Yes |

| PCI | One 32-bit (up to 66 MHz) | One 32-bit (up to 66 MHz) |

| Integrated security engine* | Yes | Yes |

| DUART | Yes | Yes |

| I 2C controller | 2 | 2 |

| SPI | 2 | 2 |

| USB | Yes | Yes |

| Interrupt controller | Yes | Yes |

| Package options | 740 TBGA 668 PBGA |

740 TBGA |

Are you working with NXP processors or microcontrollers?

Don’t spend your money solving issues that NXP has already solved.

With NXP’s Premium Support, you’re getting expert help and a contractually obligated agreement for high-quality technical assistance. Enjoy guaranteed response times and direct access to NXP engineers who have likely already solved the issues you are facing.

Benefits include:Click here to discover how Premium Support can optimize your next design.

| | | | | |

|---|---|---|---|---|---|

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

Quick reference to our documentation types

1-10 of 56 documents

Compact List

There are no results for this selection.

Please wait while your secure files are loading.

1-10 of 56 documents

Compact List

1 design file

Please wait while your secure files are loading.

1 design file

2 hardware offerings

3 hardware offerings

To find additional partner offerings that support this product, visit our Partner Marketplace.

2 hardware offerings

Quick reference to our software types.

1-5 of 6 software files

Additional software available. View our featured partner solutions.

Note: For better experience, software downloads are recommended on desktop.

Please wait while your secure files are loading.

1-5 of 15 software offerings

To find additional partner offerings that support this product, visit our Partner Marketplace.

1-5 of 6 software files

Additional software available. View our featured partner solutions.

Note: For better experience, software downloads are recommended on desktop.

1-5 of 11 engineering services

There are no results for this selection.

There are no results for this selection.

To find additional partner offerings that support this product, visit our Partner Marketplace.

1-5 of 8 trainings

To find additional partner offerings that support this product, visit our Partner Marketplace.

8 trainings

To find additional partner offerings that support this product, visit our Partner Marketplace.

There are no recently viewed products to display.

Help us improve your experience on our site. We invite you to take our five-question survey.