Application Note (6)

Data Sheet (1)

Fact Sheet (2)

-

QorIQ® Qonverge® BSC9131 - Fact Sheet[QORIQPSC9131FS]Featured

Sign in for a personalized NXP experience.

Click over video to play

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

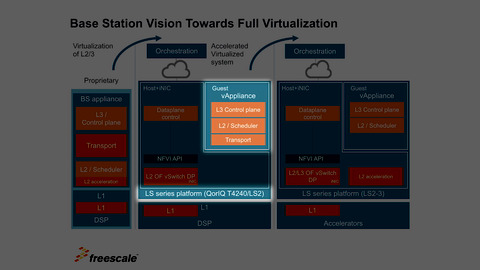

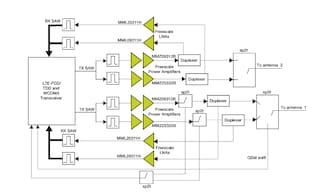

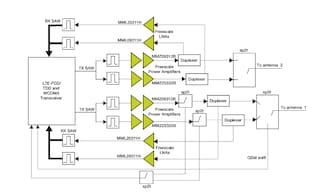

The QorIQ® Qonverge BSC9131 processor is a highly integrated device targeting small cell base station, enterprise VoIP, smart grid control, military/defense and industrial applications.

The BSC9131 device combines Power e500 and StarCore® SC3850 core technologies with MAPLE-B2F specialist DSP acceleration processing, addressing the need for a high-performance, low-cost, integrated solution, that handles a broad range of specialist DSP functions with complimentary high-performance general purpose processing.

Note: To see the product features close this window.

Are you working with NXP processors or microcontrollers?

Don’t spend your money solving issues that NXP has already solved.

With NXP’s Premium Support, you’re getting expert help and a contractually obligated agreement for high-quality technical assistance. Enjoy guaranteed response times and direct access to NXP engineers who have likely already solved the issues you are facing.

Benefits include:Click here to discover how Premium Support can optimize your next design.

1-10 of 12 results

Exclude 12 NRND

Part | CAD Model | Status | Package Termination Count | Package Type | Core Type | Core: Number of cores (SPEC) | Operating Frequency [Max] (MHz) | L2 Cache (Max) (KB) | Ethernet Type | Ambient Operating Temperature (Min to Max) (℃) |

|---|---|---|---|---|---|---|---|---|---|---|

End of Life | 520 | FBGA520 | SC3850, e500 | 1 | 800 | 256 | 1GBaseT, SGMII | -40 to 105 | ||

End of Life | 520 | FBGA520 | — | — | — | — | — | — | ||

End of Life | 520 | FBGA520 | SC3850, e500 | 1 | 800 | 256 | 1GBaseT, SGMII | -40 to 105 | ||

End of Life | 520 | FBGA520 | SC3850, e500 | 1 | 800 | 256 | 1GBaseT, SGMII | 0 to 105 | ||

End of Life | 520 | FBGA520 | — | — | — | — | — | — | ||

End of Life | 520 | FBGA520 | SC3850, e500 | 1 | 1000 | 256 | 1GBaseT, SGMII | 0 to 105 | ||

End of Life | 520 | FBGA520 | SC3850, e500 | 1 | 1000 | 256 | 1GBaseT, SGMII | 0 to 105 | ||

End of Life | 520 | FBGA520 | — | — | — | — | — | — | ||

End of Life | 520 | FBGA520 | SC3850, e500 | 1 | 1000 | 256 | 1GBaseT, SGMII | -40 to 105 | ||

End of Life | 520 | FBGA520 | — | — | — | — | — | — |

Quick reference to our documentation types

1-10 of 19 documents

Compact List

There are no results for this selection.

Sign in to access authorized secure files. Learn more about secure access rights.

Please wait while your secure files are loading.

1-10 of 19 documents

Compact List

Receive the full breakdown. See the product footprint and more in the eCad file.

5 hardware offerings

Additional hardware available. View our featured partner solutions.

Sign in to access authorized secure files. Learn more about secure access rights.

1-5 of 9 hardware offerings

.png?imwidth=300)

.png?imwidth=300)

To find additional partner offerings that support this product, visit our Partner Marketplace.

5 hardware offerings

Additional hardware available. View our featured partner solutions.

Quick reference to our software types.

2 software files

Note: For better experience, software downloads are recommended on desktop.

Sign in to access authorized secure files. Learn more about secure access rights.

Please wait while your secure files are loading.

1-5 of 11 software offerings

To find additional partner offerings that support this product, visit our Partner Marketplace.

2 software files

Note: For better experience, software downloads are recommended on desktop.

1-5 of 11 engineering services

There are no results for this selection.

There are no results for this selection.

To find additional partner offerings that support this product, visit our Partner Marketplace.

1 training

1 trainings

1 trainings

To find additional partner offerings that support this product, visit our Partner Marketplace.

There are no recently viewed products to display.

Help us improve your experience on our site. We invite you to take our five-question survey.