Design Files

Receive the full breakdown. See the product footprint and more in the eCad file.

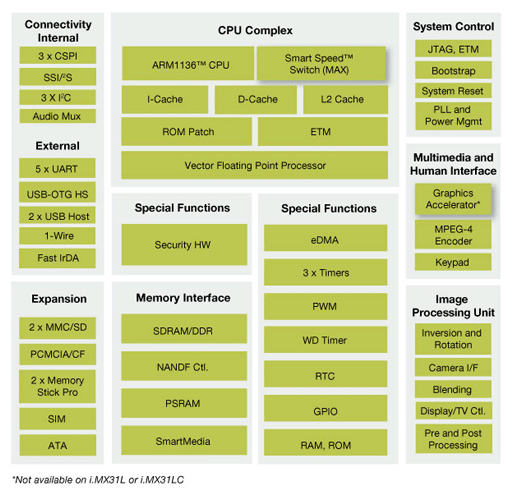

Millions of i.MX31 processors are powering consumer, industrial, automotive, medical and general embedded devices. With on-chip media accelerators, multiple connectivity interfaces and package options, the i.MX31 and i.MX31L are suitable for a broad spectrum of multimedia oriented applications. As the first in the i.MX portfolio to achieve automotive AEC-Q100 grade 3 qualification, the i.MX31 processor is the engine in the acclaimed Ford SYNC. Design engineers need choices; NXP® delivers.

Note: To see the product features close this window.

|

|

|

|

|

|

|

|---|---|---|---|---|---|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Quick reference to our documentation types.

1-5 of 45 documents

Please wait while your secure files are loading.

Receive the full breakdown. See the product footprint and more in the eCad file.

Receive the full breakdown. See the product footprint and more in the eCad file.

Quick reference to our software types.

1-5 of 13 software offerings

.svg?imwidth=300)

Please wait while your secure files are loading.

1-5 of 13 software offerings

.svg?imwidth=300)

To find additional partner offerings that support this product, visit our Partner Marketplace.

1-5 of 36 engineering services

There are no results for this selection.

To find additional partner offerings that support this product, visit our Partner Marketplace.

3 trainings

1-5 of 8 trainings

To find additional partner offerings that support this product, visit our Partner Marketplace.