QorIQ® P4080/P4040/P4081 Multicore Communications Processors

Sign in for a personalized NXP experience.

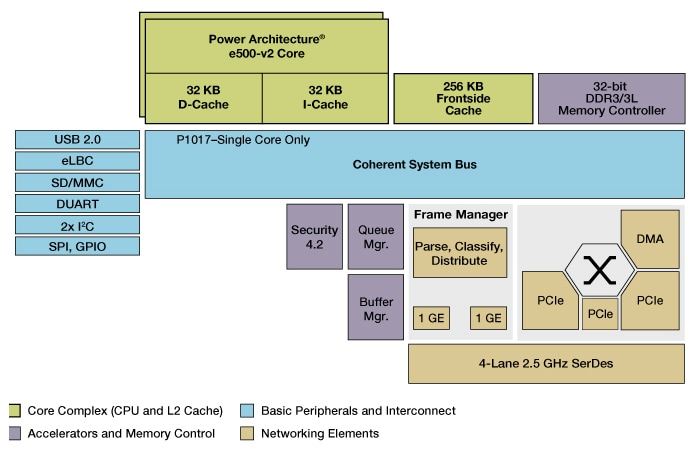

The P1023 and P1017 processors offer the value of integrated high-performance data path offload for networking protocols and dual e500 Power Architecture® cores for application software. The P1023 and P1017 are ideally suited for high-performance enterprise WLAN, fixed routers and security gateway applications. The P1023 device supports a 400–800 MHz performance range, along with advanced security and a rich set of interfaces—all delivered on 45 nm technology for low-power implementation.

The P1023 processor includes a performance-optimized implementation of the QorIQ® data path acceleration architecture (DPAA). This architecture provides the infrastructure to support simplified sharing of networking interfaces and accelerators by multiple CPU cores. The DPAA significantly reduces software overhead associated with high touch packet forwarding operations. Examples of the types of packet processing services this architecture is optimized to support include traditional routing and bridging, firewall, VPN termination for IPsec and MACsec (a standardized form of Ethernet encapsulation that can be used to provide confidentiality).

Note: To see the product features close this window.

| | | | | |

|---|---|---|---|---|---|

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

P1023Quick reference to our documentation types.

1-10 of 37 documents

Compact List

There are no results for this selection.

Please wait while your secure files are loading.

1-10 of 37 documents

Compact List

Receive the full breakdown. See the product footprint and more in the eCad file.

Quick reference to our software types.

3 software files

Note: For better experience, software downloads are recommended on desktop.

Please wait while your secure files are loading.

3 software files

Note: For better experience, software downloads are recommended on desktop.

1 training

1 trainings

There are no recently viewed products to display.

View or edit your browsing history

Help us improve your experience on our site. We invite you to take our five-question survey.