QorIQ® P2040/P2041 Multicore Communications Processors with Data Path

Sign in for a personalized NXP experience.

Click over video to play

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

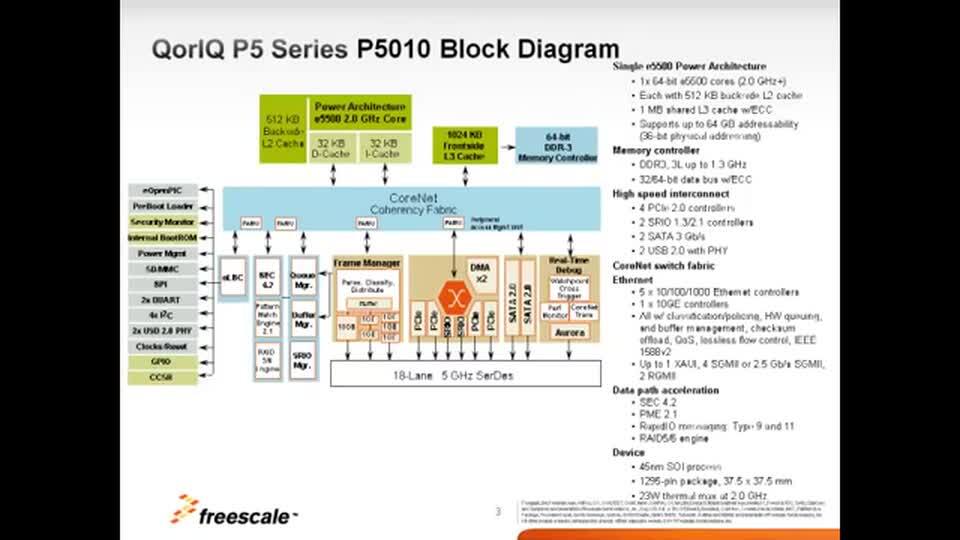

The dual-core P5020 and single-core P5010 processors deliver 64-bit processing, based on the e5500 core built on Power Architecture® technology. With frequencies scalable to 2.0 GHz, large caches and high per-cycle efficiency, these products target control plane and computer applications that require high single-threaded performance.

The P5 platform leverages architectural features pioneered in the P4 platform, including the three-level cache hierarchy for low latencies, hardware hypervisor for robust virtualization support, data path acceleration architecture (DPAA) for offloading packet handling tasks from the core and the CoreNet® switch fabric that eliminates internal bottlenecks. This enables architectural compatibility from the P5 platform to the P4 platform as well as to the P3 platform.

Note: To see the product features close this window.

| P5020 | P5010 | |

|---|---|---|

| Cores | 2 | 1 |

| Core Frequency | 1.6 to 2.0 GHz | 1.6 to 2.0 GHz |

| L2 Cache | 512 KB | 512 KB |

| L3/Platform Cache | 2 MB | 1 MB |

| DDR3 | 2x 64-bit | 1x 64-bit |

| GbE | 5x 1 GbE 1x 10 GbE | 5x 1 GbE 1x 10 GbE |

| SERDES | 18 Lanes | 18 Lanes |

| Security | Trust | Trust |

| | | | | |

|---|---|---|---|---|---|

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

P5020Quick reference to our documentation types.

1-10 of 39 documents

Compact List

There are no results for this selection.

Please wait while your secure files are loading.

1-10 of 39 documents

Compact List

Receive the full breakdown. See the product footprint and more in the eCad file.

Quick reference to our software types.

4 software files

Note: For better experience, software downloads are recommended on desktop.

Please wait while your secure files are loading.

4 software files

Note: For better experience, software downloads are recommended on desktop.

1 training

1 trainings

There are no recently viewed products to display.

View or edit your browsing history

Help us improve your experience on our site. We invite you to take our five-question survey.