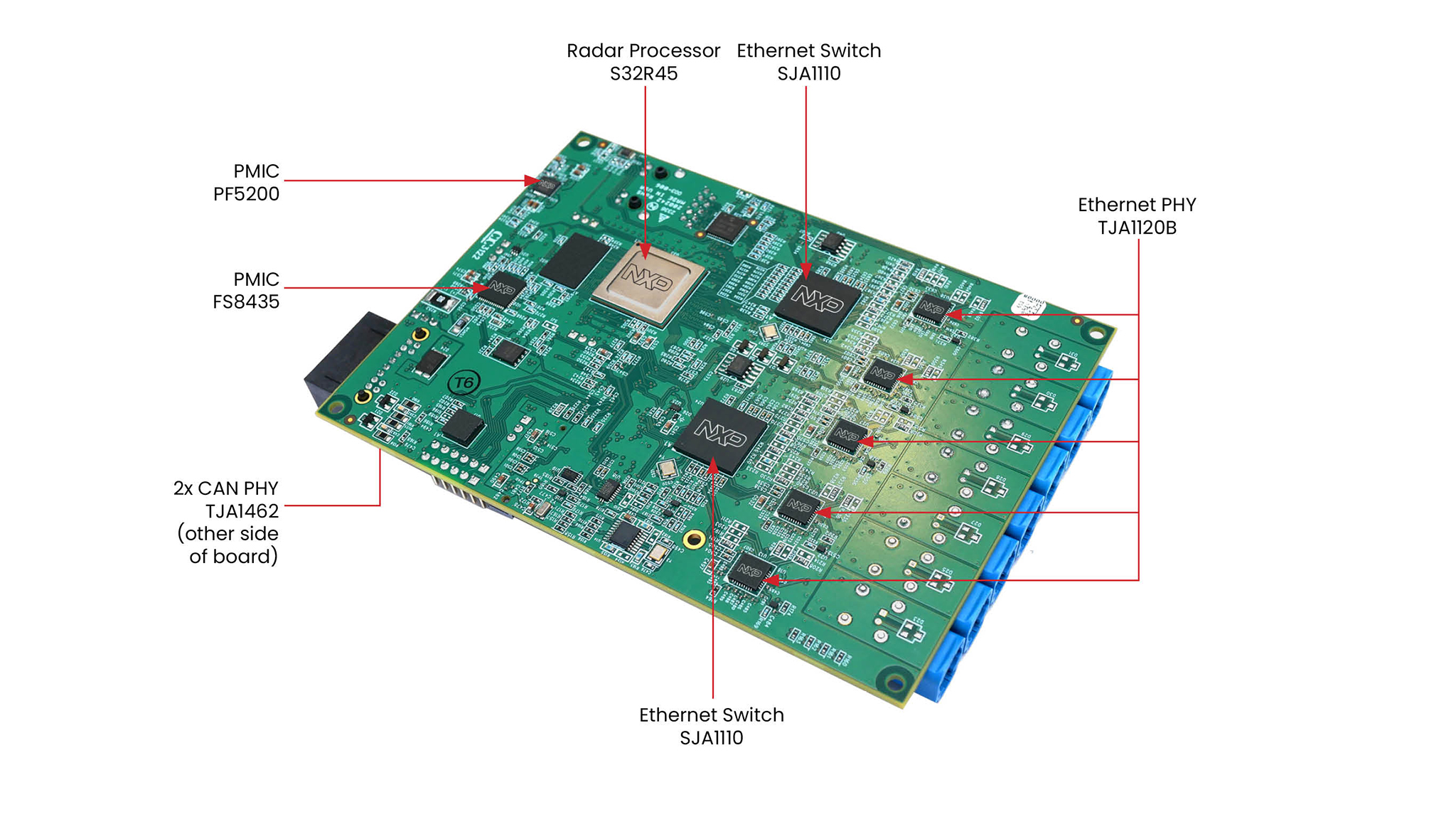

PurpleBox Reference Design for Distributed Radar Architectures

The PurpleBox is a reference design for distributed radar sensor architectures designed to aggregate and process four corner radar sensors at once, receiving compressed Range FFT data and producing a high-density surround point cloud. The PurpleBox can be used as a reference ECU and is a key component of a radar bridge proof-of-concept based on NXPs S32R45 radar processor. It comes with a comprehensive software development environment as well as with a M.2 PCIe interface which can be used to attach a mass storage device or a Hailo-8 machine learning accelerator.

To evaluate a distributed radar architecture, our Pluto radar sensor together with the PurpleBox can be used. The Pluto Radar sensor reference design enables customers to evaluate corner and front radar applications.

The PurpleBox reference design is available for selected customers with an approved NDA. For additional information, contact support or your local sales representative.

Product Details

Supported Devices

Processors and Microcontrollers

S32R Radar MCUs

- S32R45: S32R45 High-Performance Processor for Imaging Radar

Interfaces

Automotive Ethernet PHYs

- TJA1120: TJA1120, ASIL B Compliant Automotive Ethernet 1000BASE-T1 PHY Transceiver

Automotive Ethernet Switches and Network Controllers

- SJA1110: Multi-Gig Safe and Secure TSN Ethernet Switch with Integrated 100BASE-T1 PHYs

CAN Signal Improvement

- TJA1462: CAN Signal Improvement Capability Transceiver with Standby Mode

Features

Processing Power

- Aggregation and central processing of four corner radar sensors at once

- Produces a high-density surrounding point cloud

- Optional AI acceleration up to 26 tera-operations per second (TOPS) enabling enhanced point clouds

- Optional NVMe storage facilities for data gathering and playback

- Full example Radar processing chain:

- Range, Doppler

- DDMA

- Coherent/non-coherent combining

- OS CFAR

- Accelerated DoA algorithms such as iterative adaptive approach (IAA)

- ISO 26262 support by using safety components and architecture

Software Development Environment

- NXP radar software development kit

Design Resources

Software

Quick reference to our software types.

2 software files

-

Software Development Resources

PurpleBox Linux BSP

-

Software Development Resources

PurpleBox Radar Bridge Demo Application

Note: For better experience, software downloads are recommended on desktop.