USB 2.0 FULL HIGH SPEED SOLUTIONS

Applications for the USB Full-speed solutions include:

- Mice, keyboards

- Low-speed printers

- Microphones

- Game controllers

- Industrial equipment control

Applications for the USB High-speed solutions include:

- Mass storage devices, including flash drives

- Printers

- Scanners

- Video adapters

- Cell phones

- Tablets

- Wireless adapters

USB 2.0 Full-Speed Device Controller

The USB 2.0 Full-Speed Device Controller is a highly configurable, synthesizable USB core built from silicon-proven technology from NXP Semiconductors.

The core is an low gate count design that provides an efficient USB implementation in cost-sensitive applications.

It integrates with standard USB transceivers on USB side and AMBA® AHB interfaces on the system side, supporting all major embedded microprocessor cores.

Features

- Compliant to the USB 2.0 specification

- Supports Full-Speed (12 Mbps) operation

- DMA engine with connection to AHB interface

- Low gate count (7K gates)

- Various low power features including LPM support

- Up to 14 non-control logical endpoints

- Bulk, Interrupt, or Isochronous endpoint types

- Maximum packet size 0-1023

- Software-controlled interrupt structure

- Supports single-port RAM for endpoint buffers

- USB buffers can be programmed at the packet or transfer level

- Supported by 3rd-party software (drivers, and so on)

- AMBA® AHB-compliant system interfaces

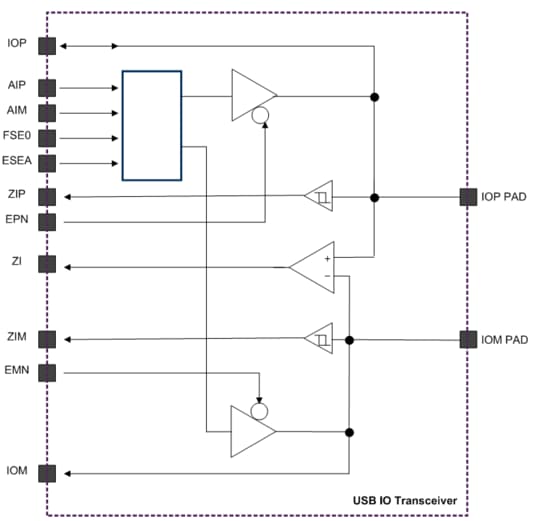

USB 2.0 I/O Transceiver

The USB IO transceiver is a CMOS IO cell available in TSMC 90LP and 65LP processes. It is compliant with the USB specification, Revision 2.0 (Full-Speed and Low-Speed, April 27, 2000).

The cell transceiver converts logic CMOS signals to USB compatible output signals and vice-versa. The transceiver supports two modes of data transfer rate; Low-Speed mode (1.5 Mbps) and Full-Speed mode (12 Mbps). In both the modes, the amplitude of output signal level is equal to the external supply voltage.

The receiver can detect differential signals as small as 0.2V (0.8V < CMR < 2.5V). This gives good noise margin that helps in building a robust communication system. Apart from the differential receiver, the cell also contains two single-ended receivers, one for each of the two data lines

Features

- Supports 12-Mbps (Full-Speed) and 1.5-Mbps (Low-Speed) serial data transmission

- Converts logic CMOS signals to USB compatible output signals and vice-versa

- Usable for downstream port of Host, upstream/downstream port of Hub and upstream port of Device

- Individual enable signals for D+ and D– outputs to enable separate control of these two paths for UART mode with same data rates as the USB

- Supports single-ended data interface

- Programmable differential or single-ended core input with forced single-ended low

- IDDQ testable in Suspend mode

- Internal programmable pull-up resistor on D+ data line

- Internal switchable pull-down resistor on both D+ and D– data lines

- No power sequence requirements

- D+ and D– are high-impedance when core is powered down and IO is powered up

- Small area (0.04mm2 in 90nm)

USB 2.0 High-Speed Device Controller

The USB 2.0 High-Speed Device Controller is a highly configurable, synthesizable USB core built from silicon-proven technology from NXP Semiconductors.

The core is an extremely low gate count design that provides an efficient USB implementation in cost-sensitive applications.

It integrates with standard UTMI-compliant PHYs or USB ULPI transceivers on USB side and AMBA® AHB interfaces on the system side, supporting all major embedded microprocessor cores.

Features:

- Compliant to the USB 2.0 specification

- Supports High-Speed (480 Mbps) and Full-Speed (12 Mbps) operation

- DMA engine with connection to AHB interface

- Low gate count (20K gates)

- Various low power features

- Up to 14 non-control logical endpoints

- Bulk, Interrupt, or Isochronous endpoint types

- Maximum packet size 0-1023

- Software-controlled interrupt structure

- Supports single-port RAM for endpoint buffers

- USB buffers can be programmed at the packet or transfer level

- Supported by 3rd-party software (drivers, and so on)

- Independent AMBA® AHB-compliant system interfaces

USB 2.0 High-Speed Host and Device Controller

The USB 2.0 High-Speed Host and Device Controller is a highly configurable, synthesizable USB core built from silicon-proven technology from NXP Semiconductors.

The core is an extremely low gate count design that provides an efficient USB implementation in cost-sensitive applications.

It integrates with standard UTMI-compliant PHYs or USB ULPI transceivers on USB side and AMBA® AHB interfaces on the system side, supporting all major embedded microprocessor cores.

Features:

- Compliant to the USB 2.0 specification

- Supports High-Speed (480 Mbps), Full-Speed (12 Mbps), and Low-Speed (Host-only, 1.5 Mbps) operation

- Host and Device functions can switch under software control

- Host is OCHI-compliant

- Two ports available as Host

- DMA engine with connection to AHB interface

- Low gate count (43K gates)

- Various low power features

- Up to 14 non-control logical endpoints

- Bulk, Interrupt, or Isochronous endpoint types

- Maximum packet size 0-1023

- Software-controlled interrupt structure

- Supports single-port RAM for endpoint buffers

- USB buffers can be programmed at the packet or transfer level

- Supported by 3rd-party software (drivers, and so on)

- Independent AMBA® AHB-compliant system interface with separate interfaces for Host and Device functions

USB 2.0 PHY

Features:

- Fully USB 1.1 (FS and LS) and USB 2.0 (HS) compliant

- Integrated 1.5 kΩ pull-up resistor on dp and 45Ω and 15kΩ pull-down termination resistors on dp and dm as defined in USB 2.0

- Option for use of external 1.5 kΩ pull-up resistor on dp and 15kΩ pull-down termination resistors on dp and dm

- 8 or 16-bit parallel word UTMI+ compliant interface

- UTMI+ v1.0 level3

- UTMI+ On-the-Go features including

- Mini-A or mini-B detect

- Vbus comparators

- 60-MHz (8-bit interface) or 30-MHz (16-bit interface) clock out

- 480-MHz clock in

- Resetable dividers to align output clocks of multiple transceivers

- High, Full, and Low-Speed disconnect detection

- Low current consumption in functional mode

- Low current consumption in suspend mode

- Small area (0.9mm2 in 90nm)

Partner Silvaco takes care of the distribution of USB IP. Silvaco is a leading EDA provider of Software tools, used in analog/mixed-signal, power IC and memory design.

Headquartered in Santa Clara, California, Silvaco has a global presence with offices located in North America, Europe, Japan and Asia for over 30 years and is offering fast-turnaround and affordable services for TCAD, SPICE Modeling, and PDK development. In June 2016 Silvaco acquired Semiconductor IP blocks vendor IPextreme, now the IP department of Silvaco (under IPextreme brand)

The USB IP is owned by NXP, but packaged, sold, and supported through Silvaco

Deliverables

| Deliverables |

| VHDL RTL source code (Verilog on request) |

| Test bench with test suites |

| Documentation including User’s Guide and Integration guide |

| Technology independent synthesis constraints |

| Where applicable |

| Behavioural models |

| Front-end and back-end views |