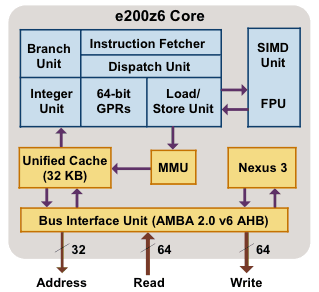

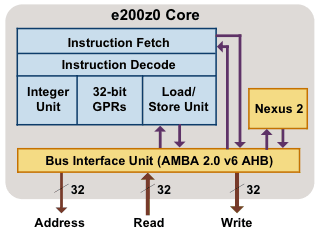

NXP’s e200 family of synthesizable, high-efficiency cores is intended for cost-sensitive, embedded real-time applications with significant performance requirements. The four e200 cores —e200z0, e200z1, e200z3, and e200z6—provide a range of features ideal for automotive, avionics, robotics, industrial control, medical devices, and compact networking applications.