Design Files

Receive the full breakdown. See the product footprint and more in the eCad file.

Sign in for a personalized NXP experience.

P1021 and P1012 devices are "Not recommended for new designs", please use the replacement families Power Architecture (T1024, T1014), Arm Architecture (LS1012, LS1023).

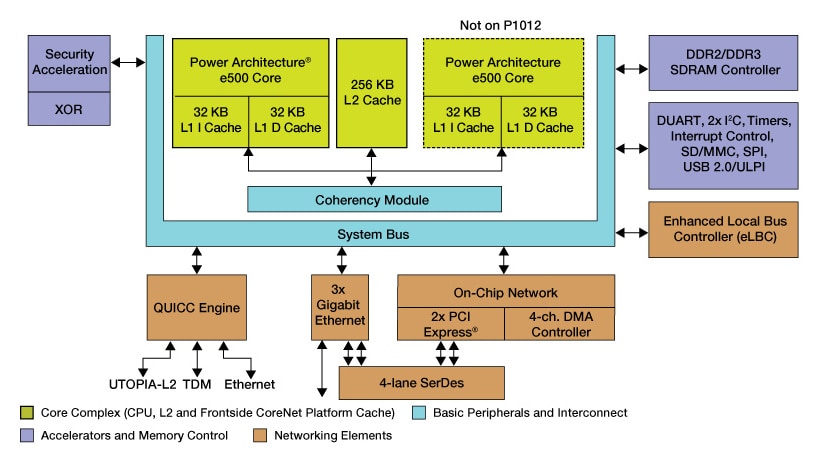

The QorIQ® P1 platform series, which includes the P1021 (dual-core) and P1012 (single-core) communications processors, offers the value of extensive integration and extreme power for a wide variety of applications in the networking, telecom, defense and industrial markets. Based on 45 nm technology for low-power implementation, the P1012 and P1021 processors provide single- and dual-core solutions for the 533 MHz to 800 MHz performance range, along with advanced security and a rich set of interfaces.

The P1012 and P1021 processors incorporate QUICC Engine® technology and are perfectly suited for multi-service gateways, Ethernet switch controllers, wireless LAN access points and high-performance general purpose control processor applications with tight thermal constraints. The QorIQ P1012 and P1021 processors are pin-compatible with the P1011, P1020 and P2 platform products, offering a six-chip range of cost-effective solutions. Scaling from a single core at 533 MHz (P1012) to a dual core at 1.2 GHz per core (P2020), the two QorIQ platforms deliver an impressive 4.5x aggregate frequency range.

Note: To see the product features close this window.

1 result

Include 18 NRND

Part | Order | CAD Model | Status | Budgetary Price excluding tax |

|---|---|---|---|---|

Active | 1 @ US$833.75 |

P1021Quick reference to our documentation types.

1-10 of 44 documents

Compact List

There are no results for this selection.

Please wait while your secure files are loading.

1-10 of 44 documents

Compact List

Receive the full breakdown. See the product footprint and more in the eCad file.

Quick reference to our software types.

3 software files

Note: For better experience, software downloads are recommended on desktop.

Please wait while your secure files are loading.

3 software files

Note: For better experience, software downloads are recommended on desktop.

1 training

1 trainings

There are no recently viewed products to display.

View or edit your browsing history

Help us improve your experience on our site. We invite you to take our five-question survey.