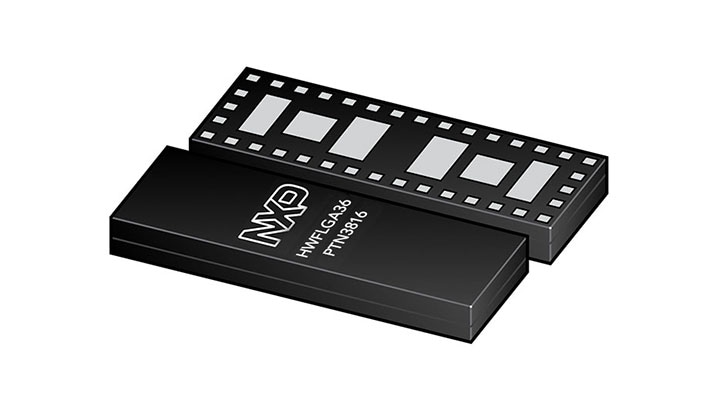

Type-C USB 3.2 and DisplayPort v 1.4 Combination Linear Redriver

PTN3816 is a high performance 20 Gbps per lane, 4 lane DisplayPort linear redriver for DisplayPort upstream (DP source side) and downstream (DP Sink side) applications. It is used to improve high-speed signal quality in DisplayPort interfaces in various platforms and applications.

The device provides pin programmable receive equalization, output linearity control to improve signal integrity and enable channel extension by reducing Inter-Symbol Interference (ISI). This IC also implements AUX snooping to monitor the AUX signals to optimally configure the link and achieve power saving and SI performance.

PTN3816 has control pins for application-specific configurability. These pins can either be strapped appropriately on the PCB or connected to a microcontroller’s GPIO pins.

PTN3816 is powered from 1.8 V supply. It is available in a small high performance HWFLGA36 package with 2.1 mm x 6.0 mm x 0.6 mm size and 0.4 mm pitch.

3.3 V, Two Differential Channel, 2-1 Multiplexer/Demultiplexer Switch

SuperSpeed USB 3.0 Redriver

Three-Lane High-Speed MIPI-Compatible Switch

USB PD TCPC PHY IC

|

|

|

|

|

|

|

|---|---|---|---|---|---|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Quick reference to our documentation types.

3 documents

Please wait while your secure files are loading.

Receive the full breakdown. See the product footprint and more in the eCad file.

Receive the full breakdown. See the product footprint and more in the eCad file.

1 hardware offering