Designed to power the AI-enabled edge including wearables, consumer medical, smart home and HMI devices, the i.MX

RT700

family delivers an optimized combination of high performance, extensive integration, advanced functionality and power

efficiency.

Building on the success of the i.MX RT500 and i.MX RT600 crossover MCUs, NXP announced the ultra-low power, multicore

i.MX RT700 with integrated eIQ® Neutron Neural Processing Unit (NPU).

The new i.MX RT700 family combines both existing families, offering even lower power consumption while adding more

performance through the increase of cores and other architectural enhancements:

- Integration of NXP’s eIQ Neutron NPU AI/ML accelerator

- Up to 7.5 MB low power internal SRAM array with 30 partitions for optimal multicore access

- New graphic accelerators include hardware JPEG and PNG decoding coupled with a vector graphics engine and MIPI-DSI

interface

- Up to 70% reduction in power consumption compared to previous generations

- 1.2V low power eUSB standard support allowing interaction with standard USB2.0 devices

i.MX RT700 Overview

i.MX RT700 Overview

The i.MX RT700 targets deeply embedded applications that require high performance sensing, DSP and computing

capabilities while maintaining low-power characteristics for longer battery life.

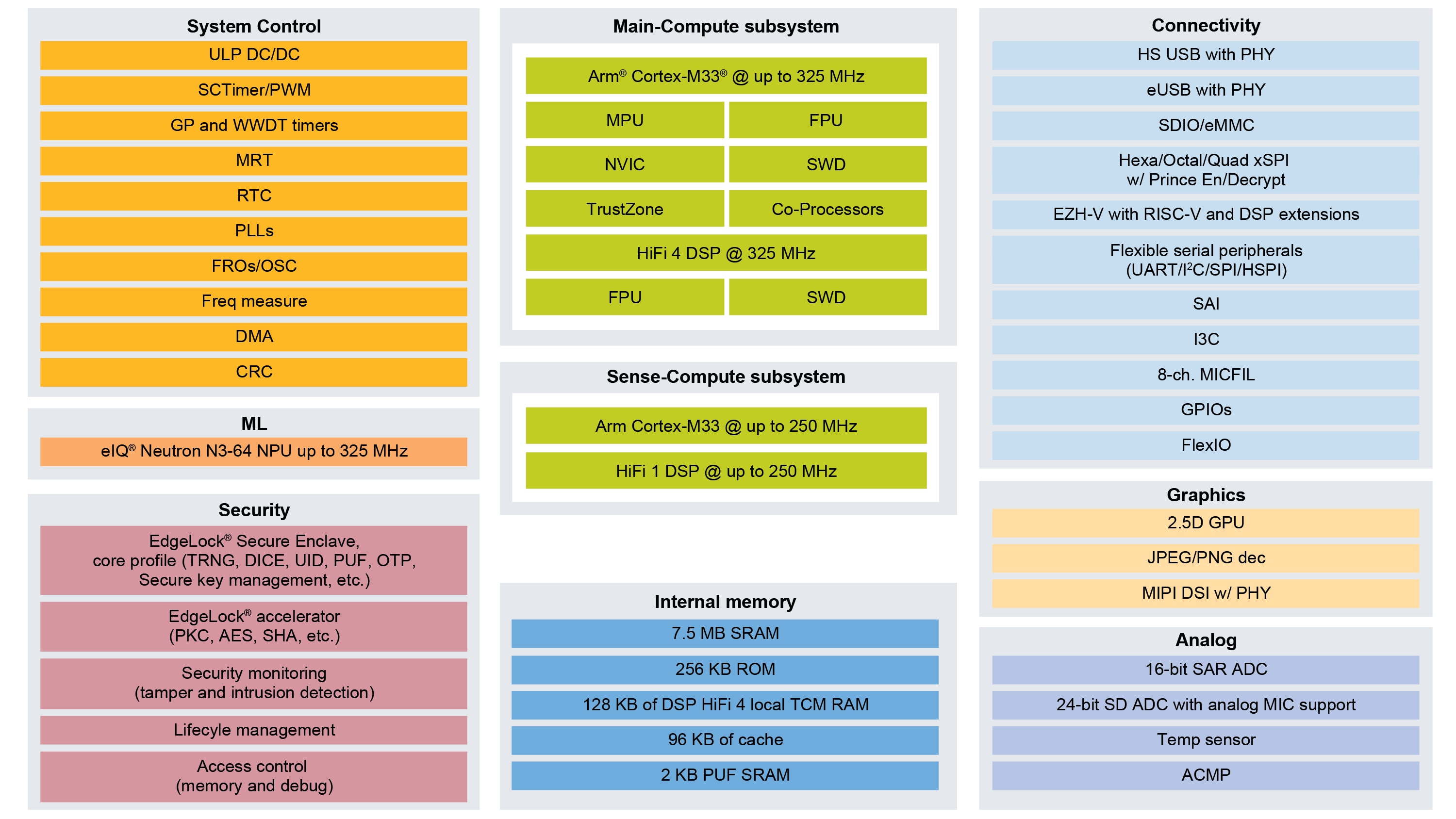

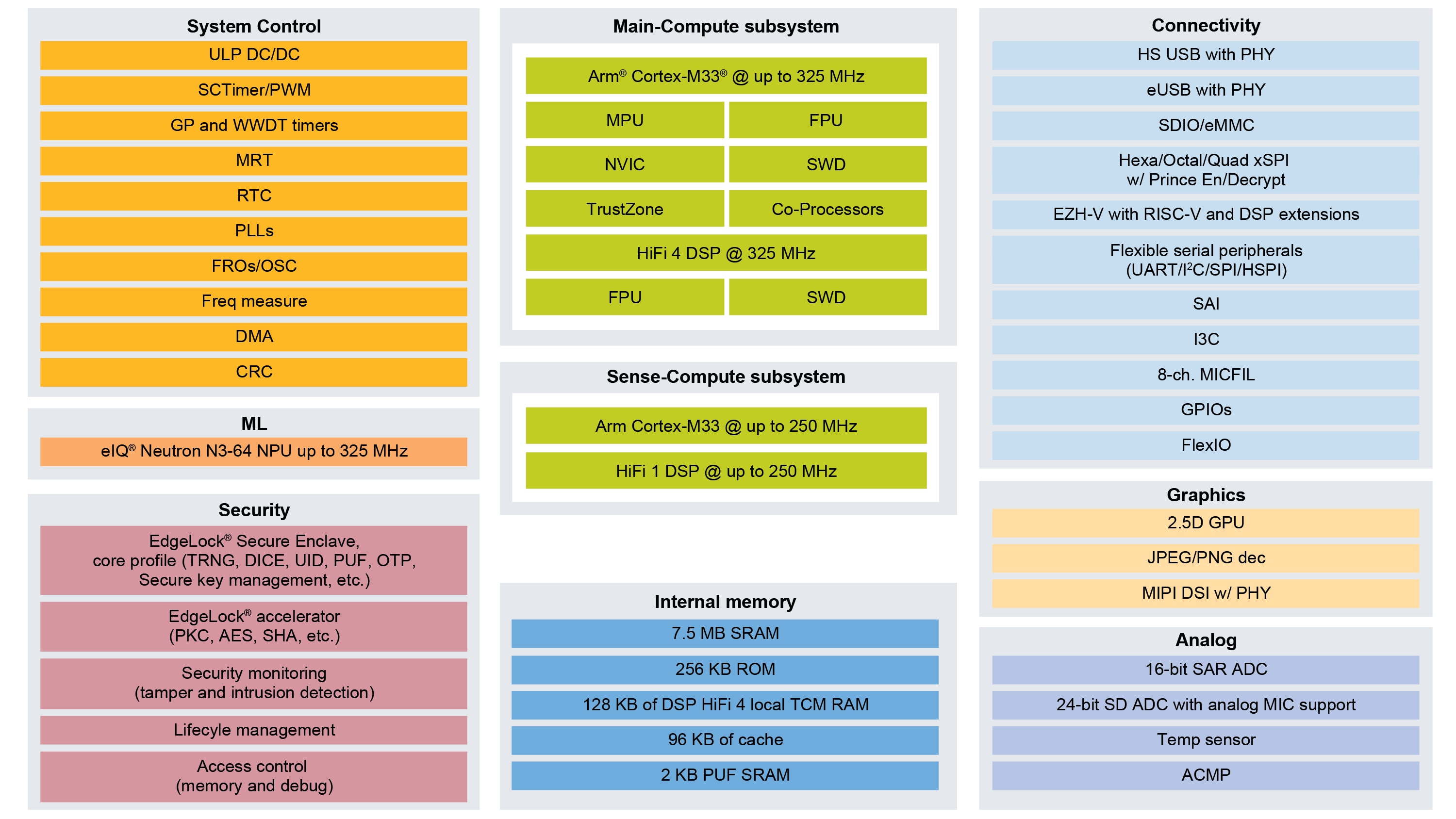

Multicore Architecture with eIQ® Neutron NPU

The new i.MX RT700 CPU architecture is composed of a high-performance main compute subsystem, a secondary

“always-on”

sense-compute subsystem and specialized coprocessors.

i.MX RT700 Block Diagram. For a better experience, download the block diagram.

i.MX RT700 Block Diagram. For a better experience, download the block diagram.

The main compute subsystem uses a 325 MHz capable Arm® Cortex®-M33 (CM33). Similar to the i.MX RT600 crossover MCU,

the

i.MX RT700 includes a Cadence Tensilica® HiFi 4 DSP. The HiFi 4 is a high performance DSP core based upon a Very Long

Instruction Word (VLIW) architecture, which is capable of processing up to eight 32x16 MACs per instruction cycle. It

can

be used for offloading high-performance numerical tasks such as audio and image processing and supports both fixed-point

and floating-point operations.

The CM33 serves as a general-purpose execution platform, which is available at system boot. It handles the initial

startup of the HiFi 4 DSP as well as the other coprocessors and external memory interfaces. The low-power sense

compute

subsystem is composed of another 250 MHz capable CM33 and low-power Cadence Tensilica® HiFi 1 DSP. It’s primarily

intended for always-on applications and can access a select number of general-purpose peripherals tuned for ultra-low

power operation. Applications include wake word detection with the PDM microphone interface, real-time sensor hubs and

Bluetooth LE audio processing.

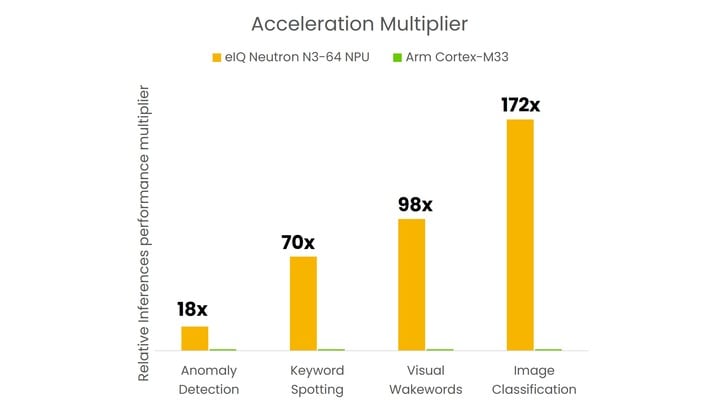

To support acceleration of AI and machine learning models, the i.MX RT700 includes NXP’s eIQ® Neutron NPU. eIQ® Neutron

is a scalable hardware accelerator architecture found in a variety of NXP offerings purpose built for AI and machine

learning applications.

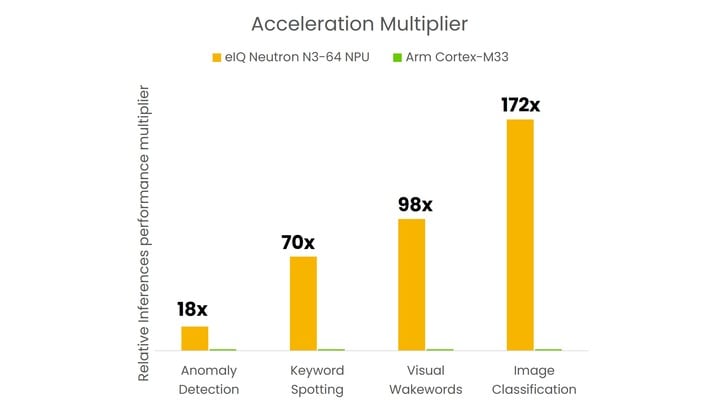

eIQ Neutron NPU Acceleration Multiplier. For a better experience, download this chart.

eIQ Neutron NPU Acceleration Multiplier. For a better experience, download this chart.

i.MX RT700 features the eIQ Neutron N3-64 NPU and its capability is positioned between the N1-16 found in the MCX N947

MCU and the N3-1024 found in the high-end i.MX 95 applications processors. The NPU has been tuned for deeply embedded,

low-power applications and can achieve a 172x performance increase while reducing power consumption per inference by up to

119x when compared to a general-purpose processor.

AL/ML application development with eIQ Neutron NPU is supported by the eIQ ML Software Development Environment. The

toolset enables developers with a workflow that translates code from common ML frameworks, such as TensorFlow Lite, into

equivalent computation graphs that can be accelerated on the NPU.

Another interesting processing resource in the i.MX RT700 is the new EZH-V IO coprocessor based upon the open RISC-V

Instruction Set Architecture (ISA).

The RISC-V ISA in the EZH-V has been extended to:

- Add hardware multiply and divide capabilities

- Add floating point capabilities

- Add bit manipulation capabilities

- Improved code density

The EZH-V can implement “SmartDMA” tasks for post processing graphics data and be a high-speed data manipulation bridge

between the GPU, CPU and the hardware interfaces such as FlexIO and MIPI DSI. The EZH-V is available for any other

general-purpose IO tasks and is connected to an extensive selection of trigger inputs from GPIOs and most on-chip

peripherals. Code for EZH-V is developed with an RISC-V LLVM-based tool chain that will be available in the MCUXpresso

SDK.

A Sophisticated Memory Architecture for Processing, Graphics and Storage

The memory architecture in the i.MX RT700 was optimized for flexible, low contention interconnect between the different

internal processing resources. A large 7.5 MB SRAM array is divided into 30 partitions, each accessible to bus

controllers to reduce contention between the CM33 cores, HiFi DSPs, DMA controllers and the EZH-V. The large internal

memory can provide fast access to large graphics frame buffers and can be coupled to the built-in hardware JPEG and PNG

decoders.

Each of the 30 individual SRAM partitions can be used exclusively as a code or data store, dedicated to a CPU, or

shared between the various cores. Each partition can be independently placed in a low-power retention mode or powered

off entirely.

There are two XCACHE modules to serve as dedicated system and code caches, which can be accessed by the compute subsystem

primary CM33, the HiFi 4, the EZH-V and two instances of the eDMA peripheral. These caches can significantly improve

performance when accessing external memory. The HiFi 4 has its own local Tightly Coupled Memory (TCM) as well as local

instruction/data cache to place the most performance critical DSP.

External Memory Support

Like the previous i.MX RT500 and i.MX RT600 devices, the i.MX RT700 is a Flashless architecture. Three xSPI external

memory controllers have been included to interface with quad and octal flash memories. Two of the xSPI instances support

16-bit interfaces to external PSRAM for adding non-volatile storage.

The xSPI interfaces up to 400 MHz DDR and 200 MHz SDR transfers. This enables large blocks of fast external RAM to be

added for large ML models, data buffers and graphics assets. External memory connected via the xSPI controller is

accessible via the system memory map. Code can be Executed-In-Place (XIP) from externally connected flash. The xSPI

interfaces are cached to ensure maximum performance.

Built in into the xSPI controller is a flexible Look Up Table (LUT) based command engine that can be adapted to support

virtually any NOR flash memory. The i.MX RT700 boot ROM can use flash connected to the xSPI interface to boot the

system. There are several options available including copying boot codes to internal SRAM or direct XIP. Encrypted code

can be decrypted on-the-fly as is accessed from external flash.

Bulk commodity storage memories can be connected via the SHDC/eMMC controller. The i.MX RT700 boot ROM also supports

system boot from an eMMC/SD Card. This allows SD/eMMC memories to both boot the i.MX RT700 and be available for typical

file systems that store configuration and graphics assets.

Packaging for Space Constrained Products

The i.MX RT700 will be offered in 324-ball 7.3x7.3mm, 0.4 mm pitch Fan-out Wafer Level (FOWLP) and a 256-ball

6.025x6.025mm, 0.35 mm pitch Wafer Level Chip Scale (WLCSP) packages. These packages enable designers to embed the i.MX

RT700 in the most tightly constrained spaces.

Ideal for wearable and personal fitness applications

Ideal for wearable and personal fitness applications

Applications such as wearables, personal fitness, consumer medical and augmented reality can see a huge benefit from the

high capabilities, ultra-low power consumption and dense packaging.

Ultra-Low Power, Deeply Embedded Designs Using i.MX RT700

The i.MX RT700 represents significant advancements in low-power embedded processing technology. Designed for ultra-low

power and high processing capability, the i.MX RT700 can serve many applications that require long battery life while

providing the best user experience with dedicated graphics accelerators.

The multicore architecture gives designers a great deal of flexibility in how to approach their product designs. The

combination of general-purpose cores with high-performance DSPs and a powerful NPU make the i.MX RT700 unique in its

ability to enable differentiated embedded products.