EdgeLock® Assurance

The TJA1153, part of the EdgeLock Assurance program, is designed to meet industry standards and follows NXP's security-by-design approach.

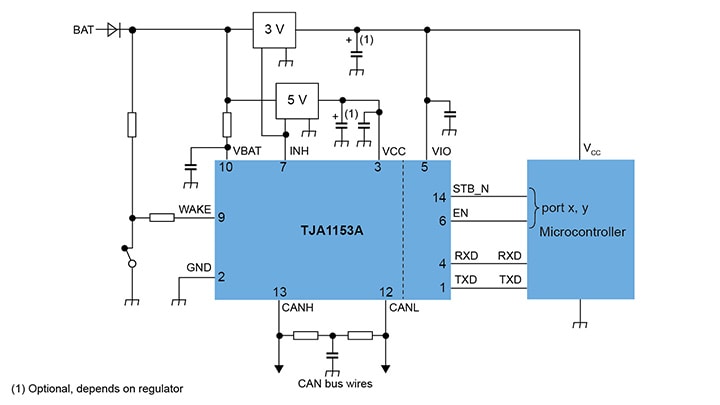

NXP's new secure CAN transceiver TJA1153A provides a seamless and very cost-effective solution for securing classical CAN and CAN FD communication without cryptography. The TJA1153A belongs to a new generation of automotive high-speed CAN/CAN FD transceivers, offering security functions. It provides an interface between a classical CAN or CAN FD protocol controller and the physical two-wire CAN bus. As long as no security incidents have been detected, the TJA1153A behaves like a standard CAN transceiver with Sleep mode.

The security incidents that can be detected and contained are:

Note: To see the product features close this window.

Part numbers include: TJA1153ATK.

The TJA1153, part of the EdgeLock Assurance program, is designed to meet industry standards and follows NXP's security-by-design approach.

Quick reference to our documentation types.

3 documents

Please wait while your secure files are loading.

1-5 of 12 hardware offerings

1 software offerings

Please wait while your secure files are loading.

1 software offerings

To find a complete list of our partners that support this product, please see our Partner Marketplace.

1 engineering service

There are no results for this selection.

To find a complete list of our partners that support this product, please see our Partner Marketplace.