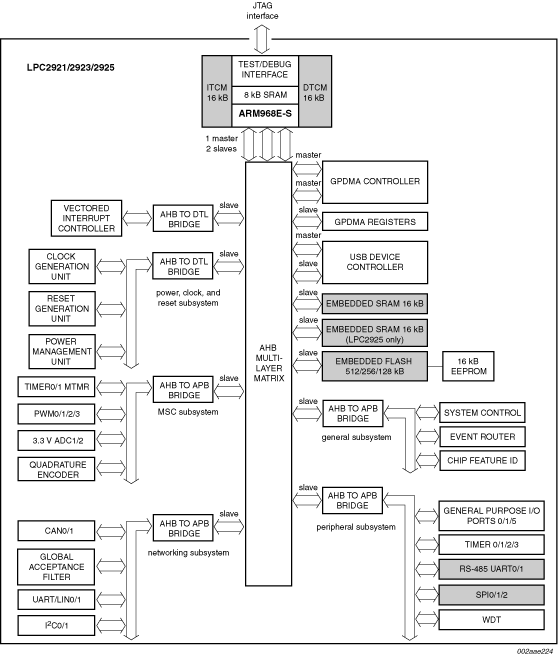

The LPC2921/2923/2925 combine an ARM968E-S CPU core with two integrated TCM blocks operating at frequencies of up to 125 MHz, Full-speed USB 2.0 device controller, CAN and LIN, up to 40 kB SRAM, up to 512 kB flash memory, two 10-bit ADCs, and multiple serial and parallel interfaces in a single chip targeted at consumer, industrial, and communication markets. To optimize system power consumption, the LPC2921/2923/2925 has a very flexible Clock Generation Unit (CGU) that provides dynamic clock gating and scaling.