Rev. 1.0 — 19 November 2024

**Product brief**

## 1 Introduction

This product brief is intended to provide overview/summary information for the purpose of evaluating a product for design suitability. It is intended for quick reference only and should not be relied upon to contain detailed and full information.

Some of the content in this product brief is extracted from the product's full data sheet. In case of any inconsistency or conflict, the full data sheet shall prevail.

For detailed and full information, see the relevant PF9455 full data sheet, available via the NXP Secure Files content interface.

## 2 General description

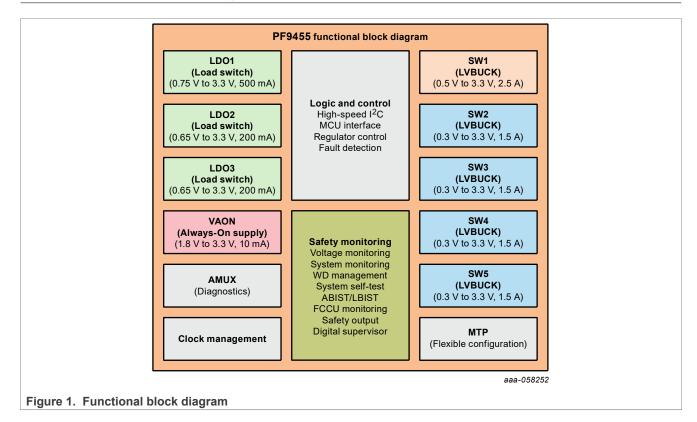

The PF9455 is a power management integrated circuit (PMIC) optimized for high-performance i.MX9x based applications. It Integrates multiple high-efficiency switch mode and linear voltage regulators to support base system power from a pre-regulated system rail (3.3 V to 5.0 V). It provides low quiescent current in Standby and Low-power Off modes.

A built-in multiple time programmable configuration stores key startup configurations, drastically reducing the number of external components typically used to set output voltage and sequence of external regulators. Regulator parameters are adjustable through high-speed I<sup>2</sup>C communication after startup, offering flexibility for various system states.

The PF9455 complies with the IEC61508 industrial safety specification targeting high safety integrity levels up to SIL 2.

## 3 Features and benefits

- Up To five buck regulators with internal power stage and programmable current limit

- Three low-dropout linear regulators with load switch operation

- Ultra-low power always-on LDO supply

- Two external voltage monitoring inputs

- Programmable I/O interfacing pins

- Advanced frequency management with frequency spread spectrum

- Multi-channel analog multiplexer for system voltage monitoring

- High-speed I<sup>2</sup>C interface with up to 3.4 MHz operation

- Advanced thermal monitoring and thermal shutdown protection

- Functional safety architecture to target industrial applications up to SIL 2

- Multiple time programmable configuration (MTP)

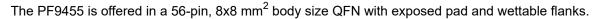

- 56-pin QFN package with exposed pad

- Operating ambient temperature from -40 °C to 105 °C, junction temperate from -40 °C to 150 °C

## **4** Applications

- High-end consumer and industrial

- Human machine interfaces

- Connectivity domain controller

- Telematics

#### **Ordering information** 5

#### Table 1. Ordering information

| Type number <sup>[1]</sup> | Package |                                                                                                                                                    |               |  |  |  |

|----------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--|--|--|

| Type number                | Name    | Description                                                                                                                                        | Version       |  |  |  |

| PF9455                     | HVQFN56 | HVQFN56, plastic thermal enhanced very thin quad flat<br>pack; no leads, wettable flank, 56 terminals, 0.5 mm pitch,<br>8 mm x 8 mm x 0.53 mm body | SOT684-32(DD) |  |  |  |

[1] To order parts in tape and reel, add the R2 suffix to the part number.

#### Table 2. Ordering options

| Part number <sup>[1][2]</sup> | Target market | NXP processor | System<br>comments | Safety grade | OTP ID |

|-------------------------------|---------------|---------------|--------------------|--------------|--------|

| PPF9455AVMA7ES                | Industrial    | i.MX 943      | LPDDR5 memory      | QM           | MA7    |

| PPF9455AVMA8ES                | Industrial    | i.MX 943      | LPDDR4 memory      | QM           | MA8    |

| PPF9455AVSA3ES                | Industrial    | i.MX 943      | LPDDR5 memory      | SIL 2        | SA3    |

| PPF9455AVSA4ES                | Industrial    | i.MX 943      | LPDDR4 memory      | SIL 2        | SA4    |

P = engineering sample part number M = production part number [1] [2]

## 6 Functional block diagram

## 7 Package pinout

### 7.1 Pin description

#### Table 3. QFN56 pin description

| Pin | Pin Name | Description                   | Min  | Max | Units |

|-----|----------|-------------------------------|------|-----|-------|

| 1   | STBY     | Standby request               | -0.3 | 6.0 | V     |

| 2   | LDO2IN   | LDO2 input                    | -0.3 | 6.0 | V     |

| 3   | LDO2OUT  | LDO2 Output                   | -0.3 | 6.0 | V     |

| 4   | FCCU0    | FCCU fault monitoring input 0 | -0.3 | 6.0 | V     |

| 5   | SW3IN    | SW3 Input                     | -0.3 | 6.0 | V     |

| 6   | SW3LXA   | SW3 switching node A          | -0.3 | 6.0 | V     |

| 7   | SW3LXB   | SW3 switching node B          | -0.3 | 6.0 | V     |

| 8   | SW2LXB   | SW2 switching node B          | -0.3 | 6.0 | V     |

| 9   | SW2LXA   | SW2 switching node A          | -0.3 | 6.0 | V     |

| 10  | SW2IN    | SW2 input                     | -0.3 | 6.0 | V     |

| 11  | NC1      | Not connected                 | -0.3 | 6.0 | V     |

| 12  | LDO3OUT  | LDO3 output                   | -0.3 | 6.0 | V     |

| Table 3. | QFN56 | pin | descriptioncontinued |

|----------|-------|-----|----------------------|

|----------|-------|-----|----------------------|

| Pin | Pin Name | Description                            | Min  | Max  | Units |

|-----|----------|----------------------------------------|------|------|-------|

| 13  | LDO3IN   | LDO3 input                             | -0.3 | 6.0  | V     |

| 14  | XFAILB   | External fail                          | -0.3 | 6.0  | V     |

| 15  | AMUX     | Analog multiplexer output              | -0.3 | 6.0  | V     |

| 16  | VAON     | Always-on output                       | -0.3 | 6.0  | V     |

| 17  | NC2      | Not connected                          | -0.3 | 6.0  | V     |

| 18  | VIN      | PMIC input supply                      | -0.3 | 6.0  | V     |

| 19  | VDDOTP   | OTP supply                             | -0.3 | 10.0 | V     |

| 20  | SW2FB    | SW2 feedback                           | -0.3 | 6.0  | V     |

| 21  | SW3FB    | SW3 feedback                           | -0.3 | 6.0  | V     |

| 22  | SW5FB    | SW5 feedback                           | -0.3 | 6.0  | V     |

| 23  | SW4FB    | SW4 feedback                           | -0.3 | 6.0  | V     |

| 24  | DGND     | Digital ground                         | -0.3 | 0.3  | V     |

| 25  | VDIG     | Internal digital supply                | -0.3 | 2.0  | V     |

| 26  | VANA     | Internal analog supply                 | -0.3 | 2.0  | V     |

| 27  | AGND     | Analog ground                          | -0.3 | 0.3  | V     |

| 28  | PWRON    | Power-on request                       | -0.3 | 6.0  | V     |

| 29  | VMON1    | External VMON1                         | -0.3 | 6.0  | V     |

| 30  | VMON2    | External VMON2                         | -0.3 | 6.0  | V     |

| 31  | SW4IN    | SW4 input                              | -0.3 | 6.0  | V     |

| 32  | SW4LXA   | SW4 switching node A                   | -0.3 | 6.0  | V     |

| 33  | SW4LXB   | SW4 switching node B                   | -0.3 | 6.0  | V     |

| 34  | SW5LXB   | SW5 switching node B                   | -0.3 | 6.0  | V     |

| 35  | SW5LXA   | SW5 switching node A                   | -0.3 | 6.0  | V     |

| 36  | SW5IN    | SW5 input                              | -0.3 | 6.0  | V     |

| 37  | SW1LXB   | SW1 switching node B                   | -0.3 | 6.0  | V     |

| 38  | SW1LXA   | SW1 switching node A                   | -0.3 | 6.0  | V     |

| 39  | SW1INB   | SW1 input B                            | -0.3 | 6.0  | V     |

| 40  | SW1INA   | SW1 input A                            | -0.3 | 6.0  | V     |

| 41  | INTB     | Interrupt request                      | -0.3 | 6.0  | V     |

| 42  | FSYNC    | Clock sync input                       | -0.3 | 6.0  | V     |

| 43  | RSTB     | MCU reset pin                          | -0.3 | 6.0  | V     |

| 44  | PGOOD    | Power good                             | -0.3 | 6.0  | V     |

| 45  | GPIO1    | Programmable IO1                       | -0.3 | 6.0  | V     |

| 46  | GPIO2    | Programmable IO2                       | -0.3 | 6.0  | V     |

| 47  | FCCU1    | XRESET / FCCU fault monitoring input 1 | -0.3 | 6.0  | V     |

| 48  | VDDIO    | I/O supply input                       | -0.3 | 6.0  | V     |

| Pin | Pin Name | Description            | Min  | Max | Units |

|-----|----------|------------------------|------|-----|-------|

| 49  | SW1FB    | SW1 feedback           | -0.3 | 6.0 | V     |

| 50  | SDA      | I <sup>2</sup> C data  | -0.3 | 6.0 | V     |

| 51  | SCL      | I <sup>2</sup> C clock | -0.3 | 6.0 | V     |

| 52  | LDO1IN   | LDO1 input             | -0.3 | 6.0 | V     |

| 53  | LDO10UT  | LDO1 output            | -0.3 | 6.0 | V     |

| 54  | FS0B     | Fail-safe output       | -0.3 | 6.0 | V     |

| 55  | GPIO3    | Programmable IO3       | -0.3 | 6.0 | V     |

| 56  | GPIO4    | Programmable IO4       | -0.3 | 6.0 | V     |

| 57  | EPAD     | Exposed-pad ground     | -0.3 | 0.3 | V     |

Table 3. QFN56 pin description...continued

## 8 Absolute maximum ratings

#### Table 4. Absolute maximum ratings

| Symbol | Description                              | Min  | Тур | Мах | Unit |

|--------|------------------------------------------|------|-----|-----|------|

| VIN    | Main input supply voltage                | -0.3 |     | 6   | V    |

| SWxIN  | Switching regulator input supply voltage | -0.3 |     | 6   | V    |

| LDOxIN | LDO regulator input supply voltage       | -0.3 |     | 6   | V    |

| VDDIO  | IO input supply voltage                  | -0.3 |     | 6   | V    |

| VDDOTP | OTP programming input supply voltage     | -0.3 |     | 10  | V    |

### **NXP Semiconductors**

Highly optimized PMIC for functionally safe and quality managed i.MX9 MPU-based applications

## 9 Revision history

#### Table 5.

| Revision | Date             | Description of changes      |

|----------|------------------|-----------------------------|

| 1.0      | 19 November 2024 | Initial preliminary release |

## Legal information

### Definitions

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

### Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at https://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**No offer to sell or license** — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

**Quick reference data** — The Quick reference data is an extract of the product data given in the Limiting values and Characteristics sections of this document, and as such is not complete, exhaustive or legally binding.

$\mbox{Export control}$  — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**HTML publications** — An HTML version, if available, of this document is provided as a courtesy. Definitive information is contained in the applicable document in PDF format. If there is a discrepancy between the HTML document and the PDF document, the PDF document has priority.

**Translations** — A non-English (translated) version of a document, including the legal information in that document, is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security — Customer understands that all NXP products may be subject to unidentified vulnerabilities or may support established security standards or specifications with known limitations. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP.

NXP has a Product Security Incident Response Team (PSIRT) (reachable at <u>PSIRT@nxp.com</u>) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

Suitability for use in industrial applications (functional safety) — This NXP product has been qualified for use in industrial applications. It has been developed in accordance with IEC 61508, and has been SIL-classified accordingly. If this product is used by customer in the development of, or for incorporation into, products or services (a) used in safety critical applications or (b) in which failure could lead to death, personal injury, or severe physical or environmental damage (such products and services hereinafter referred to as "Critical Applications"), then customer makes the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, safety, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP. As such, customer assumes all risk related to use of any products in Critical Applications and NXP and its suppliers shall not be liable for any such use by customer. Accordingly, customer will indemnify and hold NXP harmless from any claims, liabilities, damages and associated costs and expenses (including attorneys' fees) that NXP may incur related to customer's incorporation of any product in a Critical Application.

$\ensuremath{\text{NXP B.V.}}$  – NXP B.V. is not an operating company and it does not distribute or sell products.

#### **Trademarks**

NXP — wordmark and logo are trademarks of NXP B.V.

Notice: All referenced brands, product names, service names, and trademarks are the property of their respective owners.

Absolute maximum ratings ......10

Highly optimized PMIC for functionally safe and quality managed i.MX9 MPU-based applications

Tab. 4.

Tab. 5.

### **Tables**

| Tab. 1. | Ordering information5  |  |

|---------|------------------------|--|

| Tab. 2. | Ordering options5      |  |

|         | QFN56 pin description7 |  |

## **Figures**

| Fig 1    | Functional block diagram6 | Fig 2    | PE0/55 package pipout (top view) 7 |

|----------|---------------------------|----------|------------------------------------|

| i iy. i. |                           | i iy. z. |                                    |

### **NXP Semiconductors**

Highly optimized PMIC for functionally safe and quality managed i.MX9 MPU-based applications

### Contents

| 1   | Introduction             | 1 |

|-----|--------------------------|---|

| 2   | General description      | 2 |

| 3   | Features and benefits    |   |

| 4   | Applications             | 4 |

| 5   | Ordering information     |   |

| 6   | Functional block diagram |   |

| 7   | Package pinout           |   |

| 7.1 | Pin description          |   |

| 8   | Absolute maximum ratings |   |

| 9   | Revision history         |   |

|     | Legal information        |   |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

© 2024 NXP B.V.

All rights reserved.

For more information, please visit: https://www.nxp.com

Document feedback Date of release: 19 November 2024 Document identifier: PF9455\_PB