# **BMI7014**

# 14 cells battery cell controller IC

Rev. 3 — 8 August 2024

Product data sheet

## 1 General description

The BMI7014 is a SMARTMOS lithium-ion battery cell controller IC family designed for industrial applications, such as energy storage systems (ESS) and uninterruptible power supply (UPS) systems.

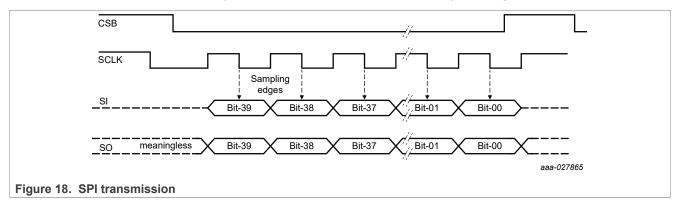

The device performs ADC conversions of the differential cell voltages and battery temperature measurements. The information is transmitted to MCU using one of the microcontroller interfaces (serial peripheral interface (SPI) or transformer physical layer (TPL)) of the IC.

#### 2 Features

- 9.6 V ≤ V<sub>PWR</sub> ≤ 63 V operation, 75 V transient

- 7 to 14 cells management

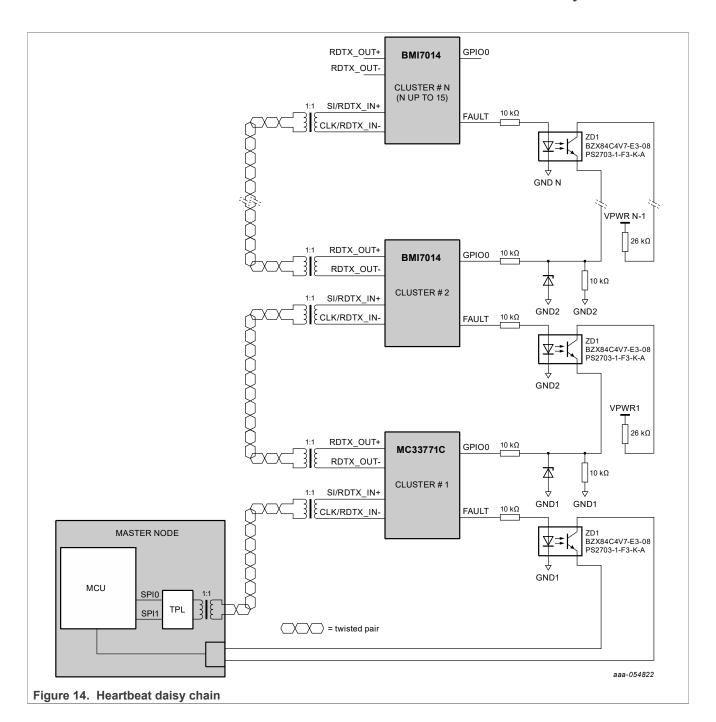

- Isolated 2.0 Mbps differential communication or 4.0 Mbps SPI

- · Addressable on initialization

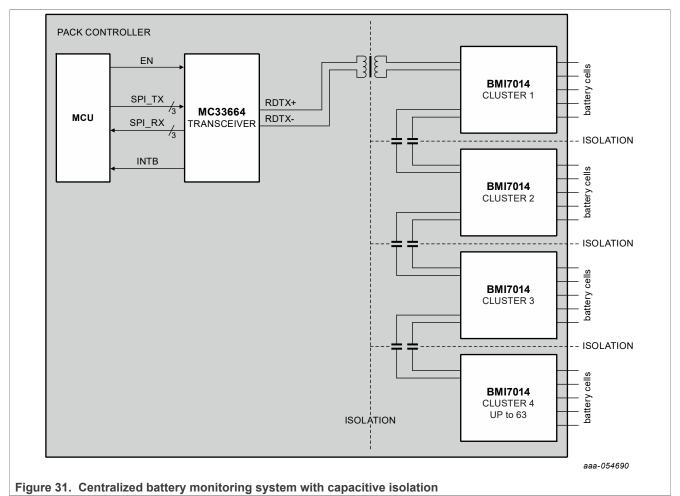

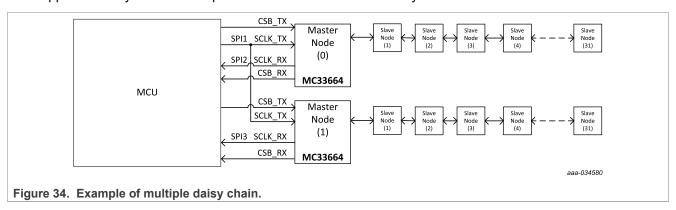

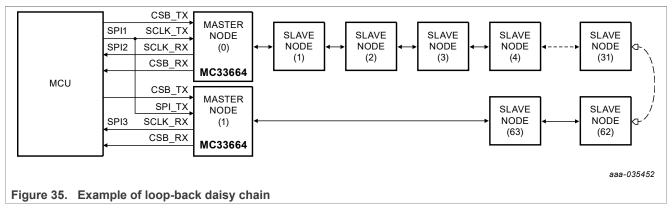

- Bidirectional transceiver to support up to 63 nodes in daisy chain

- · 0.8 mV maximum total voltage measurement error

- · Averaging of cell voltage measurements

- · Total stack voltage measurement

- · Seven GPIO/temperature sensor inputs

- 5.0 V at 5.0 mA reference supply output

- Automatic over/undervoltage and temperature detection routable to fault pin

- Integrated sleep mode over/undervoltage and temperature monitoring

- Onboard 300 mA passive cell balancing with diagnostics

- · Hot plug capable

- · Detection of internal and external faults, as open lines, shorts, and leakages

14 cells battery cell controller IC

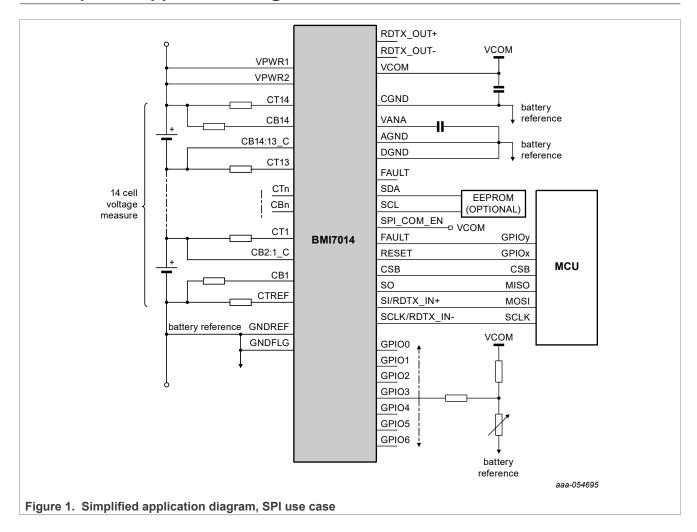

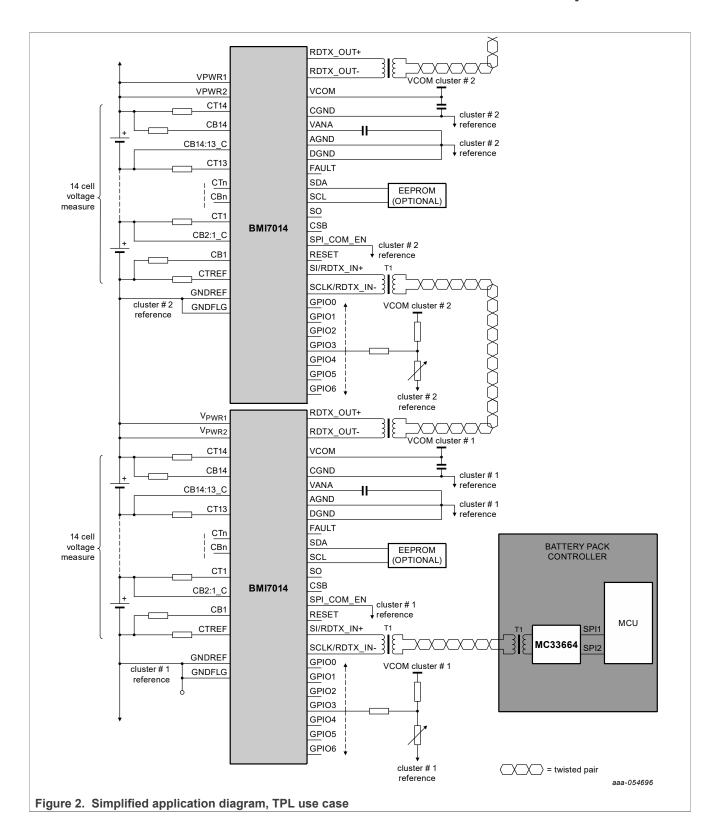

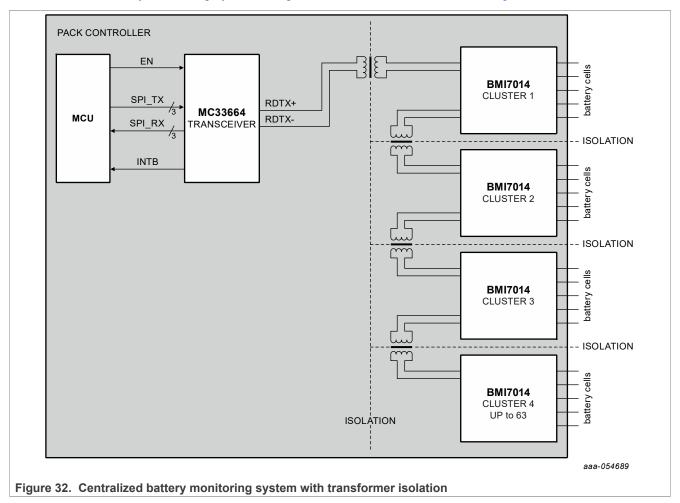

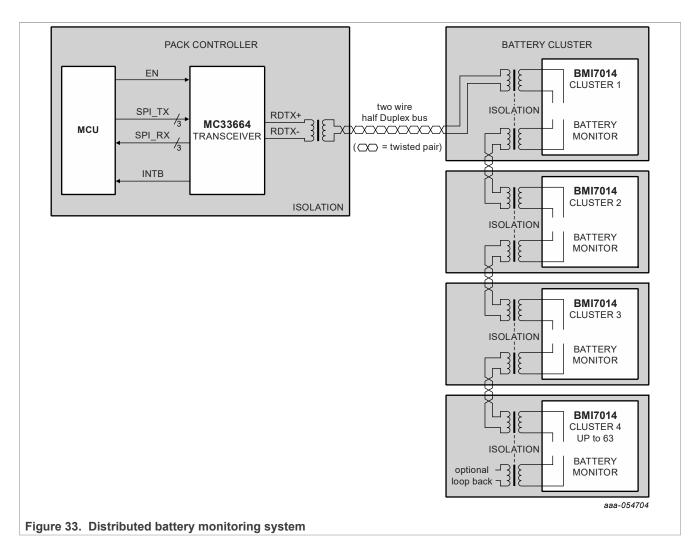

# 3 Simplified application diagram

## 14 cells battery cell controller IC

14 cells battery cell controller IC

# 4 Applications

- Energy storage systems

- Uninterruptible power supply (UPS)

# 5 Ordering information

#### 5.1 Part numbers definition

# **MBMI7014 T A y AE/R2**

Table 1. Part number breakdown

| Code | Option   | Description                           |

|------|----------|---------------------------------------|

|      | Т        | TPL communication type                |

|      | Α        | A (silicon revision)                  |

| V    | 1        | y = 1 (Premium accuracy performance)  |

| у    | <b>I</b> | y = 2 (Standard accuracy performance) |

|      | AE       | Package suffix                        |

|      | R2       | Tape and reel indicator               |

14 cells battery cell controller IC

#### 5.2 Part numbers list

This section describes the part numbers available to be purchased along with their differences. Valid orderable part numbers are provided on the web. To determine the orderable part numbers for this device, go to <a href="http://www.nxp.com">http://www.nxp.com</a>.

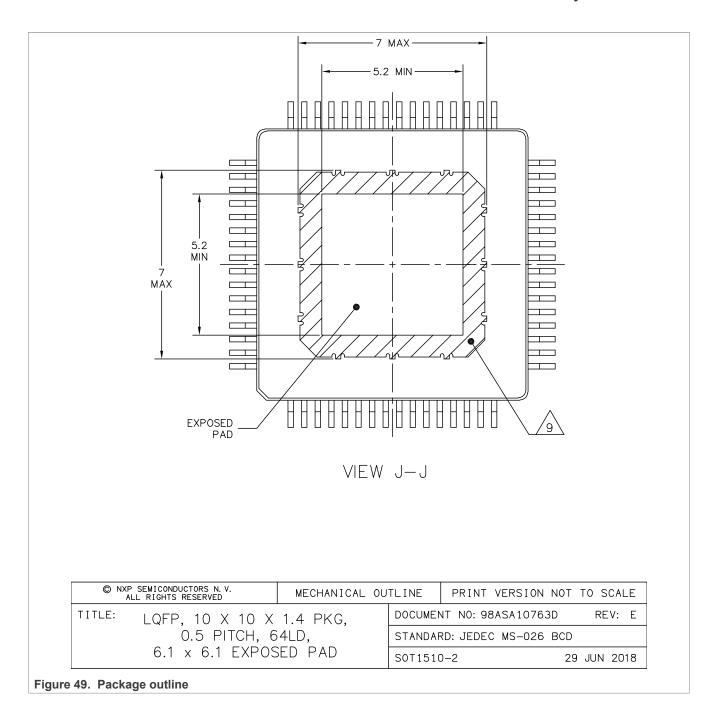

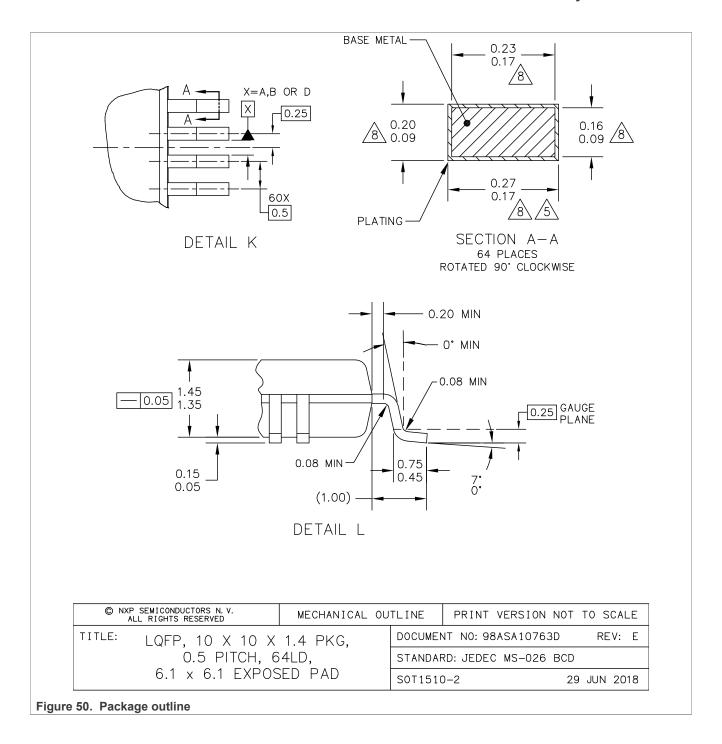

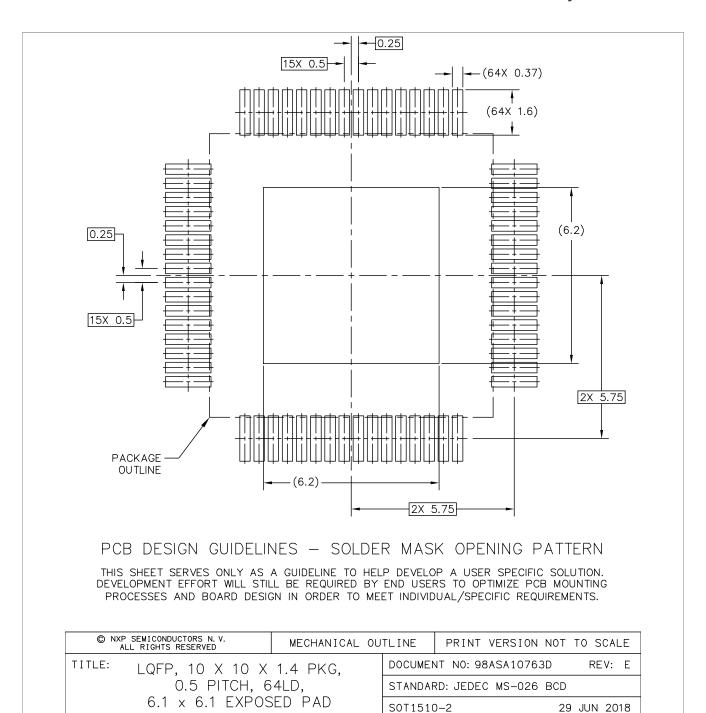

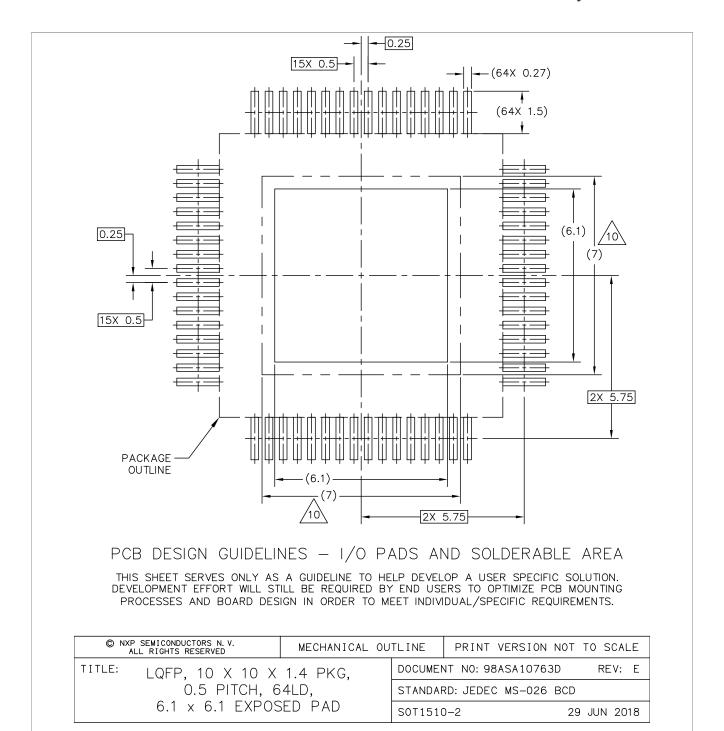

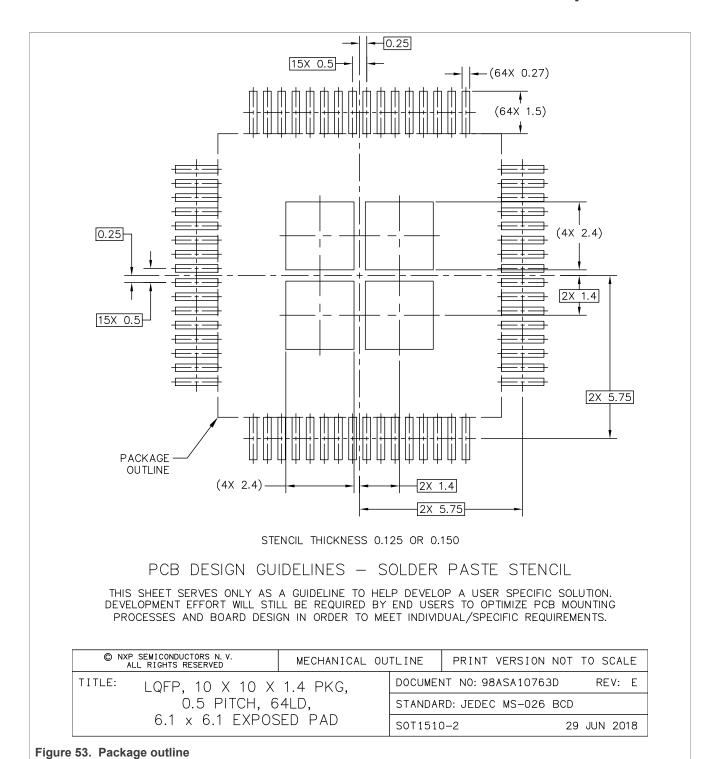

Table 2. Advanced orderable part table Temperature range is -20 °C to 85 °C Package type is 64-pin LQFP-EP

| Orderable part | Description                                 |

|----------------|---------------------------------------------|

| BMI7014TA1AE   | Premium cell voltage accuracy performances  |

| BMI7014TA2AE   | Standard cell voltage accuracy performances |

14 cells battery cell controller IC

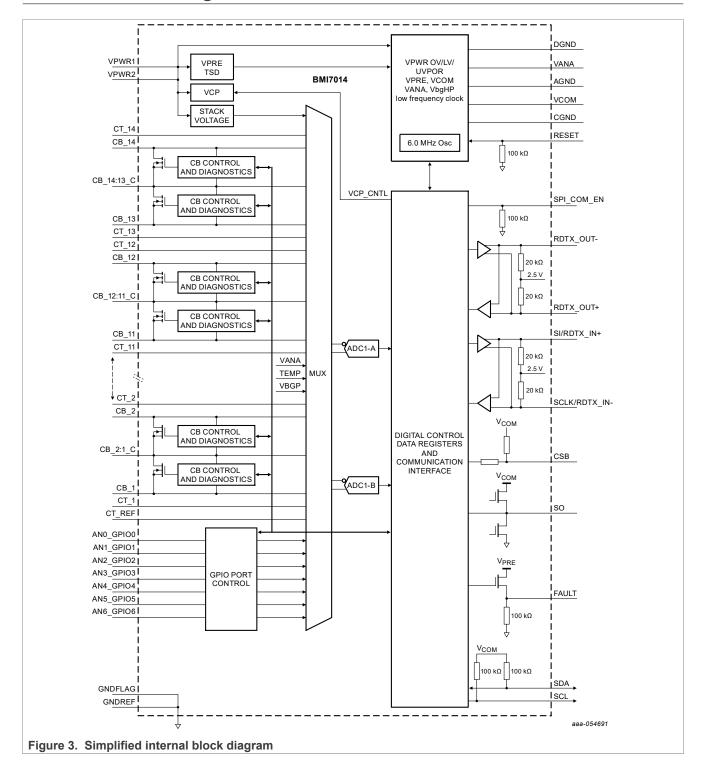

# 6 Internal block diagram

14 cells battery cell controller IC

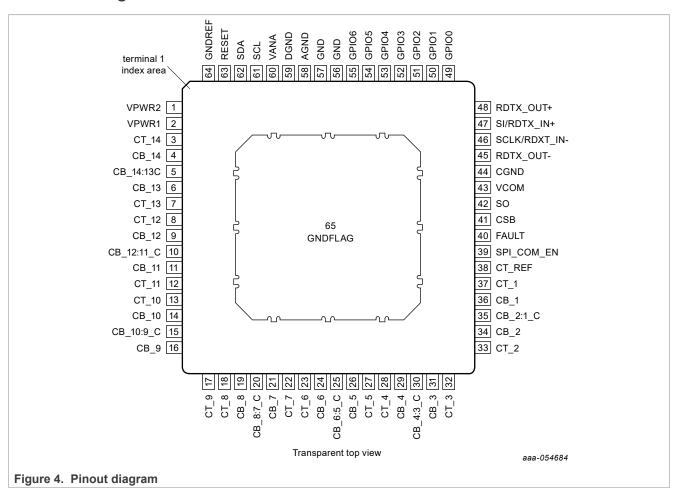

# 7 Pinning information

### 7.1 Pinout diagram

#### 7.2 Pin definitions

Table 3. Pin definitions

| Number | Name       | Function | Definition                                                                |

|--------|------------|----------|---------------------------------------------------------------------------|

| 1      | VPWR2      | Input    | Power input to the BMI7014                                                |

| 2      | VPWR1      | Input    | Power input to the BMI7014                                                |

| 3      | CT_14      | Input    | Cell pin 14 input. Terminate to LPF resistor.                             |

| 4      | CB_14      | Output   | Cell balance driver. Terminate to cell 14 cell balance load resistor.     |

| 5      | CB_14:13_C | Output   | Cell balance 14:13 common. Terminate to CB_14:13_C balance load resistor. |

| 6      | CB_13      | Output   | Cell balance driver. Terminate to cell 13 cell balance load resistor.     |

| 7      | CT_13      | Input    | Cell pin 13 input. Terminate to LPF resistor.                             |

| 8      | CT_12      | Input    | Cell pin 12 input. Terminate to LPF resistor.                             |

| 9      | CB_12      | Output   | Cell balance driver. Terminate to cell 12 cell balance load resistor.     |

BMI7014

All information provided in this document is subject to legal disclaimers.

© 2024 NXP B.V. All rights reserved.

## 14 cells battery cell controller IC

Table 3. Pin definitions...continued

| Number | Name       | Function | Definition                                                                                             |

|--------|------------|----------|--------------------------------------------------------------------------------------------------------|

| 10     | CB_12:11_C | Output   | Cell balance 12:11 common. Terminate to CB_12:11_C balance load resistor.                              |

| 11     | CB_11      | Output   | Cell balance driver. Terminate to cell 11 cell balance load resistor.                                  |

| 12     | CT_11      | Input    | Cell pin 11 input. Terminate to LPF resistor.                                                          |

| 13     | CT_10      | Input    | Cell pin 10 input. Terminate to LPF resistor.                                                          |

| 14     | CB_10      | Output   | Cell balance driver. Terminate to cell 10 cell balance load resistor.                                  |

| 15     | CB_10:9_C  | Output   | Cell balance 10:9 common. Terminate to CB_10:9_C balance load resistor.                                |

| 16     | CB_9       | Output   | Cell balance driver. Terminate to cell 9 cell balance load resistor.                                   |

| 17     | CT_9       | Input    | Cell pin 9 input. Terminate to LPF resistor.                                                           |

| 18     | CT_8       | Input    | Cell pin 8 input. Terminate to LPF resistor.                                                           |

| 19     | CB_8       | Output   | Cell balance driver. Terminate to cell 8 cell balance load resistor.                                   |

| 20     | CB_8:7_C   | Output   | Cell balance 8:7 common. Terminate to CB_8:7_C balance load resistor.                                  |

| 21     | CB_7       | Output   | Cell balance driver. Terminate to cell 7 cell balance load resistor.                                   |

| 22     | CT_7       | Input    | Cell pin 7 input. Terminate to LPF resistor.                                                           |

| 23     | CT_6       | Input    | Cell pin 6 input. Terminate to LPF resistor.                                                           |

| 24     | CB_6       | Output   | Cell balance driver. Terminate to cell 6 cell balance load resistor.                                   |

| 25     | CB_6:5_C   | Output   | Cell balance 6:5 common. Terminate to CB_6:5_C balance load resistor.                                  |

| 26     | CB_5       | Output   | Cell balance driver. Terminate to cell 5 cell balance load resistor.                                   |

| 27     | CT_5       | Input    | Cell pin 5 input. Terminate to LPF resistor.                                                           |

| 28     | CT_4       | Input    | Cell pin 4 input. Terminate to LPF resistor.                                                           |

| 29     | CB_4       | Output   | Cell balance driver. Terminate to cell 4 cell balance load resistor.                                   |

| 30     | CB_4:3_C   | Output   | Cell balance 4:3 common. Terminate to CB_4:3_C balance load resistor.                                  |

| 31     | CB_3       | Output   | Cell balance driver. Terminate to cell 3 cell balance load resistor.                                   |

| 32     | CT_3       | Input    | Cell pin 3 input. Terminate to LPF resistor.                                                           |

| 33     | CT_2       | Input    | Cell pin 2 input. Terminate to LPF resistor.                                                           |

| 34     | CB_2       | Output   | Cell balance driver. Terminate to cell 2 cell balance load resistor.                                   |

| 35     | CB_2:1_C   | Output   | Cell Balance 2:1 common. Terminate to CB_2:1_C balance load resistor.                                  |

| 36     | CB_1       | Output   | Cell balance driver. Terminate to cell 1 cell balance load resistor.                                   |

| 37     | CT_1       | Input    | Cell pin 1 input. Terminate to LPF resistor.                                                           |

| 38     | CT_REF     | Input    | Cell pin REF input. Terminate to LPF resistor.                                                         |

| 39     | SPI_COM_EN | Input    | SPI communication enable. Pin must be high for the SPI to be active.                                   |

| 40     | FAULT      | Output   | Fault output dependent on user defined internal or external faults. If not used, it must be left open. |

| 41     | CSB        | Input    | SPI chip select                                                                                        |

| 42     | so         | Output   | SPI serial output                                                                                      |

| 43     | VCOM       | Output   | Communication regulator output                                                                         |

14 cells battery cell controller IC

Table 3. Pin definitions...continued

| Number | Name          | Function | Definition                                                                                          |

|--------|---------------|----------|-----------------------------------------------------------------------------------------------------|

| 44     | CGND          | Ground   | Communication decoupling ground. Terminate to GNDREF.                                               |

| 45     | RDTX_OUT-     | I/O      | Receive/transmit output negative                                                                    |

| 46     | SCLK/RDTX_IN- | I/O      | SPI clock or receive/transmit input negative                                                        |

| 47     | SI/RDTX_IN+   | I/O      | SPI serial input or receive/transmit input positive                                                 |

| 48     | RDTX_OUT+     | I/O      | Receive/transmit output positive                                                                    |

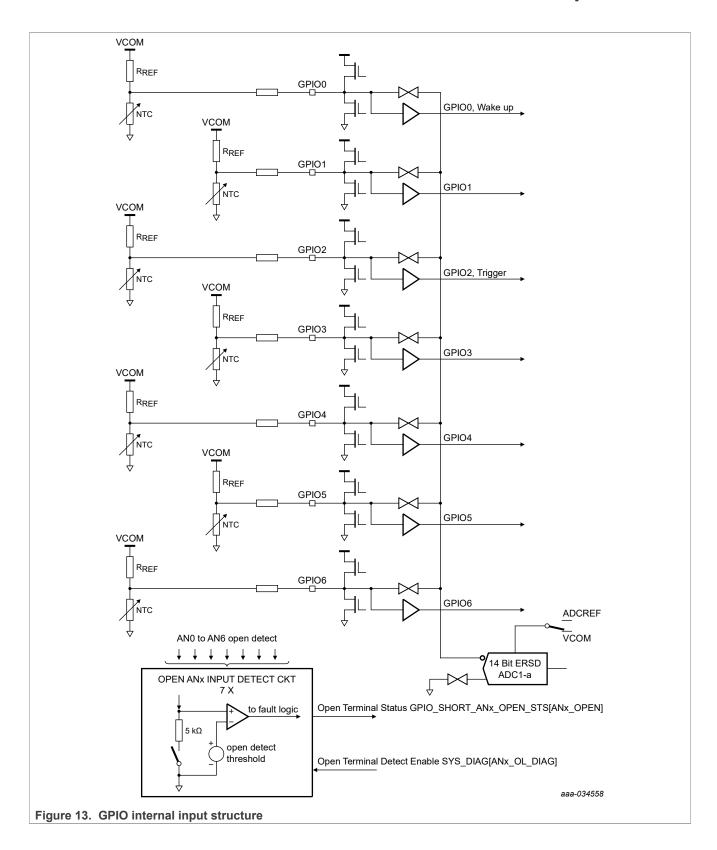

| 49     | GPIO0         | I/O      | General purpose analog input or GPIO or wake-up or fault daisy chain                                |

| 50     | GPIO1         | I/O      | General purpose analog input or GPIO                                                                |

| 51     | GPIO2         | I/O      | General purpose analog input or GPIO or conversion trigger                                          |

| 52     | GPIO3         | I/O      | General purpose analog input or GPIO                                                                |

| 53     | GPIO4         | I/O      | General purpose analog input or GPIO                                                                |

| 54     | GPIO5         | I/O      | General purpose analog input or GPIO                                                                |

| 55     | GPIO6         | I/O      | General purpose analog input or GPIO                                                                |

| 56     | GND           | Ground   | Ground                                                                                              |

| 57     | GND           | Ground   | Ground                                                                                              |

| 58     | AGND          | Ground   | Analog ground, terminate to GNDREF                                                                  |

| 59     | DGND          | Ground   | Digital ground, terminate to GNDREF                                                                 |

| 60     | VANA          | Output   | Precision ADC analog supply                                                                         |

| 61     | SCL           | I/O      | I <sup>2</sup> C clock                                                                              |

| 62     | SDA           | I/O      | I <sup>2</sup> C data                                                                               |

| 63     | RESET         | Input    | RESET is an active high input. RESET has an internal pull down. If not used, it can be tied to GND. |

| 64     | GNDREF        | Ground   | Ground reference for device. Terminate to reference of battery cluster.                             |

| 65     | GNDFLAG       | Ground   | Device flag. Terminate to lowest potential of battery cluster.                                      |

|        |               |          |                                                                                                     |

# 8 General product characteristics

## 8.1 Ratings and operating requirements relationship

The operating voltage range pertains to the VPWR pins referenced to the AGND pins.

Table 4. Ratings vs. operating requirements

| Fatal range                         | Handling range – no permanent failure                                   |                                           |                                                                                                                                           |                                     |  |  |

|-------------------------------------|-------------------------------------------------------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--|--|

| Permanent<br>failure might<br>occur | No permanent failure,     but IC functionality is not     guaranteed    | Normal operating range • 100 % functional | Upper limited operating range     IC parameters might be out of specification     Detection of V <sub>PWR</sub> overvoltage is functional | Permanent<br>failure might<br>occur |  |  |

| V <sub>PWR</sub> < -0.3 V           | 7.6 V ≤ $V_{PWR}$ < 9.6 V<br>Reset range:<br>-0.3 V ≤ $V_{PWR}$ < 7.6 V | 9.6 V ≤ V <sub>PWR</sub> ≤ 63 V           | 63 V < V <sub>PWR</sub> ≤ 75 V                                                                                                            | 75 V < V <sub>PWR</sub>             |  |  |

14 cells battery cell controller IC

In both upper and lower limited operating range, no information can be provided about IC performance. Only the detection of  $V_{PWR}$  overvoltage is guaranteed in the upper limited operating range.

Performance in normal operating range is guaranteed only if there is a minimum of seven battery cells in the stack.

#### 8.2 Maximum ratings

Table 5. Maximum ratings

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Symbol                                                                              | Description (rating)                                            | Min  | Max           | Unit |

|-------------------------------------------------------------------------------------|-----------------------------------------------------------------|------|---------------|------|

| Electrical ratings                                                                  |                                                                 |      |               |      |

| VPWR1, VPWR2                                                                        | Supply input voltage                                            | -0.3 | 75            | V    |

| CT14                                                                                | Cell terminal voltage                                           | -0.3 | 75            | V    |

| VPWR to CT14                                                                        | Voltage across VPWR1,2 pins pair and CT14 pin                   | -10  | 10.5          | V    |

| CT <sub>N</sub> to CT <sub>N-1</sub>                                                | Cell terminal differential voltage [1]                          | -0.3 | 6.0           | V    |

| CT <sub>REF</sub> to GND                                                            | Cell terminal reference to ground                               | _    | 5             | V    |

| CT <sub>N</sub> to GND                                                              | Cell terminal voltage to ground (N = 1 to 4 or N = 6 to 14)     | _    | (N+1) * 5     | V    |

|                                                                                     | Cell terminal voltage to ground (N = 5)                         | _    | 27.5          | V    |

| CT <sub>N(CURRENT)</sub>                                                            | Cell terminal input current                                     | _    | ±500          | μΑ   |

| CB <sub>N</sub> to CB <sub>N:N-1_C</sub> CB <sub>N:N-1_C</sub> to CB <sub>N-1</sub> | Cell balance differential voltage                               | _    | 10            | V    |

| CB <sub>2n</sub> to GND                                                             | Cell balance voltage to GND (n = 1 to 7)                        | _    | (2n+1) . 5    | V    |

| CB <sub>2n+1</sub> to GND                                                           | Cell balance voltage to GND (n = 0 to 6)                        | _    | (2n+1) . 5    | V    |

| CB <sub>2n:2n-1_C</sub> to GND                                                      | Cell balance voltage to GND (n = 1 to 6)                        | _    | 2n . 5        | V    |

| CB <sub>N:N-1_C</sub> to CTn-1                                                      | Cell balance input to cell terminal input                       | -10  | 10            | V    |

| VCOM                                                                                | Maximum voltage may be applied to VCOM pin from external source | _    | 5.8           | V    |

| VANA                                                                                | Maximum voltage may be applied to VANA pin                      | _    | 3.1           | V    |

| V <sub>GPIO0</sub>                                                                  | GPIO0 pin voltage                                               | -0.3 | 6.5           | V    |

| V <sub>GPIOx</sub>                                                                  | GPIOx pins (x = 1 to 6) voltage                                 | -0.3 | VCOM<br>+ 0.5 | V    |

| V <sub>DIG</sub>                                                                    | Voltage I <sup>2</sup> C pins (SDA, SCL)                        | -0.3 | VCOM<br>+ 0.5 | V    |

| V <sub>RESET</sub>                                                                  | RESET pin                                                       | -0.3 | 6.5           | V    |

| V <sub>CSB</sub>                                                                    | CSB pin                                                         | -0.3 | 6.5           | V    |

| V <sub>SPI_COMM_EN</sub>                                                            | SPI_COMM_EN                                                     | -0.3 | 6.5           | V    |

| V <sub>SO</sub>                                                                     | SO pin                                                          | -0.3 | VCOM<br>+ 0.5 | V    |

| FAULT                                                                               | Maximum applied voltage to pin                                  | -0.3 | 7.0           | V    |

| I <sub>pin_unpowered</sub>                                                          | Input current in a pin when the device is unpowered             | -2   | 2             | mA   |

14 cells battery cell controller IC

Table 5. Maximum ratings...continued

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Symbol            | Description (rating)                                                                                                                                                                                                                                                                                                      | Min              | Max                                  | Unit |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------|------|

| V <sub>COMM</sub> | Maximum voltage to pins RDTX_OUT+, RDTX_OUT-, SI/RDTX_IN+, SCLK/RDTX_IN-                                                                                                                                                                                                                                                  | -10.0            | 10.0                                 | V    |

| V <sub>ESD1</sub> | ESD voltage Human body model (HBM) Charge device model (CDM) Charge device model corner pins (CDM)                                                                                                                                                                                                                        | _<br>_<br>_      | ±2000<br>±500 <sup>[2]</sup><br>±750 | V    |

| V <sub>ESD2</sub> | ESD voltage (VPWR1, VPWR2, CTx, CBx, GPIOx, RDTX_OUT+, RDTX_OUT-, SI/RDTX_IN+, SCLK/RDTX_IN-) versus all ground pins  Human body model (HBM)                                                                                                                                                                              | _                | ±4000                                | V    |

| V <sub>ESD3</sub> | ESD voltage (CTREF, CTx, CBx, GPIOx, RDTX_OUT+, RDTX_OUT-, SI/RDTX_IN+, SCLK/ RDTX_IN-) IEC 61000-4-2, Unpowered (Gun configuration: 330Ω / 150pF) HMM, Unpowered (Gun configuration: 330Ω / 150pF) ISO 10605:2009, Unpowered (Gun configuration: 2 kΩ / 150pF) ISO 10605:2009, Powered (Gun configuration: 2 kΩ / 150pF) | _<br>_<br>_<br>_ | ±8000<br>±8000<br>±8000<br>±8000     | V    |

Adjacent CT pins may experience an overvoltage that exceeds their maximum rating during OV/UV functional verification test or during open line diagnostic test. Nevertheless, the IC is completely tolerant to this special situation. For CT\_REF pin applicable limit is ±450 V.

## 8.3 Thermal characteristics

Table 6. Thermal ratings

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Symbol                 | Description (rating)                                                        |        | Min | Max  | Unit |

|------------------------|-----------------------------------------------------------------------------|--------|-----|------|------|

| Thermal ratin          | ngs                                                                         |        |     |      |      |

| TJ                     | Operating temperature  Junction <sup>[1]</sup>                              |        | -40 | +150 | °C   |

| T <sub>STG</sub>       | Storage temperature                                                         |        | -55 | +150 | °C   |

| T <sub>PPRT</sub>      | Peak package reflow temperature                                             | [2][3] | _   | 260  | °C   |

| Thermal resi           | stance and package dissipation ratings                                      |        |     |      | •    |

| R <sub>OJB</sub>       | Junction-to-board (bottom exposed pad soldered to board) 64 LQFP EP         | [4]    | _   | 10   | °C/W |

| R <sub>OJA</sub>       | Junction-to-ambient, natural convection, single-layer board (1s) 64 LQFP EP | [5][6] | _   | 59   | °C/W |

| R <sub>OJA</sub>       | Junction-to-ambient, natural convection, four-layer board (2s2p) 64 LQFP EP | [5][6] | _   | 27   | °C/W |

| R <sub>OJCTOP</sub>    | Junction-to-case top (exposed pad) 64 LQFP EP                               | [7]    | _   | 14   | °C/W |

| R <sub>OJCBOTTOM</sub> | Junction-to-case bottom (exposed pad) 64 LQFP EP                            | [8]    | _   | 0.97 | °C/W |

| $\Psi_{JT}$            | Junction to package top, natural convection                                 | [9]    | _   | 3    | °C/W |

<sup>[1]</sup> The user must ensure that the average maximum operating junction temperature (TJ) is not exceeded.

All information provided in this document is subject to legal disclaimers.

© 2024 NXP B.V. All rights reserved.

ESD testing is performed in accordance with the human body model (HBM) ( $C_{ZAP} = 100$  pF,  $R_{ZAP} = 1500$   $\Omega$ ), and the charge device model (CDM) ( $C_{ZAP} = 100$  pF,  $C_{ZAP} = 100$ [3] 4.0 pF).

These voltage values can be sustained only if ESD caps are used as described in Section 12.2

#### 14 cells battery cell controller IC

- [2] Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause a malfunction or permanent damage to the device.

- [3] NXP's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL), go to <a href="https://www.nxp.com">www.nxp.com</a>, search by part number (remove prefixes/suffixes) and enter the core ID to view all orderable parts and review parametrics.

- [4] Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- [5] Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- [6] Per JEDEC JESD51-6 with the board (JESD51-7) horizontal.

- Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1), with the cold plate temperature used for the case temperature.

- [8] Thermal resistance between the die and the solder pad on the bottom of the package based on simulation without any interface resistance.

- [9] Thermal characterization parameter indicating the temperature difference between the package top and the junction temperature per JEDEC JESD51-2.

#### 8.4 Electrical characteristics

#### Table 7. Static and dynamic electrical characteristics

| Symbol                    | Parameter                                                                                                                                                                                                         | Min                  | Тур    | Max               | Unit |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------|-------------------|------|

| Power manageme            | ent                                                                                                                                                                                                               |                      |        |                   |      |

| V <sub>PWR(FO)</sub>      | Supply voltage Full parameter specification                                                                                                                                                                       | 9.6                  | _      | 63                | V    |

|                           | Supply current (base value)  Normal mode, cell balance OFF, ADC inactive, SPI communication inactive, IVCOM = 0 mA                                                                                                | _                    | 5.4    | 8.5               | mA   |

| IVPWR                     | Normal mode, cell balance OFF, ADC inactive, TPL communication inactive, IVCOM = 0 mA                                                                                                                             | _                    | 8.0    | 10.0              | IIIA |

| I <sub>VPWR(TPL_TX)</sub> | Supply current adder when TPL communication active                                                                                                                                                                | _                    | _      | 16                | mA   |

| I <sub>VPWR(CBON)</sub>   | Supply current adder to set all 14 cell balance switches ON                                                                                                                                                       | _                    | 0.97   | _                 | mA   |

| I <sub>VPWR(ADC)</sub>    | Delta supply current to perform ADC conversions (addend)  ADC1-A,B continuously converting                                                                                                                        | _                    | 3.0    | 5.0               | mA   |

|                           | Supply current in sleep mode and in idle mode, communication inactive, cell balance off, cyclic measurement off, oscillator monitor on                                                                            |                      |        |                   |      |

|                           | SPI mode ( $T_A = 25$ °C)<br>SPI mode ( $T_A = -20$ °C to 60 °C) BMI7014TA1                                                                                                                                       | _                    | 40     | _                 |      |

| I <sub>VPWR(SS)</sub>     | SPI mode ( $T_A = -20 \text{ °C to 60 °C}$ ) BMI7014TA1<br>SPI mode ( $T_A = -20 \text{ °C to 60 °C}$ ) BMI7014TA2                                                                                                | _                    | _      | 75<br>110         | μA   |

|                           | TPL mode ( $T_A = 25 ^{\circ}\text{C}$ ) TPL mode ( $T_A = -20 ^{\circ}\text{C}$ to 60 $^{\circ}\text{C}$ )                                                                                                       | 64<br>54             | _<br>_ | 108<br>115        |      |

| I <sub>VPWR(CKMON)</sub>  | Clock monitor current consumption                                                                                                                                                                                 | _                    | 5      | 8                 | μA   |

| V <sub>VPWR_CT</sub>      | Voltage drop across CT14 and VPWR without accuracy degradation $3.0 \text{ V} \leq \text{V}_{\text{CELL}} \\ 2.5 \text{ V} \leq \text{V}_{\text{CELL}} < 3.0 \text{ V} \\ \text{V}_{\text{CELL}} < 2.5 \text{ V}$ | -3.0<br>-2.0<br>-1.5 |        | 3.0<br>2.0<br>1.5 | V    |

| V <sub>PWR(OV_FLAG)</sub> | V <sub>PWR</sub> overvoltage fault threshold (flag)                                                                                                                                                               | 63                   | 65     | 68                | V    |

| V <sub>PWR(LV_FLAG)</sub> | V <sub>PWR</sub> low-voltage warning threshold (flag)                                                                                                                                                             | 11.7                 | 12     | 12.3              | V    |

| V <sub>PWR(UV_POR)</sub>  | V <sub>PWR</sub> undervoltage shutdown threshold (POR)                                                                                                                                                            | 7.6                  | 8.5    | 9.6               | V    |

| V <sub>PWR(HYS)</sub>     | V <sub>PWR</sub> UV hysteresis voltage                                                                                                                                                                            | 100                  | 200    | _                 | mV   |

| t <sub>VPWR(FILTER)</sub> | V <sub>PWR</sub> OV, LV filter                                                                                                                                                                                    |                      | 50     | _                 | μs   |

14 cells battery cell controller IC

Table 7. Static and dynamic electrical characteristics...continued

| Symbol                          | Parameter                                                                                            | Min  | Тур                 | Max  | Unit   |

|---------------------------------|------------------------------------------------------------------------------------------------------|------|---------------------|------|--------|

| VCOM power supply               |                                                                                                      |      |                     |      |        |

| V <sub>COM</sub>                | VCOM output voltage                                                                                  | 4.9  | 5.0                 | 5.2  | V      |

| I <sub>VCOM</sub>               | VCOM output current allocated for external use                                                       | _    | _                   | 5.0  | mA     |

| V <sub>COM(UV)</sub>            | VCOM undervoltage fault threshold                                                                    | 4.2  | 4.4                 | 4.6  | V      |

| V <sub>COM_HYS</sub>            | VCOM undervoltage hysteresis                                                                         | _    | 100                 | _    | mV     |

| t <sub>VCOM(FLT_TIMER)</sub>    | VCOM undervoltage fault timer                                                                        | _    | 10                  | _    | μs     |

| t <sub>VCOM(RETRY)</sub>        | VCOM fault retry timer                                                                               | _    | 10                  | _    | ms     |

| V <sub>COM(OV)</sub>            | VCOM overvoltage fault threshold                                                                     | 5.4  | _                   | 5.9  | V      |

| I <sub>LIM_VCOM(OC)</sub>       | VCOM current limit                                                                                   | 65   | _                   | 140  | mA     |

| R <sub>VCOM(SS)</sub>           | VCOM sleep mode pulldown resistor                                                                    | 1.0  | 2.0                 | 5.0  | kΩ     |

| t <sub>VCOM</sub>               | VCOM rise time (for $V_{PWR}$ > 10V and CL = 2.2 $\mu F$ (ceramic X7R only) in parallel with 220 pF) | _    | _                   | 440  | μs     |

| VANA power supply               |                                                                                                      |      |                     |      |        |

| V <sub>ANA</sub>                | VANA output voltage (not used by external circuits) Decouple with 47 nF X7R 0603 or 0402             | 2.6  | 2.65                | 2.7  | V      |

| V <sub>ANA(UV)</sub>            | VANA undervoltage fault threshold                                                                    | 2.28 | 2.4                 | 2.5  | V      |

| V <sub>ANA_HYS</sub>            | VANA undervoltage hysteresis                                                                         | _    | 50                  | _    | mV     |

| V <sub>ANA(FLT_TIMER)</sub>     | VANA undervoltage fault timer                                                                        | _    | 11                  | _    | μs     |

| V <sub>ANA(OV)</sub>            | VANA overvoltage fault threshold                                                                     | 2.77 | 2.8                 | 2.85 | V      |

| t <sub>VANA(RETRY)</sub>        | VANA fault retry timer                                                                               | _    | 10                  | _    | ms     |

| I <sub>LIM_VANA(OC)</sub>       | VANA current limit                                                                                   | 5.0  | _                   | 10   | mA     |

| R <sub>VANA_RPD</sub>           | VANA sleep mode pulldown resistor                                                                    | _    | 1.0                 | _    | kΩ     |

| t <sub>VANA</sub>               | VANA rise time (CL = 47 nF ceramic X7R only) [4]                                                     | _    | _                   | 400  | μs     |

| ADC1-A, ADC1-B                  |                                                                                                      |      |                     |      | I      |

| CTn <sub>(LEAKAGE)</sub>        | Cell terminal input leakage current (except in Sleep mode when cell balancing is ON)                 | _    | 10                  | 100  | nA     |

| CTn <sub>(FV)</sub>             | Cell terminal input current - functional verification                                                | _    | 0.365               | 0.5  | mA     |

| CT <sub>N</sub>                 | Cell terminal input current during conversion                                                        | _    | 50                  | _    | nA     |

| R <sub>PD</sub>                 | Cell terminal open load detection pulldown resistor                                                  | 850  | 950                 | 1250 | Ω      |

| V <sub>VPWR_RES</sub>           | VPWR terminal measurement resolution                                                                 | _    | 2.44141             | _    | mV/LSB |

| V <sub>VPWR_RNG</sub>           | VPWR terminal measurement range                                                                      | 9.6  | _                   | 75   | V      |

| VPWR <sub>TERM_ERR</sub>        | VPWR terminal measurement accuracy                                                                   | -0.5 | _                   | 0.5  | %      |

| V <sub>CT_RNG</sub>             | ADC differential input voltage range for CTn to CTn-1 [5]                                            | 0.0  | _                   | 4.85 | V      |

| V <sub>CT_ANx_RES</sub>         | Cell voltage and ANx resolution in 15-bit MEAS_xxxx registers                                        | _    | 152.58789           | _    | μV/LSB |

| V <sub>ANx_RATIO_RES</sub>      | ANx resolution in 15-bit MEAS_xxxx registers in ratiometric mode                                     | _    | VCOM.<br>(30.51758) | _    | μV/LSB |

| V <sub>ERR33RT_BMI7014TA1</sub> | Cell voltage measurement error V <sub>CELL</sub> = 3.3 V, T <sub>A</sub> = 25 °C                     | -0.8 | ±0.4                | 0.8  | mV     |

|                                 | Cell voltage measurement error [6][7]                                                                |      |                     |      | mV     |

14 cells battery cell controller IC

Table 7. Static and dynamic electrical characteristics...continued

| Symbol                                    | Parameter                                                                                                                                                                                                                                                                           |           | Min                | Тур                            | Max                  | Unit  |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------------|--------------------------------|----------------------|-------|

| V <sub>ERR_1_BMI7014TA1</sub>             | Cell voltage measurement error<br>0.1 V ≤ V <sub>CELL</sub> ≤ 4.3 V, −20 °C ≤ T <sub>J</sub> ≤ 85 °C                                                                                                                                                                                | [6][7][8] | -3.0               | ±1.0                           | 3.0                  | mV    |

| V <sub>ERR_1_BMI7014TA2</sub>             | Cell voltage measurement error 0.1 V ≤ V <sub>CELL</sub> ≤ 4.3 V , -20 °C ≤ Tj ≤ 85 °C                                                                                                                                                                                              | [6][7][8] | -9.0               | _                              | 9.0                  | mV    |

| V <sub>ERR_2_BMI7014TA2</sub>             | Cell voltage measurement error 0.1 V ≤ V <sub>CELL</sub> ≤ 3.7 V , 0 °C ≤ Tj ≤ 65 °C                                                                                                                                                                                                | [6][7][8] | -5.0               | _                              | 5.0                  | mV    |

| V <sub>ERR_A_BMI7014TA1</sub>             | Cell voltage measurement error after aging, 0.1 V ≤ V <sub>CELL</sub> ≤ 4.3 V, −20 °C ≤ T <sub>J</sub> ≤ 85 °C                                                                                                                                                                      | [6][8][9] | -5.0               | ±1.0                           | 5.0                  | mV    |

| V <sub>ANx_ERR</sub>                      | Magnitude of ANx error in the entire measurement range: Ratiometric measurement Absolute measurement after soldering and aging, input in the range [1.0, 4.5] V Absolute measurement after soldering and aging, input in the range [0, 4.85] V, for –40 °C < T <sub>A</sub> < 60 °C | [6][9]    | <br><br>           | _<br>_<br>_                    | 16<br>10<br>8.0      | mV    |

| t <sub>VCONV</sub>                        | Single channel net conversion time 13-bit resolution 14-bit resolution 15-bit resolution 16-bit resolution                                                                                                                                                                          |           | _<br>_<br>_        | 6.77<br>9.43<br>14.75<br>25.36 | _<br>_<br>_<br>_     | μs    |

| V <sub>V_NOISE</sub>                      | Conversion noise 13-bit resolution 14-bit resolution 15-bit resolution 16-bit resolution                                                                                                                                                                                            |           | _<br>_<br>_        | 1800<br>1000<br>600<br>400     | _<br>_<br>_<br>_     | μVrms |

| ADC <sub>CLK</sub>                        | ADC1-A,B clocking frequency                                                                                                                                                                                                                                                         |           | 5.7                | 6.0                            | 6.3                  | MHz   |

| Diagnostic threshole                      | ds                                                                                                                                                                                                                                                                                  |           |                    |                                |                      |       |

| V <sub>OL_DETECT</sub>                    | Cell terminal open load V detection threshold $1.5 \text{ V} \leq \text{V}_{\text{CELL}} \leq 2.7 \text{ V}$ $2.5 \text{ V} \leq \text{V}_{\text{CELL}} \leq 3.7 \text{ V}$ $2.5 \text{ V} \leq \text{V}_{\text{CELL}} \leq 4.3 \text{ V}$                                          | [10]      | _<br>_<br>_        | 50<br>100<br>150               | _<br>_<br>_          | mV    |

| V <sub>LEAK</sub>                         | Cell terminal leakage detection level                                                                                                                                                                                                                                               | [6]       | -27                | _                              | 27                   | mV    |

| V <sub>REF_ZD</sub>                       | Precision diagnostic Zener reference for cell voltage channel functional verification                                                                                                                                                                                               | [6]       | 4.45               | 4.6                            | 4.85                 | V     |

| V <sub>CVFV</sub>                         | Cell voltage channel functional verification allowable error in CT verification measurement                                                                                                                                                                                         | [6]       | -22                | _                              | 6.0                  | mV    |

| V <sub>BGP</sub>                          | Voltage reference used in ADC1-A,B functional verification                                                                                                                                                                                                                          |           | _                  | 1.18                           | _                    | V     |

| ADC1a <sub>FV</sub> , ADC1b <sub>FV</sub> | ADC1-A and ADC1-B functional verification  Maximum tolerance between ADC1-A, B and diagnostic reference (1.5 V ≤ V <sub>CELL</sub> ≤ 4.3 V)                                                                                                                                         |           | -5.25              | _                              | 5.25                 | mV    |

| CTx_UV_TH                                 | Undervoltage functional verification threshold in Diagnostic mode  1.5 V ≤ V <sub>CELL</sub> ≤ 2.7 V  2.5 V ≤ V <sub>CELL</sub> ≤ 3.7 V  2.5 V ≤ V <sub>CELL</sub> ≤ 4.3 V                                                                                                          | [10]      | 390<br>650<br>1200 | _<br>_<br>_                    | _<br>_<br>_          | mV    |

| CTx_OV_TH                                 | Overvoltage functional verification threshold in Diagnostic mode<br>1.5 V $\leq$ V <sub>CELL</sub> $\leq$ 2.7 V<br>2.5 V $\leq$ V <sub>CELL</sub> $\leq$ 3.7 V<br>2.5 V $\leq$ V <sub>CELL</sub> $\leq$ 4.3 V                                                                       | [10]      | _<br>_<br>_        | _<br>_<br>_                    | 1800<br>4000<br>4000 | mV    |

14 cells battery cell controller IC

Table 7. Static and dynamic electrical characteristics...continued

Characteristics noted under conditions 9.6 V  $\leq$  V<sub>PWR</sub>  $\leq$  63 V, -20 °C  $\leq$  T<sub>J</sub>  $\leq$  85 °C, GND = 0 V, unless otherwise stated. Typical values refer to V<sub>PWR</sub> = 56 V, T<sub>A</sub> = 25 °C, unless otherwise noted.

| Symbol                    | Parameter                                                                                                                                                                                        | Min  | Тур             | Max            | Unit   |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------|----------------|--------|

| Cell balance driver       | s                                                                                                                                                                                                |      |                 |                |        |

| V <sub>DS(CLAMP)</sub>    | Cell balance driver VDS active clamp voltage                                                                                                                                                     | 10   | 11              | 12             | V      |

| V <sub>OUT(FLT_TH)</sub>  | Output fault detection voltage threshold Balance off (open load) Balance on (shorted load)                                                                                                       | 0.3  | 0.55            | 0.75           | V      |

| R <sub>PD_CB</sub>        | Output OFF open load detection pulldown resistor Balance off, open load detect disabled                                                                                                          | 1.7  | 2.0             | 2.9            | kΩ     |

| I <sub>OUT(LKG)</sub>     | Output leakage current  Balance off, open load detect disabled at V <sub>DS</sub> = 4.0 V                                                                                                        | _    | _               | 1.0            | μА     |

| R <sub>DS(on)</sub>       | Drain-to-source on resistance $I_{OUT} = 300 \text{ mA}, T_J = 85 ^{\circ}\text{C}$ $I_{OUT} = 300 \text{ mA}, T_J = 25 ^{\circ}\text{C}$ $I_{OUT} = 300 \text{ mA}, T_J = -20 ^{\circ}\text{C}$ |      | —<br>0.5<br>0.4 | 0.80<br>—<br>— | Ω      |

| I <sub>LIM_CB</sub>       | Driver current limitation                                                                                                                                                                        | 310  | _               | 950            | mA     |

| t <sub>ON</sub>           | Cell balance driver turn on $R_L = 15 \Omega$                                                                                                                                                    | _    | 350             | 450            | μs     |

| t <sub>OFF</sub>          | Cell balance driver turn off $R_L = 15 \Omega$                                                                                                                                                   | _    | 200             | _              | μs     |

| t <sub>BAL_DEGLICTH</sub> | Short/open detect filter time                                                                                                                                                                    | 19   | 20              | 42.1           | μs     |

| Internal temperatur       | re measurement                                                                                                                                                                                   |      |                 |                |        |

| IC_TEMP1_ERR              | IC temperature measurement error                                                                                                                                                                 | -3.0 | _               | 3.0            | K      |

| IC_TEMP1_RES              | IC temperature resolution                                                                                                                                                                        | _    | 0.032           | _              | K/LSB  |

| TSD_TH                    | Thermal shutdown                                                                                                                                                                                 | 155  | 170             | 185            | °C     |

| TSD_HYS                   | Thermal shutdown hysteresis                                                                                                                                                                      | 5.0  | 10              | 12.2           | °C     |

| Default operational       | parameters                                                                                                                                                                                       |      |                 |                |        |

| V <sub>CTOV(TH)</sub>     | Cell overvoltage threshold (8 bits), typical value is default value after RESET                                                                                                                  | 0.0  | 4.2             | 5.0            | V      |

| V <sub>CTOV(RES)</sub>    | Cell overvoltage threshold resolution                                                                                                                                                            | _    | 19.53125        | _              | mV/LSB |

| V <sub>CTUV(TH)</sub>     | Cell undervoltage threshold (8 bits), typical value is default value after RESET                                                                                                                 | 0.0  | 2.5             | 5.0            | V      |

| V <sub>CTUV(RES)</sub>    | Cell undervoltage threshold resolution                                                                                                                                                           | _    | 19.53125        | _              | mV/LSB |

| V <sub>GPIO_OT(TH)</sub>  | GPIOx configured as ANx input overtemperature threshold after RESET                                                                                                                              | _    | 1.16            | _              | V      |

| $V_{GPIO\_OT(RES)}$       | Temperature voltage threshold resolution                                                                                                                                                         | _    | 4.8828125       | _              | mV/LSB |

| V <sub>GPIO_UT(TH)</sub>  | GPIOx configured as ANx input undertemperature threshold after RESET                                                                                                                             | _    | 3.82            | _              | V      |

| V <sub>GPIO_UT(RES)</sub> | Temperature voltage threshold resolution                                                                                                                                                         |      | 4.8828125       | _              | mV/LSB |

| General purpose in        | •                                                                                                                                                                                                |      |                 |                |        |

| V <sub>IH</sub>           | Input high-voltage (3.3 V compatible) [11]                                                                                                                                                       | 2.0  |                 |                | V      |

| V <sub>IL</sub>           | Input low-voltage (3.3 V compatible) [11]                                                                                                                                                        | _    | _               | 1.0            | V      |

| V <sub>HYS</sub>          | Input hysteresis [11]                                                                                                                                                                            | _    | 100             | _              | mV     |

| I <sub>IL</sub>           | Input leakage current Pins tristate, V <sub>IN</sub> = V <sub>COM</sub> or AGND                                                                                                                  | -100 | _               | 100            | nA     |

BMI7014

All information provided in this document is subject to legal disclaimers.

14 cells battery cell controller IC

Table 7. Static and dynamic electrical characteristics...continued

Characteristics noted under conditions 9.6 V  $\leq$  V<sub>PWR</sub>  $\leq$  63 V, -20 °C  $\leq$  T<sub>J</sub>  $\leq$  85 °C, GND = 0 V, unless otherwise stated. Typical values refer to V<sub>PWR</sub> = 56 V, T<sub>A</sub> = 25 °C, unless otherwise noted.

| Symbol                     | Parameter                                                                                                                    | Min                       | Тур  | Max              | Unit |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------|---------------------------|------|------------------|------|

| V <sub>OH</sub>            | Output high-voltage I <sub>OH</sub> = −0.5 mA                                                                                | V <sub>COM</sub><br>- 0.8 | _    | _                | V    |

| V <sub>OL</sub>            | Output low-voltage I <sub>OL</sub> = +0.5 mA                                                                                 | _                         | _    | 0.8              | V    |

| V <sub>ADC</sub>           | Analog ADC input voltage range for ratiometric measurements                                                                  | AGND                      | _    | V <sub>COM</sub> | V    |

| V <sub>OL(TH)</sub>        | Analog input open pin detect threshold                                                                                       | 0.1                       | 0.15 | 0.23             | V    |

| R <sub>OPENPD</sub>        | Internal open detection pulldown resistor [12]                                                                               | 3.8                       | 5.0  | 6.2              | kΩ   |

| t <sub>GPIO0_WU</sub>      | GPIO0 WU de-glitch filter                                                                                                    | 47                        | 50   | 85               | μs   |

| t <sub>GPIO0_FLT</sub>     | GPIO0 daisy chain de-glitch filter both edges                                                                                | 19                        | 20   | 48               | μs   |

| t <sub>GPIO2_SOC</sub>     | GPIO2 convert trigger de-glitch filter                                                                                       | 1.9                       | 2.0  | 2.1              | μs   |

| t <sub>GPIOx_DIN</sub>     | GPIOx configured as digital input de-glitch filter                                                                           | 2.5                       | _    | 5.6              | μs   |

| Reset input                |                                                                                                                              |                           | 1    | '                | '    |

| V <sub>IH_RST</sub>        | Input high-voltage (3.3 V compatible)                                                                                        | 2.0                       | _    | _                | V    |

| V <sub>IL_RST</sub>        | Input low-voltage (3.3 V compatible)                                                                                         | _                         | _    | 1.0              | V    |

| V <sub>HYS</sub>           | Input hysteresis                                                                                                             | _                         | 0.6  | _                | V    |

| t <sub>RESETFLT</sub>      | RESET de-glitch filter                                                                                                       | _                         | 100  | _                | μs   |

| R <sub>RESET_PD</sub>      | Input logic pull down (RESET)                                                                                                | _                         | 100  | _                | kΩ   |

| SPI_COM_EN inpu            | ut .                                                                                                                         |                           |      | 1                |      |

| V <sub>IH</sub>            | Input high-voltage (3.3 V compatible)                                                                                        | 2.0                       | _    | _                | V    |

| V <sub>IL</sub>            | Input low-voltage (3.3 V compatible)                                                                                         | _                         | _    | 1.0              | V    |

| V <sub>HYS</sub>           | Input hysteresis                                                                                                             | _                         | 450  | _                | mV   |

| R <sub>SPI_COM_EN_PD</sub> | Input pulldown resistor (SPI_COM_EN)                                                                                         | _                         | 100  | _                | kΩ   |

| Digital interface          |                                                                                                                              |                           |      |                  | ı    |

| V <sub>FAULT_HA</sub>      | FAULT output (high active, IOH = 1.0 mA)                                                                                     | 4.0                       | 4.9  | 6.0              | V    |

| I <sub>FAULT_CL</sub>      | FAULT output current limit                                                                                                   | 3.0                       | _    | 40               | mA   |

| R <sub>FAULT_PD</sub>      | FAULT output pulldown resistance                                                                                             | _                         | 100  | _                | kΩ   |

| V <sub>IH_COMM</sub>       | Voltage threshold to detect the input as high SI/RDTX_IN+, SCLK/RDTX_IN-, CSB, SDA, SCL (NOTE: needs to be 3.3 V compatible) | _                         | _    | 2.0              | V    |

| V <sub>IL_COMM</sub>       | Voltage threshold to detect the input as low SI/RDTX_IN+, SCLK/RDTX_IN-, CSB, SDA, SCL                                       | 0.8                       | _    | _                | V    |

| V <sub>HYS</sub>           | Input hysteresis SI/RDTX_IN+, SCLK/RDTX_IN-, CSB, SDA, SCL                                                                   | 30                        | 80   | 130              | mV   |

| I <sub>LOGIC_SS</sub>      | Sleep state input logic current CSB                                                                                          | -100                      | _    | 100              | nA   |

| R <sub>SCLK_PD</sub>       | Input logic pulldown resistance (SCLK/RDTX_IN-, SI/RDTX_IN+)                                                                 |                           | 20   |                  | kΩ   |

| R <sub>I_PU</sub>          | Input logic pullup resistance to V <sub>COM</sub> (CSB, SDA, SCL)                                                            |                           | 100  | _                | kΩ   |

| I <sub>SO_TRI</sub>        | Tristate SO input current 0 V to V <sub>COM</sub>                                                                            | -2.0                      | _    | 2.0              | μΑ   |

| V <sub>SO_HIGH</sub>       | SO high-state output voltage with I <sub>SO(HIGH)</sub> = −2.0 mA                                                            | V <sub>COM</sub><br>- 0.4 | _    | _                | V    |

| V <sub>SO_LOW</sub>        | SO, SDA, SLK low-state output voltage with I <sub>SO(HIGH)</sub> = −2.0 mA                                                   | _                         | _    | 0.4              | V    |

| CSB <sub>WU_FLT</sub>      | CSB wake-up de-glitch filter, low to high transition                                                                         |                           | _    | 80               | μs   |

BMI7014

14 cells battery cell controller IC

Table 7. Static and dynamic electrical characteristics...continued

| Symbol                   | Parameter                                                                                                                                       | Min   | Тур   | Max   | Unit |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|------|

| System timing            |                                                                                                                                                 |       |       |       |      |

|                          | Time needed to acquire all 14 cell voltages after an on-demand conversion [13]                                                                  |       |       |       |      |

| •                        | 13-bit resolution                                                                                                                               | 56    | 59    | 62    |      |

| tCELL_CONV               | 14-bit resolution                                                                                                                               | 76    | 80    | 84    | μs   |

|                          | 15-bit resolution                                                                                                                               | 117   | 123   | 129   |      |

|                          | 16-bit resolution                                                                                                                               | 197   | 208   | 218   |      |

| t <sub>VPWR(READY)</sub> | Time after VPWR connection for the IC to be ready for initialization                                                                            | _     | _     | 5.0   | ms   |

| t <sub>WAKE-UP</sub>     | Power up duration                                                                                                                               | _     | _     | 440   | μs   |

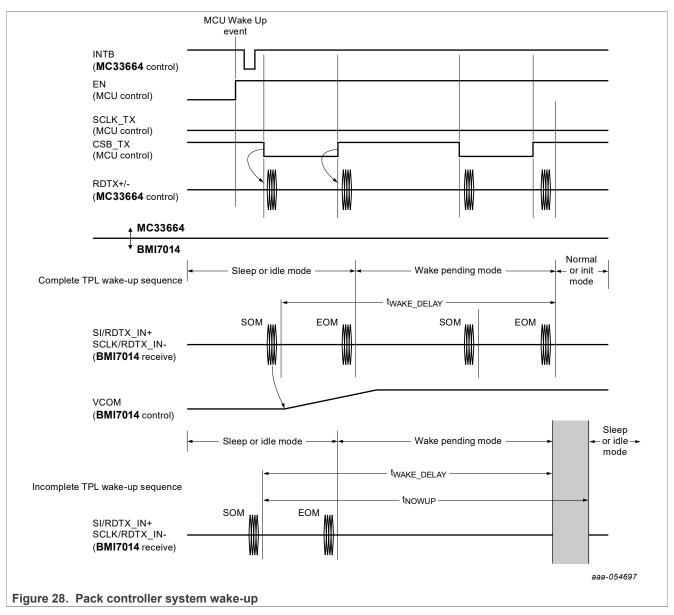

| t <sub>WAKE_DELAY</sub>  | Time between wake pulses                                                                                                                        | 500   | 600   | 700   | μs   |

| t <sub>NOWUP</sub>       | Time, starting from the first SOM received, to go back to Sleep/Idle mode time after receiving incomplete TPL bus wake-up sequence              | _     | _     | 1.3   | ms   |

| t <sub>IDLE</sub>        | Idle timeout after POR                                                                                                                          | 57    | 60    | 64    | s    |

| t <sub>BALANCE</sub>     | Cell balance timer range                                                                                                                        | 0.5   | _     | 511   | min  |

| t <sub>CYCLE</sub>       | Cyclic acquisition timer range                                                                                                                  | 0.0   | _     | 8.5   | s    |

| t <sub>FAULT</sub>       | Fault detection to activation of fault pin  Normal mode                                                                                         | _     | _     | 56    | μs   |

| t <sub>DIAG</sub>        | Diagnostic mode timeout                                                                                                                         | 0.047 | 1.0   | 8.5   | s    |

|                          | SOC to data ready (includes post processing of data, ADC_ CFG[AVG] = 0)                                                                         |       |       |       |      |

|                          | 13-bit resolution                                                                                                                               | 140   | 148   | 156   |      |

| t <sub>EOC</sub>         | 14-bit resolution                                                                                                                               | 190   | 201   | 211   | μs   |

|                          | 15-bit resolution                                                                                                                               | 291   | 307   | 323   |      |

|                          | 16-bit resolution                                                                                                                               | 494   | 520   | 546   |      |

| t <sub>SETTLE</sub>      | Time after SOC to begin converting with ADC1-A,B [13]                                                                                           | 11.67 | 12.28 | 12.90 | μs   |

|                          | Time needed to send an SOC command and read back 96 cell voltages, 48 temperatures, and ADC1-A,B configured as follows (with ADC_CFG[AVG] = 0): |       |       |       |      |

| t <sub>SYS MEAS1</sub>   | 13-bit resolution                                                                                                                               | _     | 4.67  | _     | ms   |

| 313_WLA31                | 14-bit resolution                                                                                                                               | _     | 4.73  | _     |      |

|                          | 15-bit resolution                                                                                                                               | _     | 4.83  | _     |      |

|                          | 16-bit resolution                                                                                                                               | _     | 5.05  | _     |      |

|                          | Time needed to send an SOC command and read back 96 cell voltages, and ADC1-A,B configured as follows (with ADC_CFG[AVG] = 0):                  |       |       |       |      |

| t <sub>SYS_MEAS2</sub>   | 13-bit resolution                                                                                                                               | _     | 3.24  | _     | ms   |

| 575_ME/102               | 14-bit resolution                                                                                                                               | _     | 3.39  | _     |      |

|                          | 15-bit resolution                                                                                                                               | _     | 3.40  | _     |      |

|                          | 16-bit resolution                                                                                                                               | _     | 3.61  | _     |      |

14 cells battery cell controller IC

Table 7. Static and dynamic electrical characteristics...continued

Characteristics noted under conditions 9.6 V  $\leq$  V<sub>PWR</sub>  $\leq$  63 V, -20 °C  $\leq$  T<sub>J</sub>  $\leq$  85 °C, GND = 0 V, unless otherwise stated. Typical values refer to V<sub>PWR</sub> = 56 V, T<sub>A</sub> = 25 °C, unless otherwise noted.

| Symbol                    | Parameter                                                                                                                                                                                 |       | Min  | Тур   | Max      | Unit |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|----------|------|

|                           | Time needed to send an SOC command and read back 14 cell voltages, 7 temperatures, with TPL communication working at 2.0 Mbps and ADC1-A,B configured as follows (with ADC_CFG[AVG] = 0): |       |      |       |          |      |

| $t_{\text{CLST\_TPL}}$    | 13-bit resolution                                                                                                                                                                         |       | _    | 0.85  | _        | ms   |

|                           | 14-bit resolution                                                                                                                                                                         | _     | 0.90 |       |          |      |

|                           | 15-bit resolution                                                                                                                                                                         |       | _    | 1.101 | _        |      |

|                           | 16-bit resolution                                                                                                                                                                         |       | _    | 1.22  | _        |      |

|                           | Time needed to send an SOC command and read back 14 cell voltages, 7 temperatures, with SPI communication working at 4.0 Mbps and ADC1-A,B configured as follows (with ADC_CFG[AVG] = 0): |       |      |       |          |      |

| tCLST_SPI                 | 13-bit resolution 14-bit resolution                                                                                                                                                       |       | _    | 0.57  | -        | ms   |

|                           | 15-bit resolution                                                                                                                                                                         |       | _    | 0.64  | _        |      |

|                           | 16-bit resolution                                                                                                                                                                         |       | _    | 0.76  | _        |      |

|                           |                                                                                                                                                                                           |       | _    | 1.03  | _        |      |

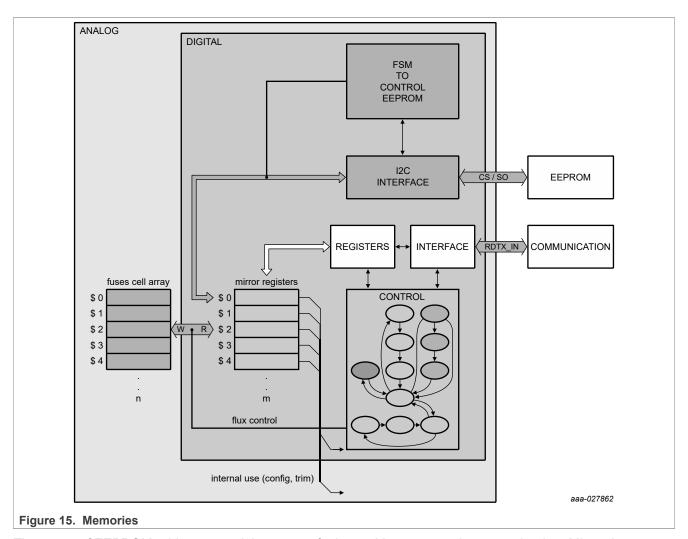

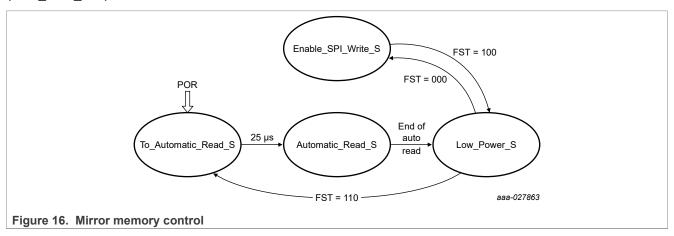

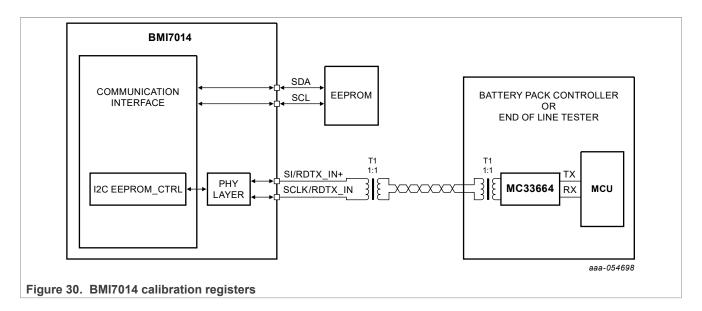

| t <sub>I2C_DOWNLOAD</sub> | Time to download EEPROM calibration after POR                                                                                                                                             |       | _    | _     | 1.0      | ms   |

| t <sub>i2C_ACCESS</sub>   | EEPROM access time, EEPROM write (depends on device selection)                                                                                                                            |       | _    | 5.0   | _        | ms   |

| t <sub>WAVE DC BITx</sub> | Daisy chain duty cycle off time                                                                                                                                                           |       |      |       |          | μs   |

| WAVE_DC_BITX              | t <sub>WAVE_DC_BITx</sub> = 00                                                                                                                                                            | 450   | 500  | 550   | <u>'</u> |      |

| twave DC BITx             | Daisy chain duty cycle off time                                                                                                                                                           |       |      | 4.0   |          | ms   |

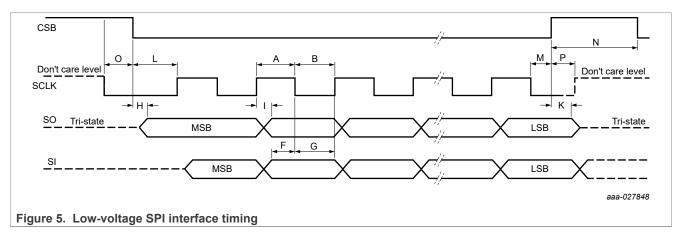

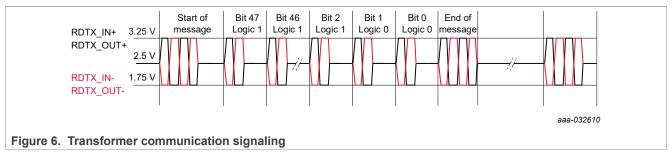

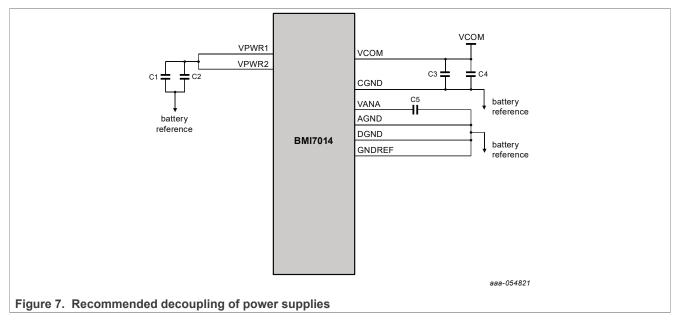

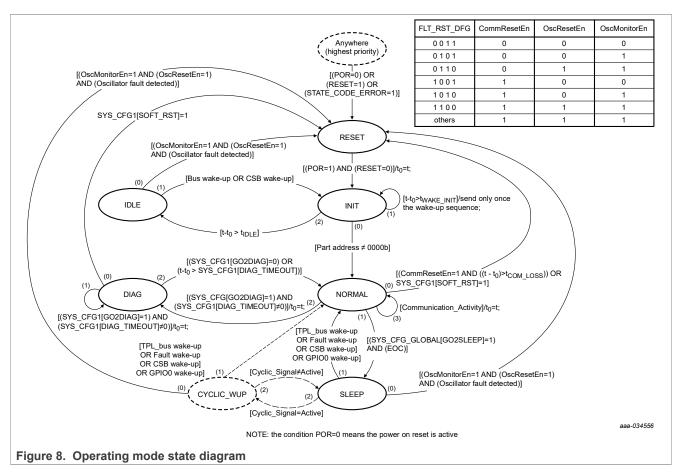

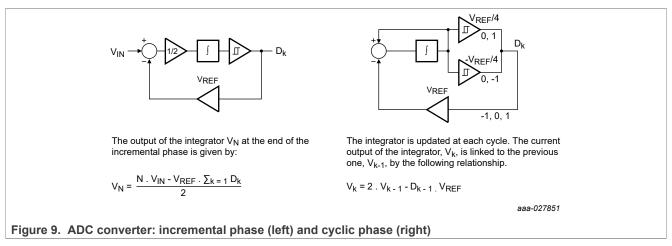

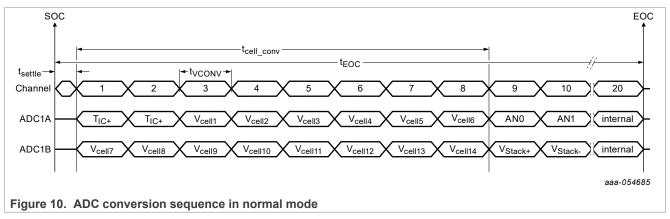

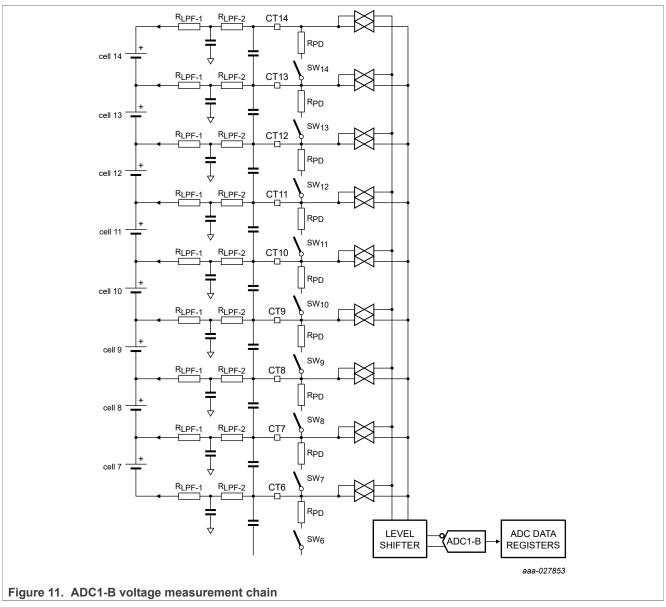

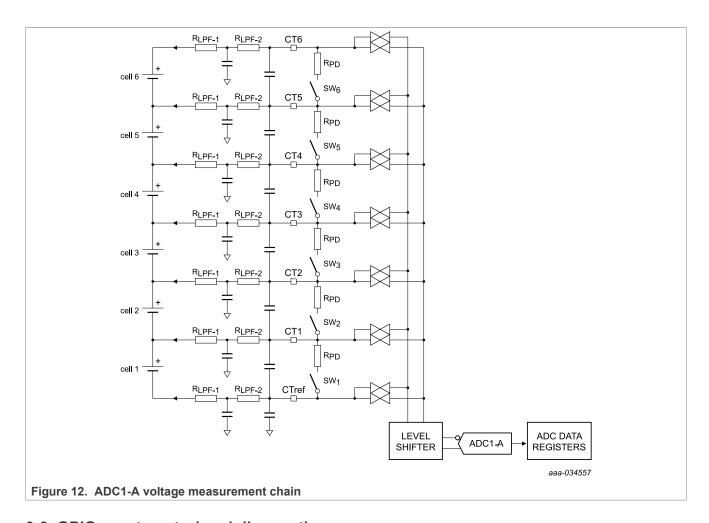

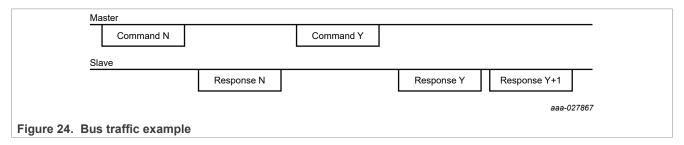

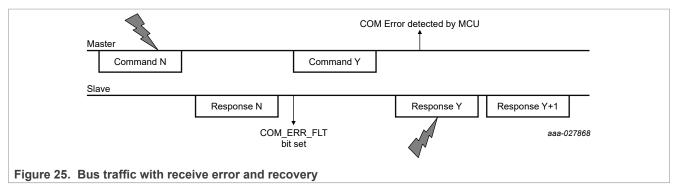

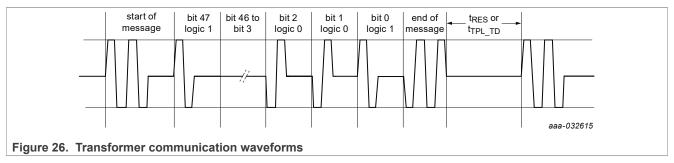

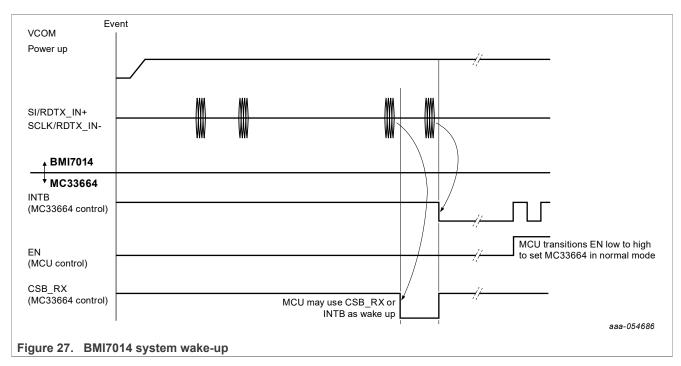

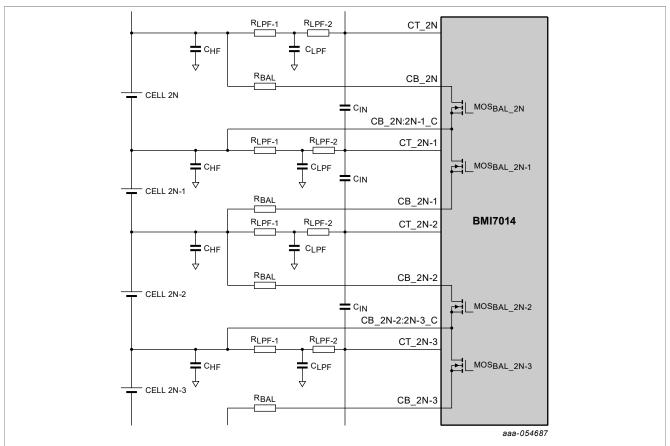

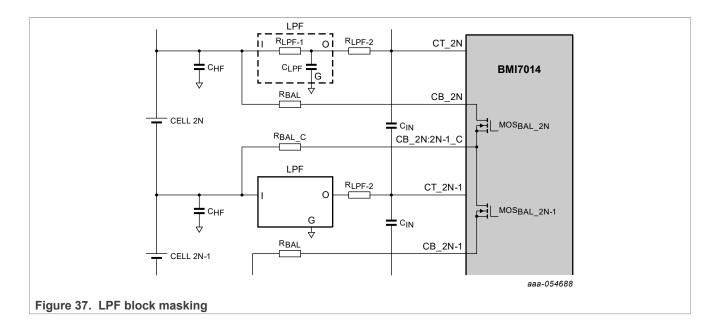

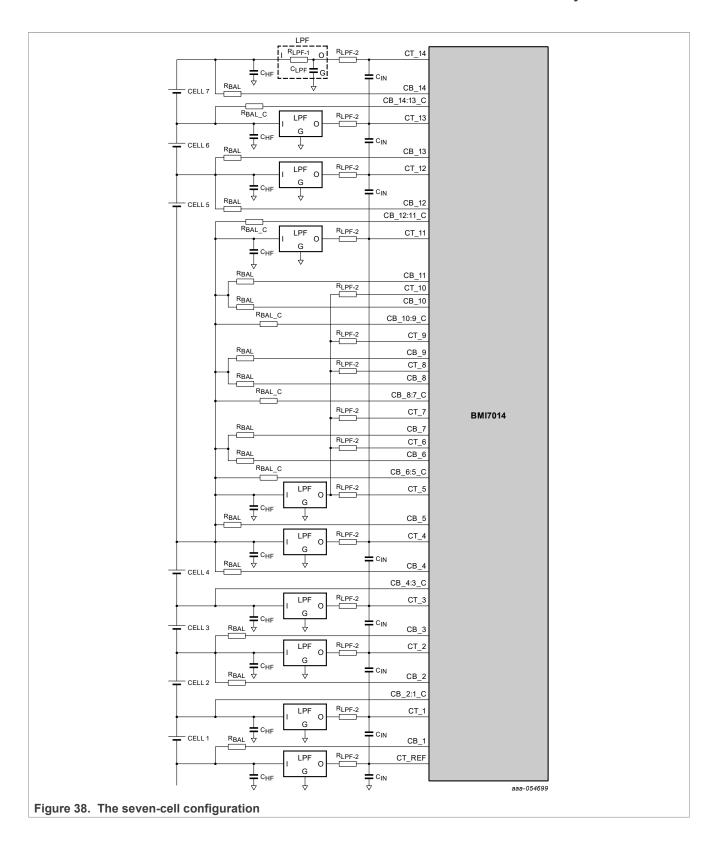

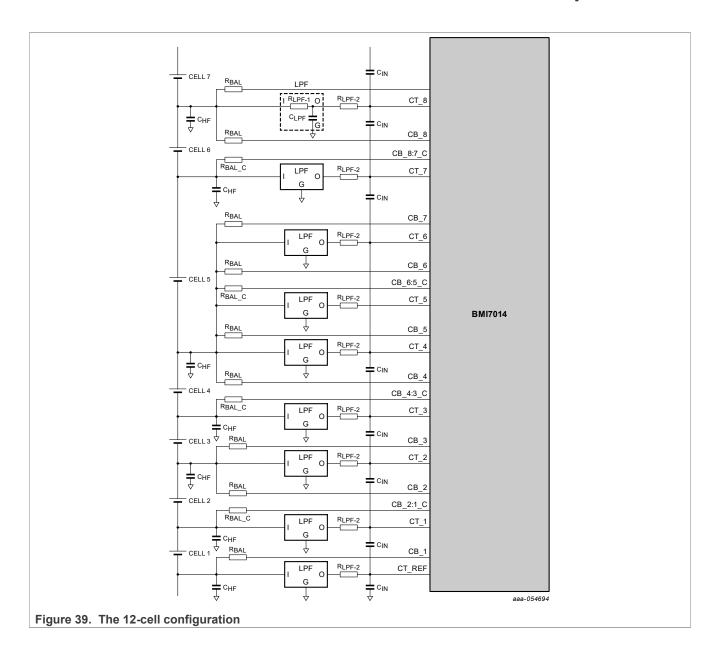

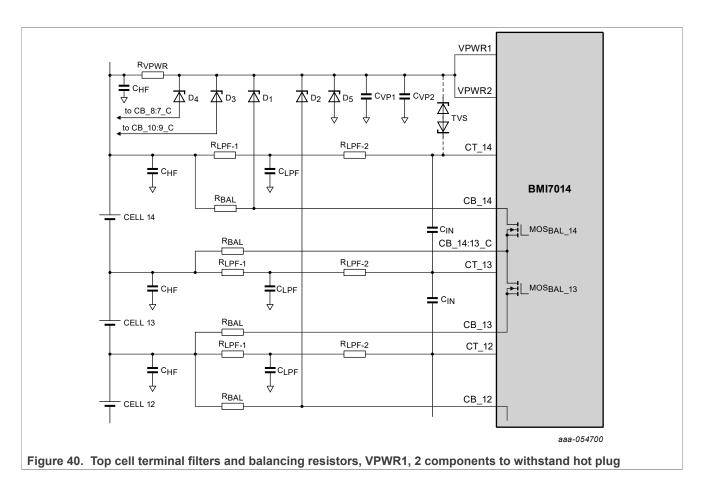

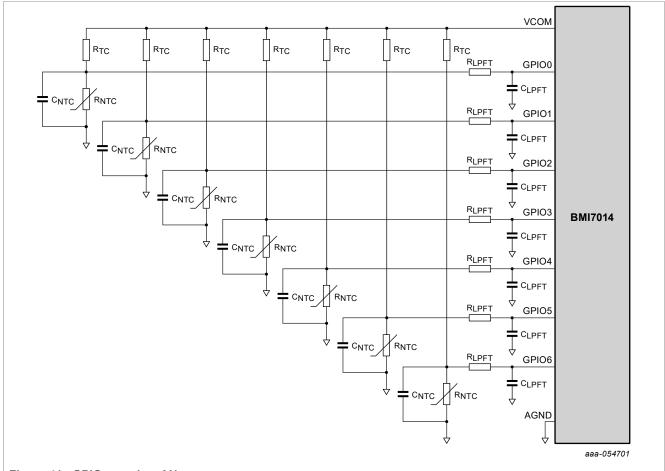

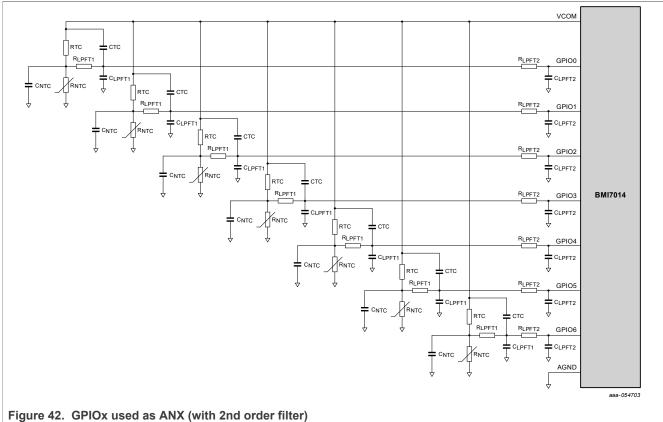

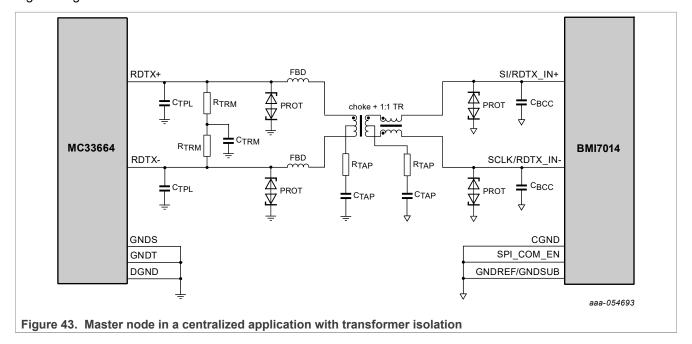

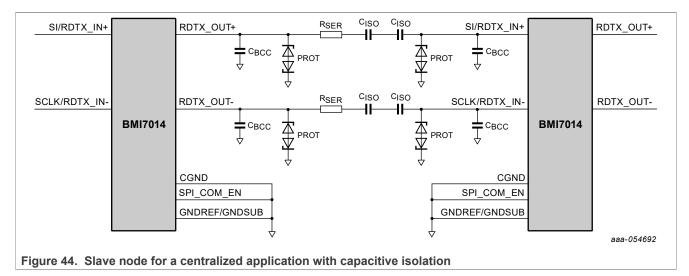

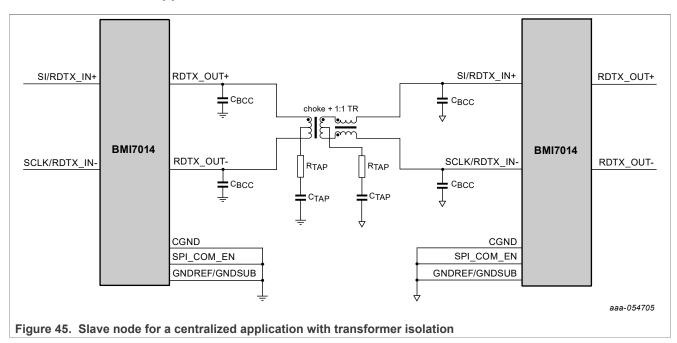

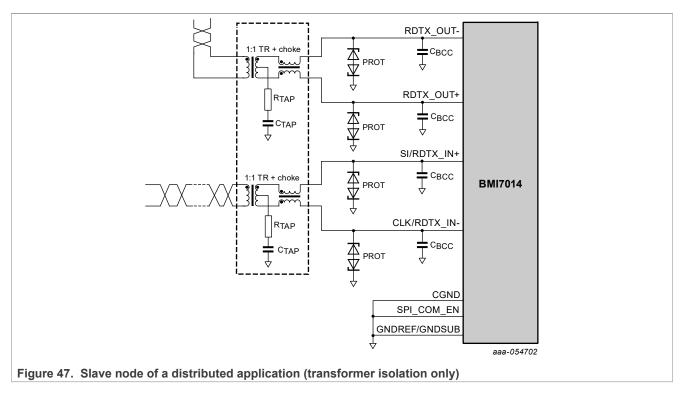

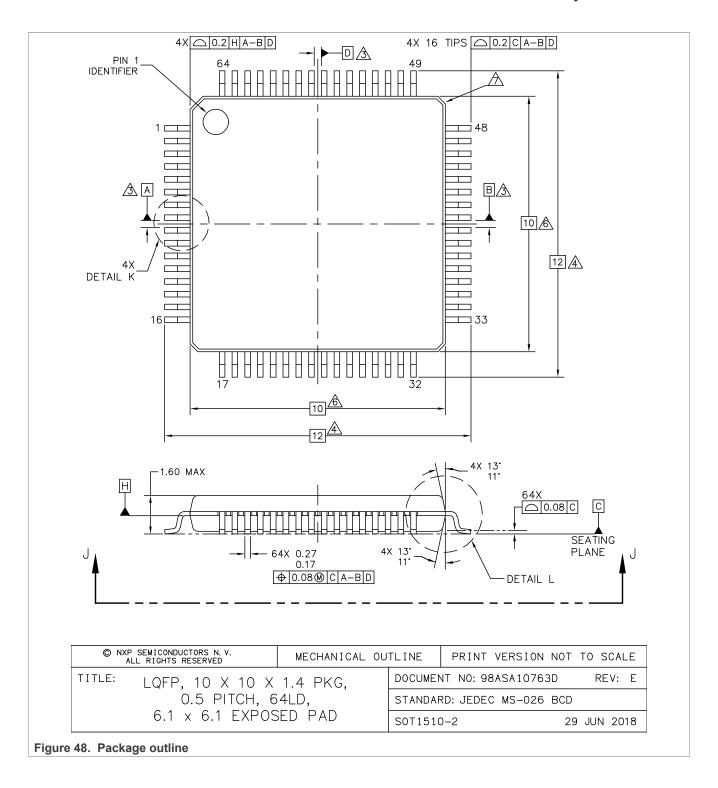

|                           | twave_dc_bitx = 01                                                                                                                                                                        |       | 0.9  | 1.0   | 1.1      |      |