# AN14183 FS2400 product guidelines

Rev. 2.0 — 8 November 2024

**Application note**

#### **Document information**

| Information | Content                                                                                                                                                                                                                                                                                                            |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | Fail-safe system basis chip (SBC), SMPS, LDO, CAN FD transceiver, ultra-wide band (UWB), near-field communication (NFC), Bluetooth Low Energy (BLE) devices, small applications, low power, functional safety, ISO pulses, non-ISO pulses, electromagnetic compatibility (EMC), external components, SPI, hardware |

| Abstract    | This application note provides product guidelines and performance results (ISO pulses, EMC) for the FS2400 system basis chip family in automotive electronic systems.                                                                                                                                              |

# 1 Introduction

### 1.1 FS24 safety system basis chip with low power and fit for ASIL B

The FS2400 is a family of automotive safety system basis chip (SBC) devices with multiple power supplies designed to support secure car access applications using ultra-wide band (UWB), near-field communication and Bluetooth Low Energy (NFC-BLE) devices, while maintaining flexibility to fit other small applications requiring low power and CAN FD communication.

This family of devices supports a wide range of applications, offering a choice of output-voltage settings, physical interfaces, and integrated system-level features to address low-power and noise-sensitive applications with automotive safety integrity levels (ASIL) up to ASIL B.

The FS2400 integrates a battery-connected switched-mode regulator (V1) and a battery-connected linear regulator (V3) to supply the microcontroller, communication devices, and other devices . V1 offers a high-performance switching regulator capable of operating in pulse frequency modulation (PFM) mode and forced pulse width modulation (FPWM) mode. The mode of operation can be changed using wake pins to optimize noise management.

The FS2400 is developed in compliance with the ISO 26262:2018 standard. The FS2400 includes enhanced safety features with a fail-safe output, becoming part of a full safety-oriented system, covering ASIL B.

The FS2400 is offered in a 5 mm x 5 mm 32-Ld HVQFN package with wettable flanks.

#### **Operating range**

- 40 V DC maximum input voltage.

- Low-power off mode with low-sleep current and multiple wake-up sources.

- Low-power on mode with HVBUCK (V1) active, HVLDO (V3) selectable by OTP and multiple wake-up sources.

### **1.2 Applications**

- UWB anchors

- NFC anchors

- BLE anchors

- Combo anchors (UWB and BLE)

- UWB radar

- All small applications requiring low power and CAN FD

- UWB master anchors

# 2 Simplified diagram

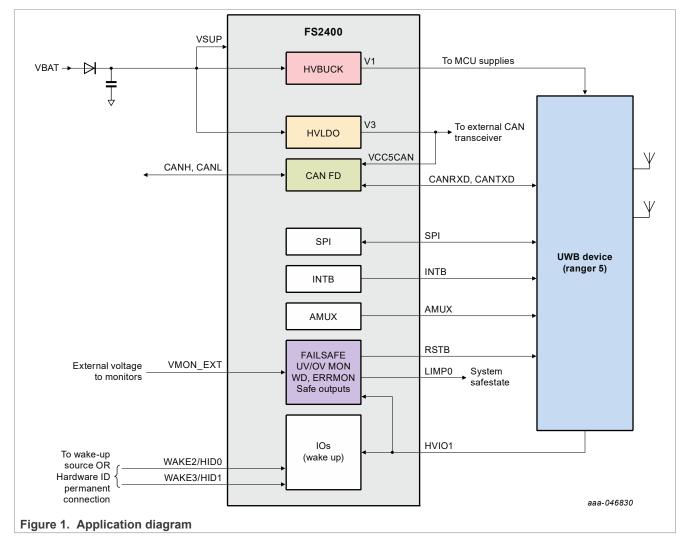

Figure 1 shows a simplified block diagram for a typical system with an FS2400.

# 3 Application external components

All external components must be automotive grade, AEC-Q100 (for IC chips), AEC-Q101 (for discrete components), and AEC-Q200 (for passive components).

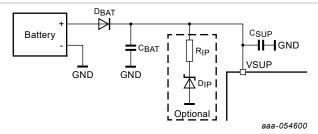

## 3.1 VBAT/VSUP components

#### Figure 2. VBAT/VSUP components

| Components       | Description                                                                                                                                                                                              |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D <sub>BAT</sub> | Reverse battery diode protection         • Low V <sub>FORWARD</sub> to minimize the losses         • I <sub>Forward</sub> > 2x maximum input current         • V <sub>Reverse</sub> ≥ 30 V               |

| R <sub>IP</sub>  | <ul> <li>Optional component to sustain ISO pulses (slow and fast positive transients) in Low-power modes (only needed if the application requires it)</li> <li>Resistor 1 kΩ - 0.25 W minimum</li> </ul> |

| D <sub>IP</sub>  | Optional component to sustain ISO pulses (slow and fast positive transients) in Low-power modes (only needed if the application requires it) <ul> <li>30 V Zener diode</li> </ul>                        |

| C <sub>BAT</sub> | <ul> <li>10 μF nominal ceramic capacitor or more</li> <li>Minimum voltage rating: 50 V</li> </ul>                                                                                                        |

| C <sub>SUP</sub> | <ul> <li>100 nF decoupling capacitor, close to the pin</li> <li>Minimum voltage rating: 50 V</li> </ul>                                                                                                  |

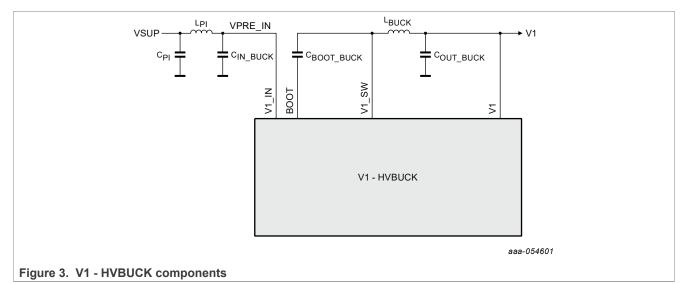

# 3.2 V1 - HVBUCK regulator

### 3.2.1 V1 - HVBUCK external components

#### Table 2. V1 - HVBUCK components description

| Components             | Description                                                                                                     |

|------------------------|-----------------------------------------------------------------------------------------------------------------|

|                        | FSW_BUCK = 2.2 MHz:                                                                                             |

|                        | <ul> <li>4.7 uF nominal decoupling capacitor, close to the pin</li> </ul>                                       |

| C <sub>IN_BUCK</sub>   | FSW_BUCK = 450 kHz:                                                                                             |

|                        | <ul> <li>10 uF nominal decoupling capacitor, close to the pin</li> </ul>                                        |

|                        | Minimum voltage rating: 50 V                                                                                    |

|                        | FSW_BUCK = 2.2 MHz:                                                                                             |

|                        | <ul> <li>L<sub>BUCK</sub> = 1 μH nominal</li> </ul>                                                             |

| L <sub>PI</sub>        | FSW_BUCK = 450 kHz:                                                                                             |

|                        | <ul> <li>L<sub>BUCK</sub> = 4.7 μH nominal</li> </ul>                                                           |

|                        | Soft saturation recommended.                                                                                    |

| C                      | Bootstrap capacitor 33 nF nominal                                                                               |

| C <sub>BOOT_BUCK</sub> | Minimum Voltage rating: 16 V                                                                                    |

|                        | FSW_BUCK = 2.2 MHz:                                                                                             |

|                        | <ul> <li>L<sub>BUCK</sub> = 4.7 μH nominal</li> </ul>                                                           |

|                        | <ul> <li>I<sub>SAT</sub> &gt; I<sub>OC_PK_PWM</sub> Max* + 20 %</li> </ul>                                      |

|                        | FSW_BUCK = 450 kHz:                                                                                             |

|                        | <ul> <li>L<sub>BUCK</sub> = 22 μH nominal</li> </ul>                                                            |

| L <sub>BUCK</sub>      | <ul> <li>I<sub>SAT</sub> &gt; I<sub>OC_PK_PWM</sub> Max* + 20 %</li> </ul>                                      |

|                        | * Use I <sub>OC_PK_PWM</sub> maximum value for calculation (refer to the <u>FS2400 data sheet</u> )             |

|                        | Soft saturation recommended.                                                                                    |

|                        | ISAT value here is to consider the case of V1 overload (or fault, such as short circuit) and IPRE being limited |

|                        | by current limit feature ILIM_PRE.                                                                              |

|                        | Shielded, ±20 % tolerance is preferred, but ±30 % is allowed.                                                   |

| Components          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C <sub>OUT_V1</sub> | <ul> <li>FSW_BUCK = 2.2 MHz:</li> <li>10 μF nominal is recommended for 2 V, 2.5 V, and 3.3 V. Minimum effective capacitance is 6.5 μF (derating vs DC bias and temperature included).</li> <li>2 x 10 μF nominal is recommended for 5 V. Minimum effective capacitance is 13 μF (derating vs DC bias and temperature included).</li> <li>FSW_BUCK = 450 kHz:</li> <li>4 x 10 μF nominal is recommended for 2 V, 2.5 V, and 5 V. Minimum effective capacitance is 25 μF (derating vs DC bias and temperature included).</li> <li>5 x 10 μF nominal is recommended for 3.3 V. Minimum effective capacitance is 25 μF (derating vs DC bias and temperature included).</li> <li>5 x 10 μF nominal is recommended for 3.3 V. Minimum effective capacitance is 25 μF (derating vs DC bias and temperature included).</li> <li>5 x 10 μF nominal is recommended for 3.3 V. Minimum effective capacitance is 25 μF (derating vs DC bias and temperature included).</li> <li>5 x 10 μF nominal is recommended for 3.3 V. Minimum effective capacitance is 25 μF (derating vs DC bias and temperature included).</li> <li>Minimum voltage rating: 2 x V1 output voltage (3 x V1 output voltage is preferred to minimize DC bias derating)</li> </ul> |

#### Table 2. V1 - HVBUCK components description...continued

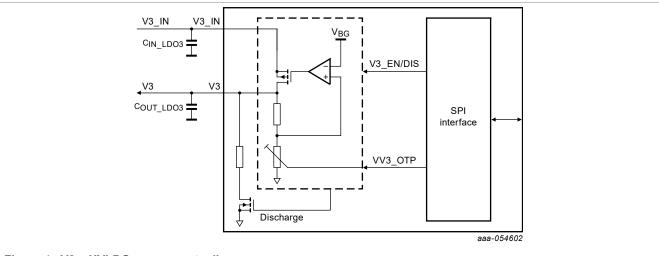

# 3.3 V3 - HVLDO regulator

| Figure 4. | V3 – HVI | DO components | s diagram |

|-----------|----------|---------------|-----------|

|-----------|----------|---------------|-----------|

| Table 3. | V3 - ŀ | HVLDO | components | description |

|----------|--------|-------|------------|-------------|

|----------|--------|-------|------------|-------------|

| Component             | Description                                                                                                                                                                                                                                                                               |  |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| C <sub>IN_LDO3</sub>  | <ul><li>1 µF nominal close to V3_IN pin</li><li>Minimum voltage rating: 50 V</li></ul>                                                                                                                                                                                                    |  |  |

| C <sub>OUT_LDO3</sub> | <ul> <li>Minimum effective capacitance is 1.3 µF (derating vs DC bias temperature included).<br/>Recommended nominal capacitance value is 2.2 µF.</li> <li>Minimum voltage rating: 2 x V3 output voltage<br/>(3 x V3 output voltage is preferred to minimize DC bias derating)</li> </ul> |  |  |

### 3.4 WAKE/HID and HVIO pins

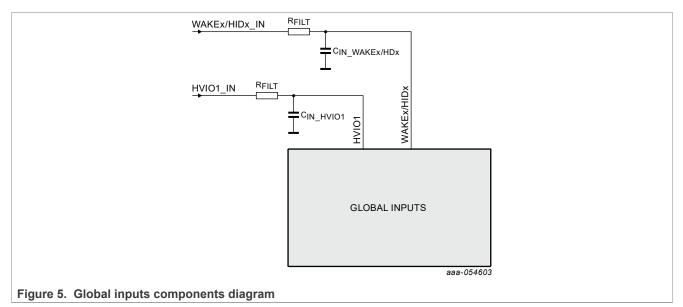

### 3.4.1 Configuration as global input

When configured as global, WAKEx/HIDx pins can either be used as wake-up sources or as a hardware identification (HID) solution. In the HID case, the pin is permanently connected to either VBAT, GND, or a floating node.

Table 4. Global inputs components description

| Component                  | Description                                                                                                                                                                                                                                                                                                                |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C <sub>IN_WAKEx/HIDx</sub> | <ul> <li>For WAKEx use case:<br/>Decoupling capacitor close to the pin for immunity</li> <li>-22 nF nominal value</li> <li>Minimum voltage rating: 50 V</li> <li>For HIDx use case:<br/>Decoupling capacitor close to the pin for immunity</li> <li>-100 nF nominal value</li> <li>Minimum voltage rating: 50 V</li> </ul> |

| C <sub>IN_HVIO1</sub>      | For HVIO1:<br>• –10 nF nominal value<br>• Minimum voltage rating: 50 V                                                                                                                                                                                                                                                     |

| R <sub>FILT</sub>          | <ul> <li>For WAKEx and HVIO1 use cases:</li> <li>Series resistor to limit the input current</li> <li>-5.1 kΩ nominal value</li> <li>For HIDx use case:</li> <li>-220 Ω nominal value</li> </ul>                                                                                                                            |

**Note:** In the case of ground loss of the module, there is a possibility (if HIDx is connected to GND) that the current flows through the HIDx pin. In that case, the current through  $R_{FILT}$  creates a ground-shift voltage equal to  $I_{SUP}*R_{FILT}$ . In most cases, if the shift is significant enough, the device goes directly in Fail-safe state because of the  $V_{BOS UV}$  triggered.

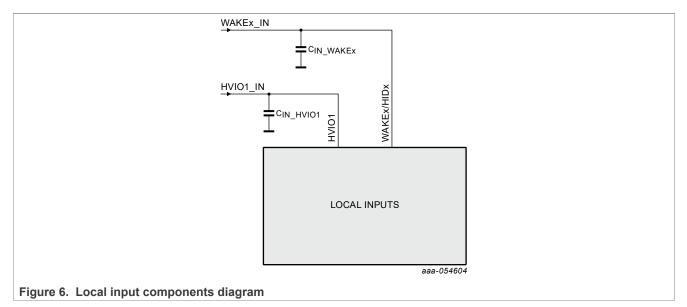

### 3.4.2 Configuration as local input

When configured as local, WAKEx/HIDx pins can only be used as wake-up sources.

Table 5. Local inputs components description

| Component             | Description                                        |

|-----------------------|----------------------------------------------------|

| C <sub>IN_WAKEx</sub> | Decoupling capacitor close to the pin for immunity |

| C <sub>IN_HVIO1</sub> | <ul> <li>–10 nF nominal value</li> </ul>           |

|                       | Minimum voltage rating: 50 V                       |

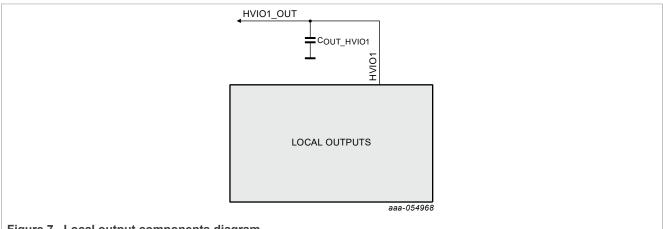

### **3.4.3 Configuration as local output**

Figure 7. Local output components diagram

| Component              | Description                                                                      |

|------------------------|----------------------------------------------------------------------------------|

| C <sub>OUT_HVI01</sub> | Decoupling capacitor close to the pin for immunity                               |

|                        | <ul> <li>–10 nF nominal value</li> </ul>                                         |

|                        | Minimum voltage rating: 2 x HVIO1 output voltage                                 |

|                        | (3 x HVIO1 output voltage is preferred to minimize DC bias derating)             |

|                        | <b>Note:</b> HVIO1 output voltage depends on HVIO1_PU_SEL_OTP bit configuration. |

#### Table 6. Local output components description

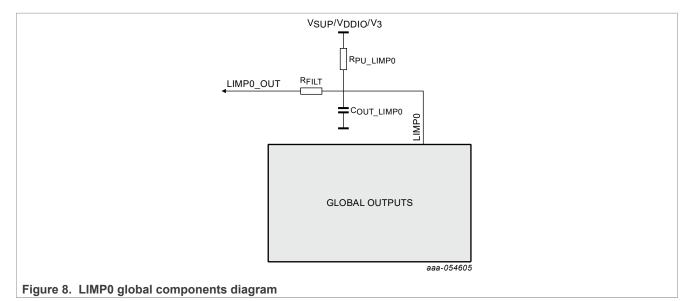

## 3.5 Functional safety pins

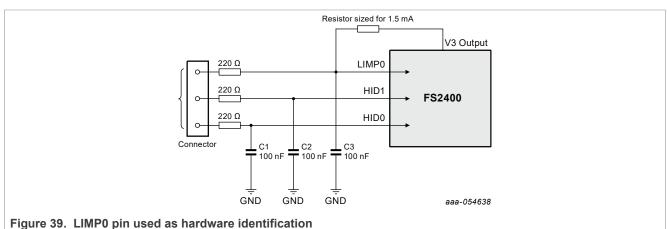

### 3.5.1 LIMP0: Configuration as global output

| Table 7. | LIMP0 | global | components | description |

|----------|-------|--------|------------|-------------|

| Component              | Description                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C <sub>OUT_LIMP0</sub> | Decoupling capacitor close to the pin for immunity<br>• –10 nF nominal value<br>• Minimum voltage rating: 50 V                                                                                                                                                                                                                                                                                         |

| R <sub>FILT</sub>      | <ul> <li>Series resistor to limit the input current</li> <li>LIMP0 as a safety output use case: 5.1 kΩ nominal value</li> <li>LIMP0 as a HW ID pin use case: 220 Ω nominal value</li> </ul>                                                                                                                                                                                                            |

| R <sub>PU_LIMP0</sub>  | <ul> <li>LIMP0 as a safety output use case:</li> <li>Pullup resistor to either VDDIO or VSUP<sup>[1]</sup></li> <li>-10 kΩ nominal value if pulled up to VSUP</li> <li>-5.1 kΩ nominal value if pulled up to VDDIO</li> <li>LIMP0 as a HW ID pin use case:</li> <li>Pullup resistor to either V3 or VDDIO</li> <li>Resistor sized for between 1.5 mA and 4 mA nominal current<sup>[2]</sup></li> </ul> |

In Low-power mode, if LIMP0 is asserted, the pin will drain a continuous current from the pullup source. [1] [2]

Current between the pullup source and LIMP0\_OUT, when LIMP0 is released and LIMP0\_OUT connected to GND + 1 V

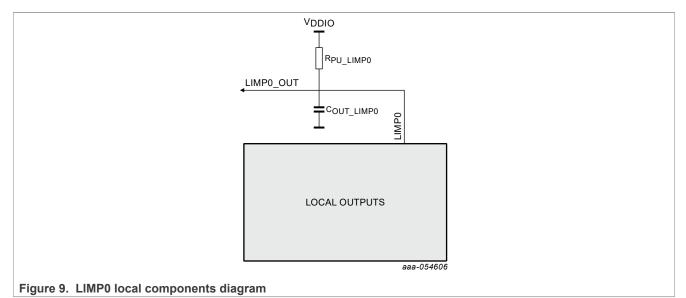

### 3.5.2 LIMP0: Configuration as local output

## Table 8. LIMP0 local components description

| Component              | Description                                                                                                                                                                     |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C <sub>OUT_LIMP0</sub> | Decoupling capacitor close to the pin for immunity<br>• 10 nF nominal value<br>• Minimum voltage rating: 50 V                                                                   |

| R <sub>PU_LIMP0</sub>  | <ul> <li>Pullup resistor to either VDDIO or VSUP<sup>[1]</sup></li> <li>10 kΩ nominal value if pulled up to VSUP</li> <li>5.1 kΩ nominal value if pulled up to VDDIO</li> </ul> |

[1] In Low-power mode, if LIMP0 is asserted, the pin will drain a continuous current from the pullup source.

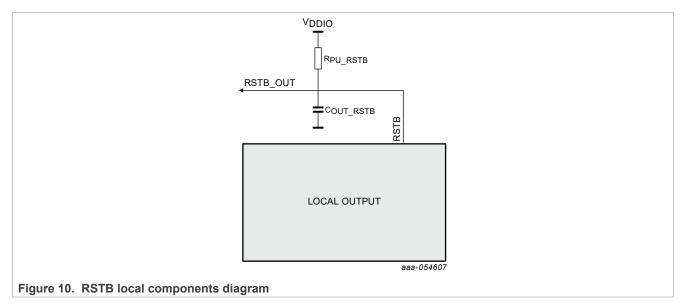

### 3.5.3 RSTB: Configuration as local output

| Component             | Description                                                                                                                                           |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| C <sub>OUT_RSTB</sub> | <ul> <li>Decoupling capacitor close to the pin for immunity</li> <li>1 nF nominal value</li> <li>Minimum voltage rating: 2 x VDDIO voltage</li> </ul> |

|                       | (3 x VDDIO voltage is preferred to minimize DC bias derating)                                                                                         |

| R <sub>PU_RSTB</sub>  | <ul><li>Pullup resistor to VDDIO</li><li>5.1 kΩ nominal value</li></ul>                                                                               |

#### Table 9. RSTB local components description

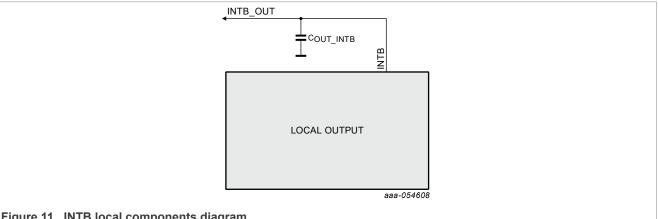

## 3.5.4 INTB: Configuration as local output

### Figure 11. INTB local components diagram

### Table 10. INTB local components description

| Component | Description                                                                                                                                                                                                                                                                                                                                                 |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | <ul> <li>Decoupling capacitor close to the pin</li> <li>1 nF nominal value (10 nF can be used for conductive immunity requirements. In this case, an external pullup resistor can be used to reduce the rising time of the pin)</li> <li>Minimum voltage rating: 2 x VDDIO voltage (3 x VDDIO voltage is preferred to minimize DC bias derating)</li> </ul> |

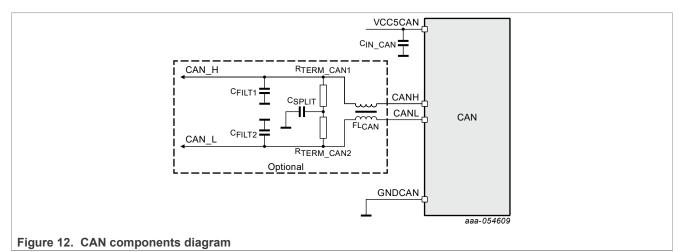

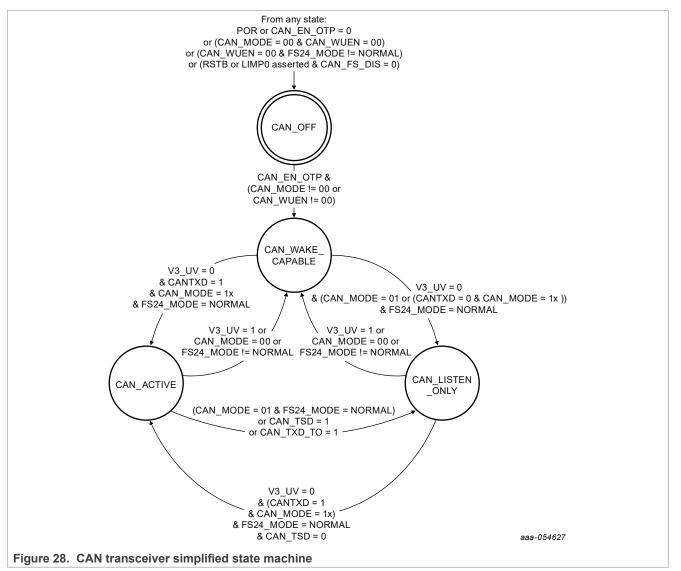

# 3.6 CAN pins

# Table 11. CAN components description

| Component                         | Description                                                                                                                                                                                                                                                                                                                              |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C <sub>IN_CAN</sub>               | Decoupling capacitor close to the pin for immunity <ul> <li>100 nF nominal value</li> <li>Minimum voltage rating: 16 V</li> </ul>                                                                                                                                                                                                        |

| FL <sub>CAN</sub> (Optional)      | Common mode choke for noise filtering (Depends on system requirements)<br>• 100 uH @ 100 kHZ nominal value                                                                                                                                                                                                                               |

| R <sub>TERM_CANx</sub> (Optional) | <ul> <li>CAN termination resistors</li> <li>2 x 60 Ω nominal value or 1 x 120 Ω if C<sub>SPLIT</sub> is not used. The goal is to have a total resistance of 60 Ω on the CAN bus. (An additional 120 Ω resistor must be populated on another CAN node).</li> <li>Power rating: 0.5 W total to support short circuit conditions</li> </ul> |

| C <sub>SPLIT</sub> (Optional)     | <ul><li>Filtering capacitor depending on system requirements</li><li>4.7 nF nominal value</li></ul>                                                                                                                                                                                                                                      |

| C <sub>FILTx</sub> (Optional)     | Filtering capacitor depending on system requirements <ul> <li>100 pF nominal value</li> </ul>                                                                                                                                                                                                                                            |

# 4 Bill of materials (BOM)

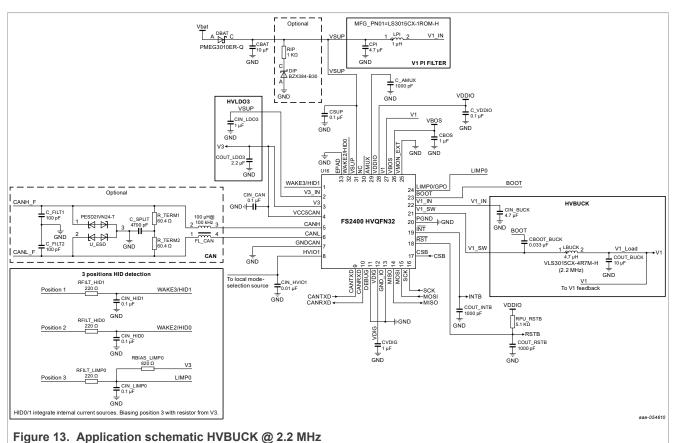

# 4.1 Application schematic used for HVBUCK @ 2.2 MHz

## 4.2 BOM for HVBUCK switching frequency at 2.2 MHz

#### Table 12. BOM reference for HVBUCK @ 2.2 MHz

| Reference     | Quantity | Description                                                | Vendor                     | Part number          | Value       |

|---------------|----------|------------------------------------------------------------|----------------------------|----------------------|-------------|

| CBAT          | 1        | CAP CER 10uF 50 V 10<br>% X7S AEC-Q200 1210                | ТDК                        | CGA6P3X7S1H106K250AE | 10 µF       |

| DBAT          | 1        | DIODE SCH PWR RECT 1 A<br>30 V AEC-Q101 SOD123W            | NEXPERIA                   | PMEG3010ER, 115      | NA          |

| RIP           | 1        | RES MF 1K 1/10 W<br>5 % AEC-Q200 0603                      | VISHAY INTERT<br>ECHNOLOGY | CRCW06031K00JNEA     | 1 kΩ        |

| DIP           | 1        | DIODE ZNR 30 V 300<br>mW AEC-Q101 SOD323                   | NEXPERIA                   | BZX384-B30, 115      | NA          |

| CSUP          | 1        | CAP CER 0.1 uF 50 V 10<br>% X7R AEC-Q200 0603              | ТDК                        | CGA3E2X7R1H104K080AA | 0.1 µF      |

| CPI, CIN_BUCK | 2        | CAP CER 4.7 uF 50 V<br>10% X7R AEC-Q200 1206               | ТDК                        | CGA5L3X7R1H475K160AB | 4.7 µF      |

| LPI           | 1        | IND FER 1 uH @ 1 MHz 2.96 A<br>0.038 OHM 20 % AEC-Q200 SMT | ТDК                        | VLS3015CX-1R0M-H     | 1 µH        |

| CBOOT_BUCK    | 1        | CAP CER 0.033 UF 16 V<br>10 % X7R AEC-Q200 0402            | трк                        | CGA2B2X7R1C333K050BA | 0.033<br>µF |

AN14183 Application note

# FS2400 product guidelines

| Reference                                 | Quantity | Description                                                        | Vendor                | Part number          | Value                  |

|-------------------------------------------|----------|--------------------------------------------------------------------|-----------------------|----------------------|------------------------|

| LBUCK                                     | 1        | IND FER 4.7 uH @ 1 MHz 1.7 A<br>0.12 OHM 20 % AEC-Q200 SMT         | TDK                   | VLS3015CX-4R7M-H     | 4.7 µH                 |

| COUT_BUCK                                 | 1        | CAP CER 10 uF 10 V 10<br>% X7S AEC-Q200 0805                       | TDK                   | CGA4J3X7S1A106K125AB | 10 µF                  |

| CIN_LDO3                                  | 1        | CAP CER 1.0 uF 50 V 10<br>% X7R AEC-Q200 0805                      | TDK                   | CGA4J3X7R1H105K125AB | 1 µF                   |

| COUT_LDO3                                 | 1        | CAP CER 2.2 uF 16 V 10<br>% X7R AEC-Q200 0805                      | TDK                   | CGA4J3X7R1C225K125AB | 2.2 µF                 |

| CIN_CAN,<br>C_VDDIO                       | 2        | CAP CER 0.1 uF 16 V 10<br>% X7R AEC-Q200 0402                      | MURATA                | GCM155R71C104KA55D   | 0.1 µF                 |

| FL_CAN                                    | 1        | FILTER COMMON MODE<br>100 uH @ 100 KHZ 150<br>mA 30 % AEC-Q200 SMT | TDK                   | ACT1210-101-2P-TL00  | 100 μH<br>@ 100<br>kHz |

| R_TERM1,<br>R_TERM2                       | 2        | RES MF 60.4 OHM 1/4<br>W 1 % AEC-Q200 0603                         | PANASONIC             | ERJ-PA3F60R4V        | 60.4 Ω                 |

| C_SPLIT                                   | 1        | CAP CER 4700 pF 50 V 5<br>% C0G AEC-Q200 0603                      | TDK                   | CGA3E2C0G1H472J080AA | 4700<br>pF             |

| U_ESD                                     | 1        | DIODE 2 CH ESD PROTECTOR<br>30 KV 24 V AEC-Q101 SOT23-3            | NEXPERIA              | PESD2IVN24-T         | NA                     |

| C_FILT1,<br>C_FILT2                       | 2        | CAP CER 100 pF 100 V 5<br>% C0G AEC-Q200 0603                      | MURATA                | GCM1885C2A101JA16D   | 100 pF                 |

| RFILT_HID0,<br>RFILT_HID1,<br>RFILT_LIMP0 | 3        | RES MF 220 OHM<br>1/10 W 5 % 0603                                  | PANASONIC             | ERJ-3GEYJ221V        | 220 Ω                  |

| CIN_HID0,<br>CIN_HID1,<br>CIN_LIMP0       | 3        | CAP CER 0.1 uF 50 V 10<br>% X7R AEC-Q200 0402                      | MURATA                | GCM155R71H104KE02D   | 0.1uF                  |

| RBIAS_LIMP0                               | 1        | RES MF 820 OHM 1/10<br>W 1 % AEC-Q200 0402                         | KOA SPEER             | RK73H1ETTP8200F      | 820 Ω                  |

| CIN_HVIO1                                 | 1        | CAP CER 0.01 uF 50 V 10<br>% X7R AEC-Q200 0603                     | ТDК                   | CGA3E2X7R1H103K080AA | 0.01 µf                |

| RPU_RSTB                                  | 1        | RES TF 5.1 K 1/4 W<br>5 % AEC-Q200 0603                            | ROHM                  | ESR03EZPJ512         | 5.1 kΩ                 |

| C_AMUX,<br>COUT_RSTB,<br>COUT_INTB        | 3        | CAP CER 1000 pF 25 V 5<br>% C0G AEC-Q200 0402                      | Murata<br>Electronics | GRT1555C1E102JA02D   | 1000<br>pF             |

| CVDIG, CBOS                               | 2        | CAP CER 1 uF 16 V 10<br>% X7R AEC-Q200 0603                        | TDK                   | CGA3E1X7R1C105K080AC | 1 µF                   |

#### Table 12. BOM reference for HVBUCK @ 2.2 MHz...continued

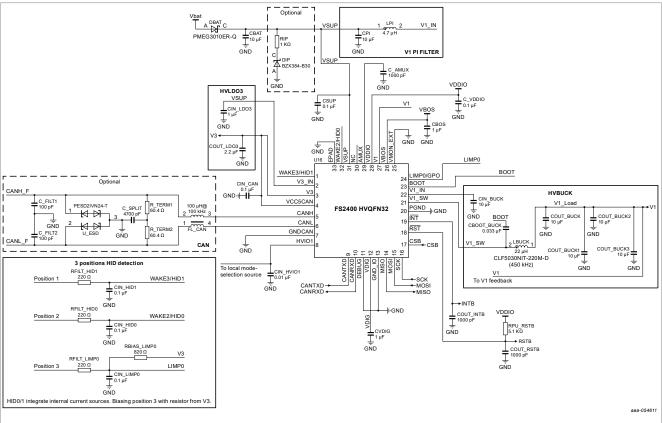

## 4.3 Application schematic used for HVBUCK @ 450 kHz

Figure 14. Application schematic for front end topology (450 kHz)

# 4.4 BOM for HVBUCK switching frequency at 450 kHz

| Table 13. | BOM | reference | for H | VBUCK | @ 450 | kHz |

|-----------|-----|-----------|-------|-------|-------|-----|

|           |     |           |       |       |       |     |

| Quantity | Description                                                | Vendor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Part number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3        | CAP CER 10 uF 50 V 10<br>% X7S AEC-Q200 1210               | ТDК                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CGA6P3X7S1H106K250AE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10 µF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1        | DIODE SCH RECT<br>30 V 1 A SOD993                          | NEXPERIA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | PMEG3010AESBYL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | NA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1        | RES MF 1K 1/10 W<br>5 % AEC-Q200 0603                      | VISHAY INTERT<br>ECHNOLOGY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CRCW06031K00JNEA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1 kΩ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1        | DIODE ZNR 30 V 300<br>mW AEC-Q101 SOD323                   | NEXPERIA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | BZX384-B30,115                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | NA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1        | CAP CER 0.1 uF 50 V 10<br>% X7R AEC-Q200 0603              | ТDК                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CGA3E2X7R1H104K080AA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0.1 µF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1        | IND FER 4.7 uH @ 1 MHz 1.7 A<br>0.12 OHM 20 % AEC-Q200 SMT | ТDК                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | VLS3015CX-4R7M-H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4.7 µH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1        | CAP CER 0.033 UF 16 V<br>10 % X7R AEC-Q200 0402            | ТDК                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CGA2B2X7R1C333K050BA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0.033<br>μF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1        | IND PWR 22 uH @ 100 kHz<br>1.42 A 20 % AEC-Q200 SMD        | TDK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CLF5030NIT-220M-D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 22 µH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|          |                                                            | 3         CAP CER 10 uF 50 V 10<br>% X7S AEC-Q200 1210           1         DIODE SCH RECT<br>30 V 1 A SOD993           1         RES MF 1K 1/10 W<br>5 % AEC-Q200 0603           1         DIODE ZNR 30 V 300<br>mW AEC-Q101 SOD323           1         CAP CER 0.1 uF 50 V 10<br>% X7R AEC-Q200 0603           1         CAP CER 0.1 uF 50 V 10<br>% X7R AEC-Q200 0603           1         IND FER 4.7 uH @ 1 MHz 1.7 A<br>0.12 OHM 20 % AEC-Q200 SMT           1         CAP CER 0.033 UF 16 V<br>10 % X7R AEC-Q200 0402           1         IND PWR 22 uH @ 100 kHz | 3         CAP CER 10 uF 50 V 10<br>% X7S AEC-Q200 1210         TDK           1         DIODE SCH RECT<br>30 V 1 A SOD993         NEXPERIA           1         RES MF 1K 1/10 W<br>5 % AEC-Q200 0603         VISHAY INTERT<br>ECHNOLOGY           1         DIODE ZNR 30 V 300<br>mW AEC-Q101 SOD323         NEXPERIA           1         CAP CER 0.1 uF 50 V 10<br>% X7R AEC-Q200 0603         NEXPERIA           1         IND FER 4.7 uH @ 1 MHz 1.7 A<br>0.12 OHM 20 % AEC-Q200 SMT         TDK           1         CAP CER 0.033 UF 16 V<br>10 % X7R AEC-Q200 0402         TDK           1         IND PWR 22 uH @ 100 kHz         TDK | 3         CAP CER 10 uF 50 V 10<br>% X7S AEC-Q200 1210         TDK         CGA6P3X7S1H106K250AE           1         DIODE SCH RECT<br>30 V 1 A SOD993         NEXPERIA         PMEG3010AESBYL           1         RES MF 1K 1/10 W<br>5 % AEC-Q200 0603         VISHAY INTERT<br>ECHNOLOGY         CRCW06031K00JNEA           1         DIODE ZNR 30 V 300<br>mW AEC-Q101 SOD323         NEXPERIA         BZX384-B30,115           1         CAP CER 0.1 uF 50 V 10<br>% X7R AEC-Q200 0603         TDK         CGA3E2X7R1H104K080AA           1         IND FER 4.7 uH @ 1 MHz 1.7 A<br>0.12 OHM 20 % AEC-Q200 SMT         TDK         VLS3015CX-4R7M-H           1         CAP CER 0.033 UF 16 V<br>10 % X7R AEC-Q200 0402         TDK         CGA2B2X7R1C333K050BA           1         IND PWR 22 uH @ 100 kHz         TDK         CI E5030NIT-220M-D |

# FS2400 product guidelines

| Reference                                               | Quantity | Description                                                        | Vendor                | Part number          | Value                  |

|---------------------------------------------------------|----------|--------------------------------------------------------------------|-----------------------|----------------------|------------------------|

| COUT_BUCK1,<br>COUT_BUCK2,<br>COUT_BUCK3,<br>COUT_BUCK4 | 4        | CAP CER 10 uF 10 V 10<br>% X7S AEC-Q200 0805                       | TDK                   | CGA4J3X7S1A106K125AB | 10 µF                  |

| CIN_LDO3                                                | 1        | CAP CER 1.0 uF 50 V 10<br>% X7R AEC-Q200 0805                      | TDK                   | CGA4J3X7R1H105K125AB | 1 µF                   |

| COUT_LDO3                                               | 1        | CAP CER 2.2 uF 16 V 10<br>% X7R AEC-Q200 0805                      | TDK                   | CGA4J3X7R1C225K125AB | 2.2 µF                 |

| CIN_CAN,<br>C_VDDIO                                     | 2        | CAP CER 0.1 uF 16 V 10<br>% X7R AEC-Q200 0402                      | MURATA                | GCM155R71C104KA55D   | 0.1 µF                 |

| FL_CAN                                                  | 1        | FILTER COMMON MODE<br>100 uH @ 100 KHZ 150<br>mA 30 % AEC-Q200 SMT | TDK                   | ACT1210-101-2P-TL00  | 100 µH<br>@ 100<br>kHz |

| R_TERM1,<br>R_TERM2                                     | 2        | RES MF 60.4 OHM 1/4<br>W 1 % AEC-Q200 0603                         | PANASONIC             | ERJ-PA3F60R4V        | 60.4 Ω                 |

| C_SPLIT                                                 | 1        | CAP CER 4700 pF 50 V 5<br>% C0G AEC-Q200 0603                      | TDK                   | CGA3E2C0G1H472J080AA | 4700<br>pF             |

| U_ESD                                                   | 1        | DIODE 2 CH ESD PROTECTOR<br>30 KV 24 V AEC-Q101 SOT23-3            | NEXPERIA              | PESD2IVN24-T         | NA                     |

| C_FILT1,<br>C_FILT2                                     | 2        | CAP CER 100 pF 100 V 5<br>% C0G AEC-Q200 0603                      | MURATA                | GCM1885C2A101JA16D   | 100 pF                 |

| RFILT_HID0,<br>RFILT_HID1,<br>RFILT_LIMP0               | 3        | RES MF 220 OHM<br>1/10 W 5 % 0603                                  | PANASONIC             | ERJ-3GEYJ221V        | 220 Ω                  |

| CIN_HID0,<br>CIN_HID1,<br>CIN_LIMP0                     | 3        | CAP CER 0.1 uF 50 V 10<br>% X7R AEC-Q200 0402                      | MURATA                | GCM155R71H104KE02D   | 0.1 uF                 |

| RBIAS_LIMP0                                             | 1        | RES MF 820 OHM 1/10<br>W 1 % AEC-Q200 0402                         | KOA SPEER             | RK73H1ETTP8200F      | 820 Ω                  |

| CIN_HVIO1                                               | 1        | CAP CER 0.01 uF 50 V 10<br>% X7R AEC-Q200 0603                     | TDK                   | CGA3E2X7R1H103K080AA | 0.01 µf                |

| RPU_RSTB                                                | 1        | RES TF 5.1 K 1/4 W<br>5 % AEC-Q200 0603                            | ROHM                  | ESR03EZPJ512         | 5.1 kΩ                 |

| C_AMUX,<br>COUT_RSTB,<br>COUT_INTB                      | 3        | CAP CER 1000 pF 25 V 5<br>% C0G AEC-Q200 0402                      | Murata<br>Electronics | GRT1555C1E102JA02D   | 1000<br>pF             |

| CVDIG, CBOS                                             | 2        | CAP CER 1 uF 16 V 10<br>% X7R AEC-Q200 0603                        | ТDК                   | CGA3E1X7R1C105K080AC | 1 µF                   |

#### Table 13. BOM reference for HVBUCK @ 450 kHz...continued

# 5 Layout guidelines

The FS2400 integrates multiple functional blocks in a single chip in a way that prevents any functions from disturbing one another. To stay consistent with that, to prevent any external emission or immunity issues and to optimize the function performances, some layout guidelines must be followed while routing the traces between FS2400 components on a printed circuit board (PCB). KITFS2400FRDMEVM rev C board layout can be used as a reference.

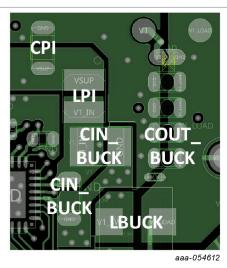

## 5.1 V1 - HVBUCK layout

- V1 HVBUCK input capacitor is connected as close as possible to the V1\_IN pin. The capacitor should be orientated to allow direct connection between the FS2400 PGND pin and the capacitor ground.

- The PGND ground shape should not be connected directly to the top layer's ground (to avoid any coupling of the noise to the battery). It should be connected through vias to an underlying layer (L3)

- V1 HVBUCK input pi filter should be placed close to the V1\_IN pin

- V1 HVBUCK current loop should be as small as possible with short and wide tracks to optimize regulation loop performances.

- V1 HVBUCK feedback (connected to V1 pin) line should be shielded by surrounding the trace with GND.

- Connect V1 HVBUCK feedback close to its output capacitors.

- Place V1 HVBUCK bootstrap capacitor as close as possible to the FS24 pins.

<u>Figure 15</u> is an example of a correct layout for HVBUCK. The bootstrap capacitor is placed on the bottom, as this is the closest it can be to the pin with this layout. The trace connecting the V1\_SW pin to LBUCK is also routed on the bottom layer.

Figure 15. Example of V1 - HVBUCK layout

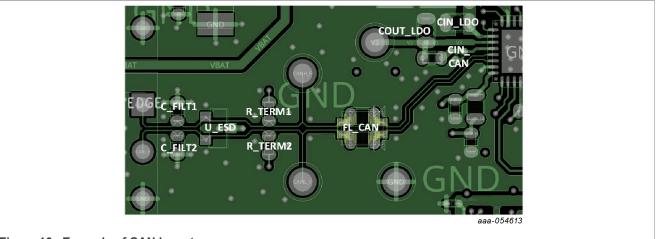

## 5.2 CAN layout

- The CAN bus should be routed in differential pairs with 120  $\Omega$  impedance.

- The CAN bus should be routed on top.

- The GNDCAN pin should be connected to the FS2400 exposed pad.

- The CAN bus should be shielded with ground planes and ground vias around the traces.

Figure 16 is an example of a correct CAN layout.

FS2400 product guidelines

# Figure 16. Example of CAN layout

### 5.3 General guidelines

- Place as many vias as possible below the FS2400 exposed pad (3 x 3 grid minimum).

- The exposed pad should not be directly connected to the different FS2400 GND pins (except GNDCAN).

- If a high-current loop is going through multiple PCB layers, multiple vias are recommended to limit the parasitic resistance and inductance in the high current path.

- When a signal is going through multiple PCB layers, ground vias around the layer interconnection are recommended to contain the electrical field.

- Avoid low-level signals below V1 HVBUCK power components.

- Connect components with high-impedance signals close to the device pin to avoid noise injection.

- When crossing a sensitive signal with a power trace, have them crossing orthogonally to avoid any coupling.

# 6 Engineering modes

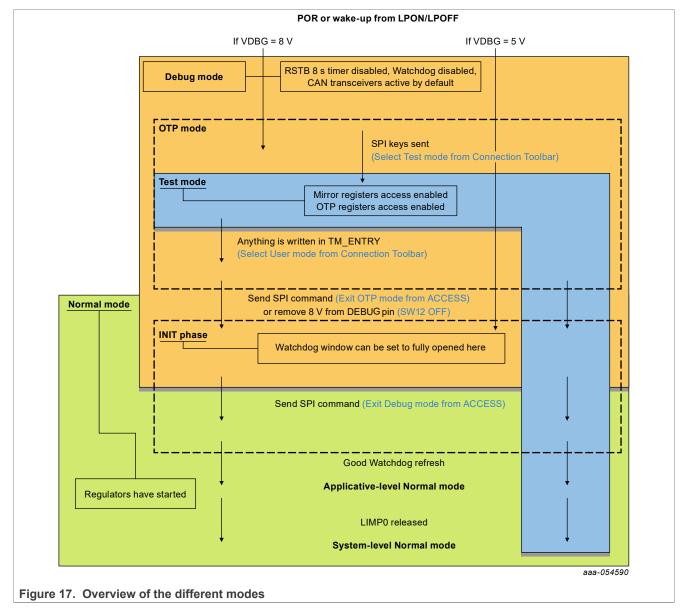

The FS2400 provides four distinct operation modes (Debug mode, Test mode, OTP mode, and Normal mode) with direct impact on device functionalities. All of these modes can operate in parallel. Understanding these modes helps to use the product properly.

For the first use, it is recommended to start the device in Debug mode. Debug mode disables the watchdog and other functional safety features, making engineering and debugging easier.

The voltage level on the FS2400 DEBUG pin is one condition for entering any given operation mode.

Figure 17 gives an overview of the device modes and actions to do in order to navigate through these.

### 6.1 Detailed state machine

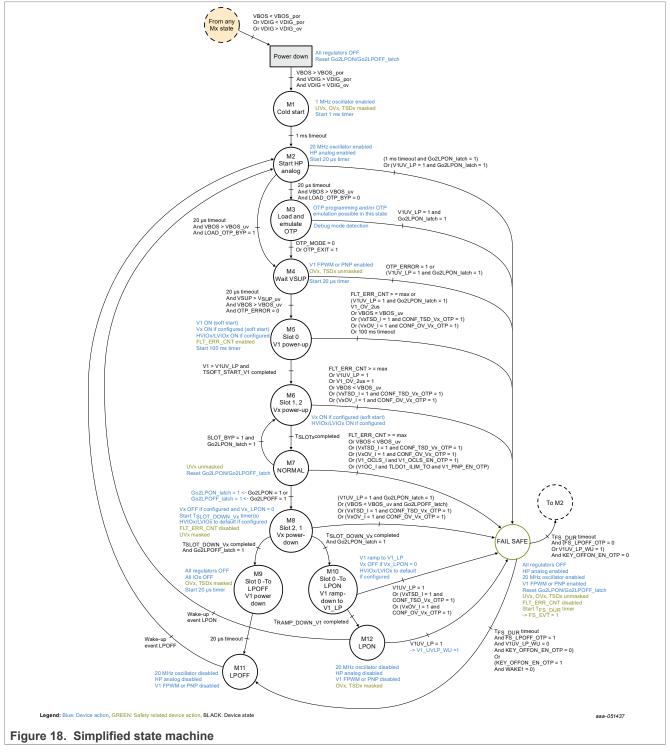

In order to better understand the behavior of the device, <u>Figure 18</u> illustrates the conditions for entering or exiting any state. The number of the state where the product is can be read inside the SPI register  $M_SYS1_CFG(0x06) \rightarrow M_FSM_STATE[4:0]$ . For more detailed information, see the <u>FS2400 data sheet</u>.

### 6.2 OTP mode

OTP mode is intended for OTP emulation and OTP programming. It is Intended for use during the engineering development process and not in the production application condition or in the vehicle.

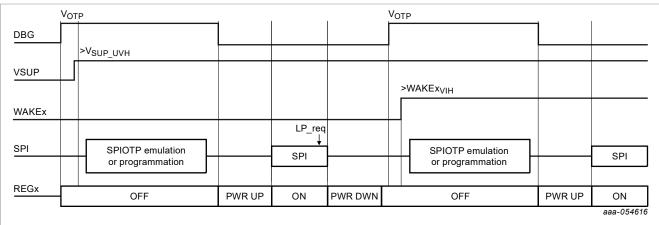

To enter OTP mode, the voltage on the DEBUG pin must be set at  $V_{OTP}$  (7.75 V < DEBUG pin < 8.15 V) prior to apply any voltage on VSUP pin.

In OTP mode:

- No watchdog refresh is required as the watchdog is configured with infinite timeout and the watchdog window is fully opened.

- RSTB 8 s timer is disabled.

- Transition to fail-safe because of the fault error counter reaching its max value is disabled.

- CAN transceiver is set to active by default.

The CAN transceiver being set to active by default in OTP mode allows an easy debug of the hardware and software routines. It is possible to emulate an OTP configuration and to start the power-up sequence while benefiting from Debug mode.

<u>Figure 19</u> shows the sequence to emulate an OTP configuration, or if already programmed, to start the powerup sequence without watchdog refresh.

Figure 19. OTP entry/emulation of programming sequence

To enter OTP mode, use the following steps. Start from device power off or Low-power mode.

- 1. Apply  $V_{OTP}$  (7.75 V < DEBUG pin < 8.15 V).

- 2. Turn on the power supply higher than the  $V_{SUP UVH}$  threshold.

OTP mode can also be entered when waking up from Low-power modes. The state machine will pass through the OTP mode entry state and verify the threshold again.

### 6.2.1 OTP emulation

Enter OTP mode and Test mode to emulate an OTP configuration. Follow the <u>instructions</u> using KITFS2400FRDMEVM or KTFS24SKTFRDMEVM. Start from device power off or Low-power mode.

- 1. Apply  $V_{OTP}$  (7.75 V < DEBUG pin < 8.15 V) SW12 on in EVB.

- 2. Turn on the power supply higher than the  $V_{SUP UVH}$  threshold.

- 3. Send Test mode keys. A programming script usually contains Test mode keys.

- 4. Run a TBB script using the NXP GUI.

- 5. Pull the DEBUG pin below the OTP mode threshold. (SW12 off in EVB)

6. The device power-up sequence will start, and the device will remain in Debug mode and in Test mode. OTP configuration emulation will remain until device POR.

### 6.2.2 OTP programming

OTP mode and Test mode are required to permanently program an OTP configuration. Follow the <u>instructions</u> using KITFS2400FRDMEVM or KTFS24SKTFRDMEVM. The user can program device sectors twice. Make sure sectors are available. Start from device power off or Low-power mode.

- 1. Apply  $V_{OTP}$  (7.75 V < DEBUG pin < 8.15 V) SW12 on on the EVB.

- 2. Turn on the power supply higher than the  $V_{SUP UVH}$  threshold.

- 3. Send Test mode keys. A programming script usually contains Test mode keys.

- 4. Program the device using the programming tool of the NXP GUI and a TBB script. Below is a <u>script</u> <u>example</u>.

- 5. Pull the DEBUG pin below the OTP mode threshold. (On the EVB, is SW12 off.)

- 6. The device power-up sequence will start and the FS24 will remain in Debug mode and Test mode.

- 7. Restart the device without entering OTP mode (DEBUG pin < 7.75 V) to verify the OTP has been programmed. The regulators should start automatically.

```

Copyright 2024 NXP. NXP Confidential. This software is owned or controlled by

NXP and may only be used strictly in accordance with the applicable license

terms found at https://www.nxp.com/LA_OPT_NXP_SW. Only the "internal use

license" in Section 2.2 in the NXP SOFTWARE LICENSE AGREEMENT is granted for

this software.

//FS2400-B0 - OTP Editor

//file generated on Thu Oct 19 13:57:03 2023

//Device Type : QM

//OTP ID : A1

//OTP Revision : B

//Part Marking : PFS2400AVMA1ES

//Customer : NXP

//Write main registers

//Test mode entry

SET MODE:FS2400-B0:test-mode

//Verify test mode entry

GET REG:FS2400-B0:M TestMode:M TM STATUS1

//Configure OTP Mirror Registers

SET REG:FS2400-B0:OTP:M MIRRORDATA:0x0008

SET REG:FS2400-B0:OTP:M MIRRORCMD:0x011C

SET REG:FS2400-B0:OTP:M MIRRORDATA:0x0001

SET REG:FS2400-B0:OTP:M MIRRORCMD:0x011D

SET REG: FS2400-B0: OTP: M MIRRORDATA: 0x003a

SET REG:FS2400-B0:OTP:M MIRRORCMD:0x011E

SET REG:FS2400-B0:OTP:M MIRRORDATA:0x00a8

SET REG:FS2400-B0:OTP:M MIRRORCMD:0x011F

SET REG: FS2400-B0: OTP: M MIRRORDATA: 0x0017

SET REG: FS2400-B0:OTP:M MIRRORCMD: 0x0120

SET REG:FS2400-B0:OTP:M MIRRORDATA:0x0057

SET REG: FS2400-B0:OTP:M MIRRORCMD: 0x0121

SET REG: FS2400-B0: OTP: M MIRRORDATA: 0x0034

SET REG:FS2400-B0:OTP:M MIRRORCMD:0x0122

SET REG:FS2400-B0:OTP:M MIRRORDATA:0x0012

SET REG:FS2400-B0:OTP:M MIRRORCMD:0x0123

SET REG: FS2400-B0: OTP:M MIRRORDATA: 0x00fc

```

```

SET REG:FS2400-B0:OTP:M MIRRORCMD:0x0124

SET REG: FS2400-B0: OTP:M MIRRORDATA: 0x00bc

SET REG:FS2400-B0:OTP:M MIRRORCMD:0x0125

SET REG:FS2400-B0:OTP:M MIRRORDATA:0x000c

SET REG:FS2400-B0:OTP:M MIRRORCMD:0x0126

SET REG: FS2400-B0: OTP: M MIRRORDATA: 0x0040

SET REG:FS2400-B0:OTP:M MIRRORCMD:0x0127

SET REG:FS2400-B0:OTP:M MIRRORDATA:0x0000

SET REG:FS2400-B0:OTP:M MIRRORCMD:0x0128

SET REG:FS2400-B0:OTP:M MIRRORDATA:0x0080

SET REG:FS2400-B0:OTP:M MIRRORCMD:0x0129

REG:FS2400-B0:OTP:M MIRRORDATA:0x0022

SET

SET REG:FS2400-B0:OTP:M MIRRORCMD:0x012A

SET REG:FS2400-B0:OTP:M MIRRORDATA:0x00cf

SET REG:FS2400-B0:OTP:M MIRRORCMD:0x012B

SET REG:FS2400-B0:OTP:M MIRRORDATA:0x00cf

SET REG:FS2400-B0:OTP:M MIRRORCMD:0x012C

SET REG:FS2400-B0:OTP:M MIRRORDATA:0x00f0

SET REG: FS2400-B0:OTP:M MIRRORCMD: 0x012D

SET REG: FS2400-B0: OTP: M MIRRORDATA: 0x0022

SET REG:FS2400-B0:OTP:M MIRRORCMD:0x012E

SET REG:FS2400-B0:OTP:M MIRRORDATA:0x0000

SET REG:FS2400-B0:OTP:M MIRRORCMD:0x012F

SET REG: FS2400-B0: OTP:M MIRRORDATA: 0x0030

SET_REG:FS2400-B0:OTP:M_MIRRORCMD:0x0130

//OTP Command CRC Fill + GO

SET REG:FS2400-B0:M OTP:M OTPCMD:0x0125

//OTP Command CRC Check + GO

SET REG:FS2400-B0:M OTP:M OTPCMD:0x0124

//Verify test mode entry

GET REG:FS2400-B0:M TestMode:M TM STATUS1

```

//----- END MAIN ------

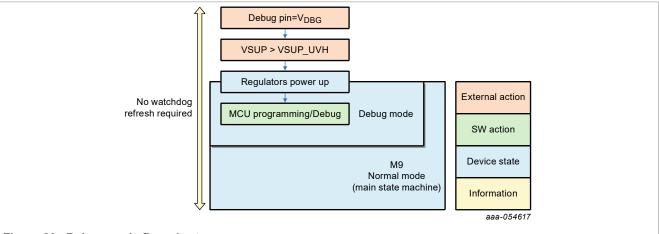

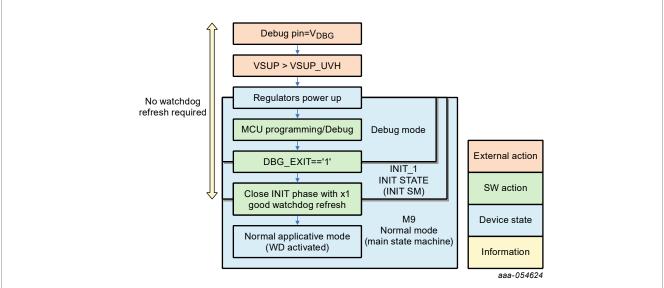

### 6.3 Debug mode

Debug mode can be used during the customer production process. In Debug mode, no watchdog refresh is required as the watchdog is disabled along with other safety features. This mode can be accessed by applying  $V_{DBG}$  (3.5 V < DEBUG pin < 5.5 V) on the DEBUG pin prior to applying any voltage to the VSUP pin.

Once the VSUP pin is supplied properly, the device will start its power-up sequence and allow MCU programming or easy debug.

It is assumed that an OTP configuration was programmed into the device before Debug mode entry.

Figure 20. Debug mode flow chart

The FS24 can exit Debug mode using the DBG\_EXIT bit from the M\_SYS1\_CFG SPI register. The procedure is detailed in <u>Section 7.3</u>.

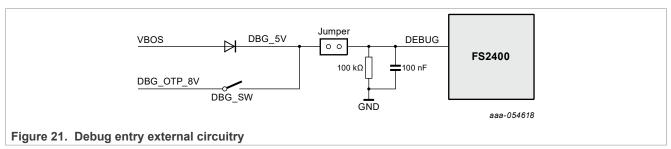

## 6.4 Debug entry circuitry

To enter OTP mode or Debug mode, the proposed circuitry, shown in <u>Figure 21</u>, powered from VBOS can be used. The VBOS regulator manages the best of supply from VSUP (or V1 in LPON mode) to efficiently generate the power to supply the internal biasing of the device, in all device modes.

For Debug mode, to start the power-up sequence without need for watchdog refresh, place a jumper between signal DBG\_5V and the DEBUG pin. This will apply ~4.3 V to the DEBUG pin.

To get to OTP mode for emulation or programming, a switch (DBG\_SW in <u>Figure 21</u>) can be added to apply ~8 V on the DEBUG pin. Once the OTP script has been sent, DBG\_SW should be opened to start the power-up sequence.

# 7 Operation modes

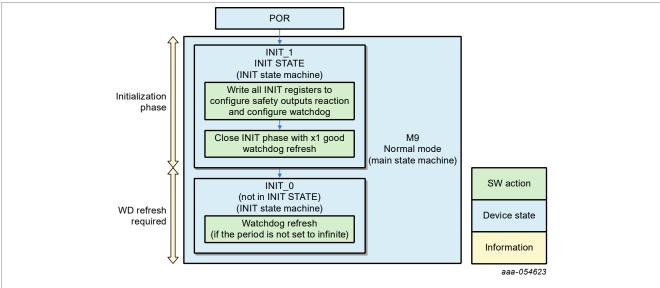

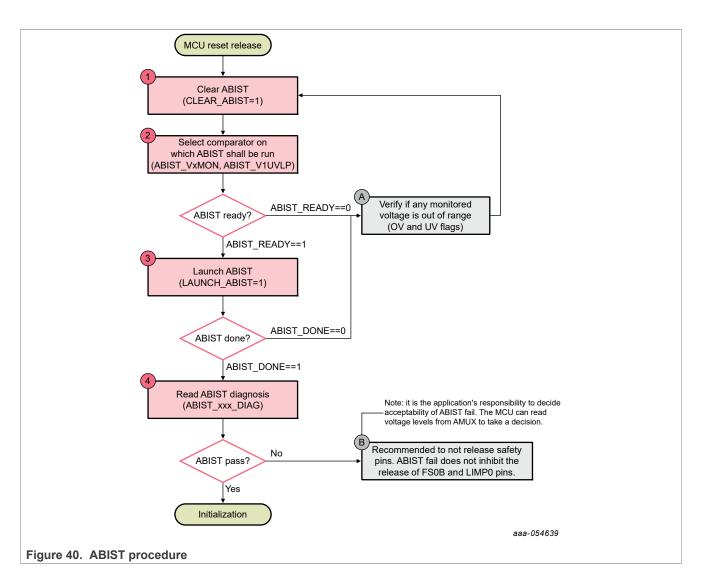

### 7.1 INIT state

### 7.1.1 INIT registers configuration

After power up, the INIT state machine waits in INIT state. In this state, the MCU must configure FS\_I\_xxx registers and then perform a good watchdog refresh to get out of the INIT state.

During this phase, the following features should be configured.

- 1. **Configure** all overvoltage and undervoltage impact on RSTB and LIMP0 with VxMON\_OV\_XXXX\_IMPACT and VxMON\_UV\_XXXX\_IMPACT SPI bits.

- Configure the WD window period, the WD counters limits and its impact on RSTB and LIMP0. Ensure the configuration does not violate the FTTI requirement at system level.

Note: INIT state is the only state where you can configure the WD period to infinite. Once out of the INIT state you can only configure the WD period using the values defined between 1 and 16384 ms.

- 3. Configure the fault error counter limit and its impact on RSTB and LIMP0 at intermediate value

- 4. **Configure** the RSTB pulse duration, RSTB request enablement, external RSTB monitoring enablement, RSTB 8 sec timer enablement

- 5. **Configure** Ext. IC error monitoring and its impact on RSTB

When all FS\_I\_xxx registers are written, the MCU should send a good WD refresh to get out of the INIT state and close the FS2400 initialization phase. By default, the WD period is configured to 256 ms. If the good WD refresh is not sent before those 256 ms, the WD error counter will be incremented. Incrimenting will eventually lead the device to generate RSTB pulses and/or main state machine transition to Fail-state state.

The figures in <u>Table 14</u> shows an example of an INIT registers' configuration for the VMONs reaction for V0MON, V1MON, V3MON :

Table 14. VMON OV/UV reaction configuration example

| -      | No Effect       | V3MON_OV_RSTB_IMPACT:  |

|--------|-----------------|------------------------|

| on 👻   | LIMP0 Assertion | V3MON_OV_LIMP0_IMPACT: |

|        | No Effect       | V3MON_UV_RSTB_IMPACT:  |

| on 🔹   | LIMP0 Assertion | V3MON_UV_LIMP0_IMPACT: |

| -      | No Effect       | VOMON_OV_RSTB_IMPACT:  |

| •      | No Effect       | V0MON_OV_LIMP0_IMPACT: |

| •      | No Effect       | VOMON_UV_RSTB_IMPACT:  |

| -      | No Effect       | VOMON_UV_LIMP0_IMPACT: |

| -05461 | aaa-05          |                        |

V1MON\_OV\_RSTB\_IMPACT: RSTB Assertion • V1MON\_OV\_LIMP0\_IMPACT: LIMP0 Assertion • V1MON\_UV\_RSTB\_IMPACT: RSTB Assertion • V1MON\_UV\_LIMP0\_IMPACT: LIMP0 Assertion • aaa-054620

SPI registers to write: FS\_I\_OVUV\_CFG1 : 0x1680 FS I OVUV CFG2 : 0x0480

AN14183 Application note

### FS2400 product guidelines

| RESERVED                  | RESERVED   | RESERVED                 | V1MON_OV_RS<br>TB_IMPACT | RESERVED                  | V1MON_OV_LI<br>MP0_IMPACT | V1MON_UV_RS<br>TB_IMPACT | RESERVED                  |

|---------------------------|------------|--------------------------|--------------------------|---------------------------|---------------------------|--------------------------|---------------------------|

| V1MON_UV_LI<br>MP0_IMPACT | RESERVED   | RESERVED                 | RESERVED                 | RESERVED                  | RESERVED                  | RESERVED                 | RESERVED                  |

| FS_I_OVUV_CFG2 (0         | 0x33) Read | 0x0489 Write             | 0x0480                   |                           |                           |                          |                           |

| RESERVED                  | RESERVED   | RESERVED                 | V3MON_OV_RS<br>TB_IMPACT | RESERVED                  | V3MON_OV_LI<br>MP0_IMPACT | V3MON_UV_RS<br>TB_IMPACT | RESERVED                  |

| V3MON_UV_LI<br>MP0_IMPACT | RESERVED   | VOMON_OV_RS<br>TB IMPACT | RESERVED                 | VOMON_OV_LI<br>MP0 IMPACT | VOMON_UV_RS<br>TB IMPACT  | RESERVED                 | VOMON_UV_LI<br>MP0_IMPACT |

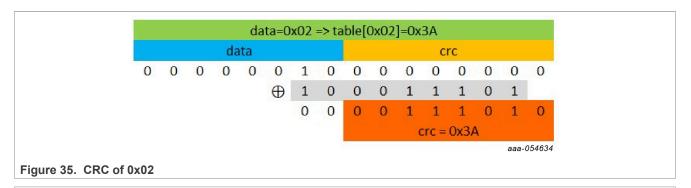

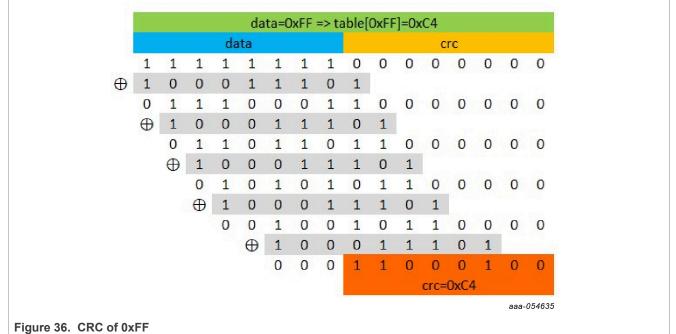

### 7.1.2 INIT CRC

If the feature is enabled by OTP, the FS2400 provides a cyclic 8-bit CRC to verify the integrity of the INIT registers. Refer to the FS2400 data sheet for more information.

### 7.1.2.1 Computing the CRC

The 8-bit CRC is computed on the result of the concatenation of the following register bits:

- FS\_I\_OVUV\_CFG1[15:0]

- FS\_I\_OVUV\_CFG2[15:0]

- FS\_I\_ERRMON\_LIMP0\_CFG[15:0]

- FS\_I\_FSSM\_CFG[15:4]

- FS\_I\_WD\_CFG[15:7]

Reserved bits are not part of the concatenation

The calculation to apply on the result of the concatenation is the same as the SPI CRC, using  $x^8+x^4+x^3+x^2+1$  polynomial. The MCU must write the obtained CRC in the FS\_CRC register before closing the INIT phase, after the modification of the INIT registers.

Figure 23 an example of INIT CRC computation based on a given configuration of the INIT registers.

### FS2400 product guidelines

|                                            | V1MON_OV_RSTB_IMPACT  | 1 |                        |

|--------------------------------------------|-----------------------|---|------------------------|

| FS_I_OVUV_CFG1[15:0]                       | V1MON_OV_LIMP0_IMPACT | 1 |                        |

| concatenated                               | V1MON_UV_RSTB_IMPACT  | 0 |                        |

|                                            | V1MON_UV_LIMP0_IMPACT | 1 |                        |

|                                            | VMON_OV_RSTB_IMPACT   | 1 |                        |

|                                            | V3MON_OV_LIMP0_IMPACT | 1 |                        |

|                                            | V3MON_UV_RSTB_IMPACT  | 1 |                        |

| FS_I_OVUV_CFG2[15:0]                       | V3MON_UV_LIMP0_IMPACT | 1 |                        |

| concatenated                               | V0MON_OV_RSTB_IMPACT  | 1 |                        |

|                                            | V0MON_OV_LIMP0_IMPACT | 1 |                        |

|                                            | V0MON_UV_RSTB_IMPACT  | 1 |                        |

|                                            | V0MON_UV_LIMP0_IMPACT | 1 |                        |

|                                            | LIMP0_GPO             | 0 |                        |

|                                            | ERRMON_M              | 0 |                        |

| S_I_ERRMON_LIMP0_CFG[15:0]<br>concatenated | ERRMON_FLT_POLARITY   | 0 |                        |

|                                            | ERRMON_ACK_TIME[1]    | 0 | FS_CRC[7:0]            |

|                                            | ERRMON_ACK_TIME[0]    | 0 | CRC 0b 0 0 1 0 1 0 1 1 |

|                                            | ERRMON_FS_REACTION    | 1 | 0x 2 B                 |

|                                            | RSTB_REQ_EN           | 0 |                        |

|                                            | EXT_RSTB_DIS          | 0 |                        |

|                                            | RSTB8S_DIS            | 0 |                        |

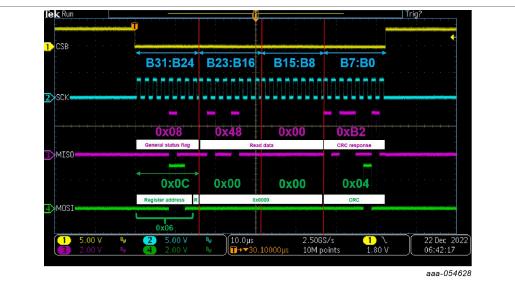

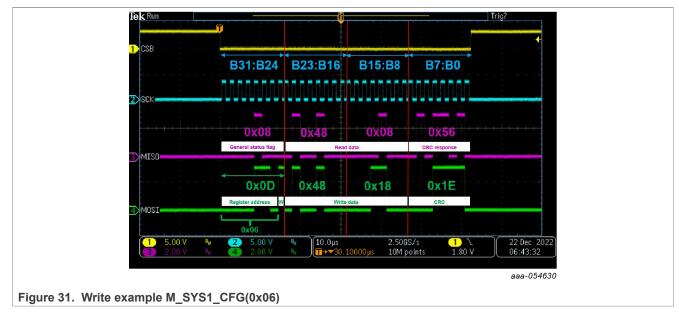

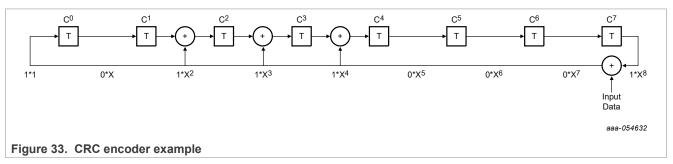

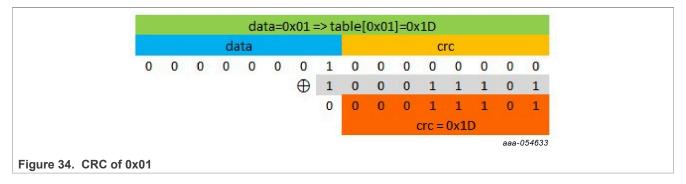

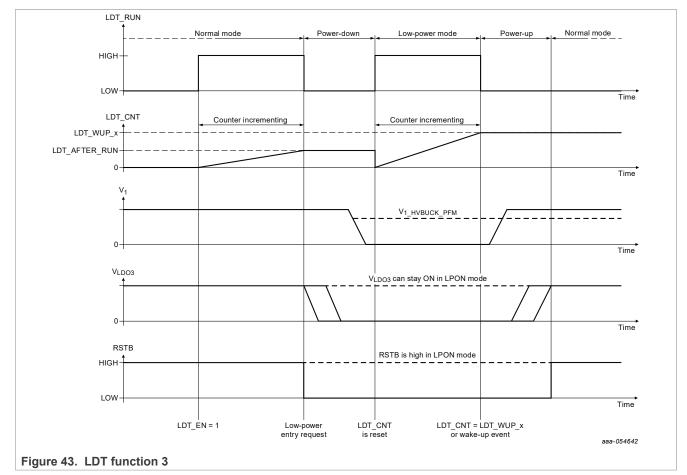

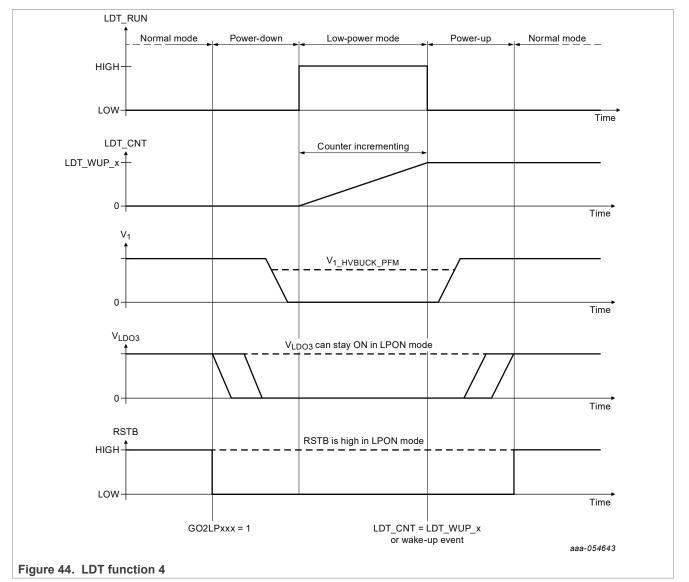

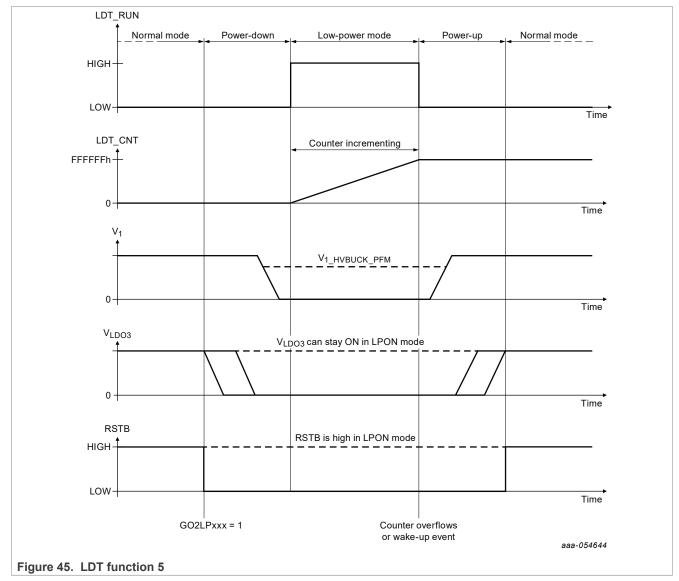

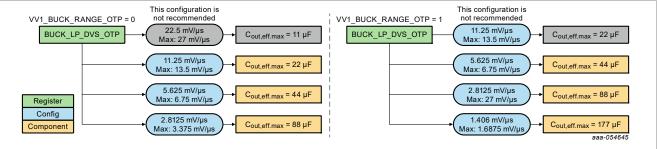

| FS_I_FSSM_CFG[15:4]                        | RSTB_DUR              | 0 |                        |