Presented by

-

Ecosystem Product Manager, NXP Semiconductors

Sign in for a personalized NXP experience.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

Sign in to access this content and additional site features. Don’t have an account? Register now.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

Sign in to access this content and additional site features. Don’t have an account? Register now.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

Sign in to access this content and additional site features. Don’t have an account? Register now.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

Sign in to access this content and additional site features. Don’t have an account? Register now.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

Sign in to access this content and additional site features. Don’t have an account? Register now.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

Sign in to access this content and additional site features. Don’t have an account? Register now.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

Sign in to access this content and additional site features. Don’t have an account? Register now.

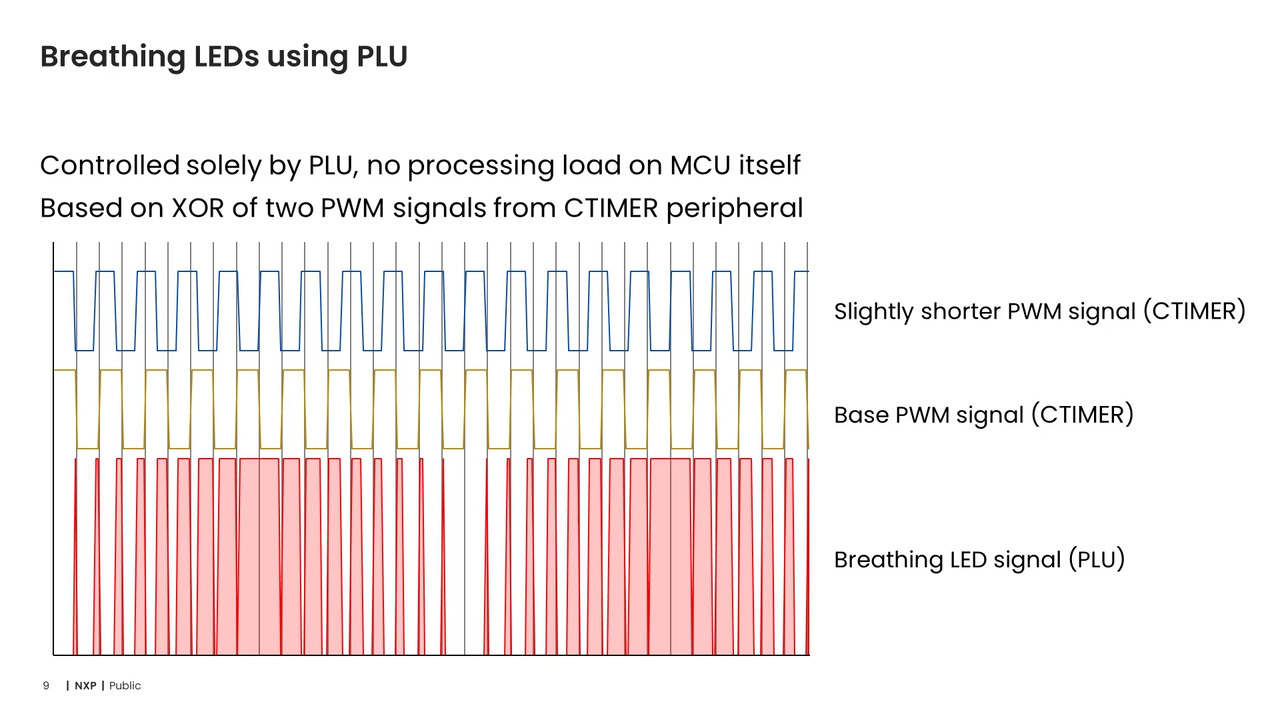

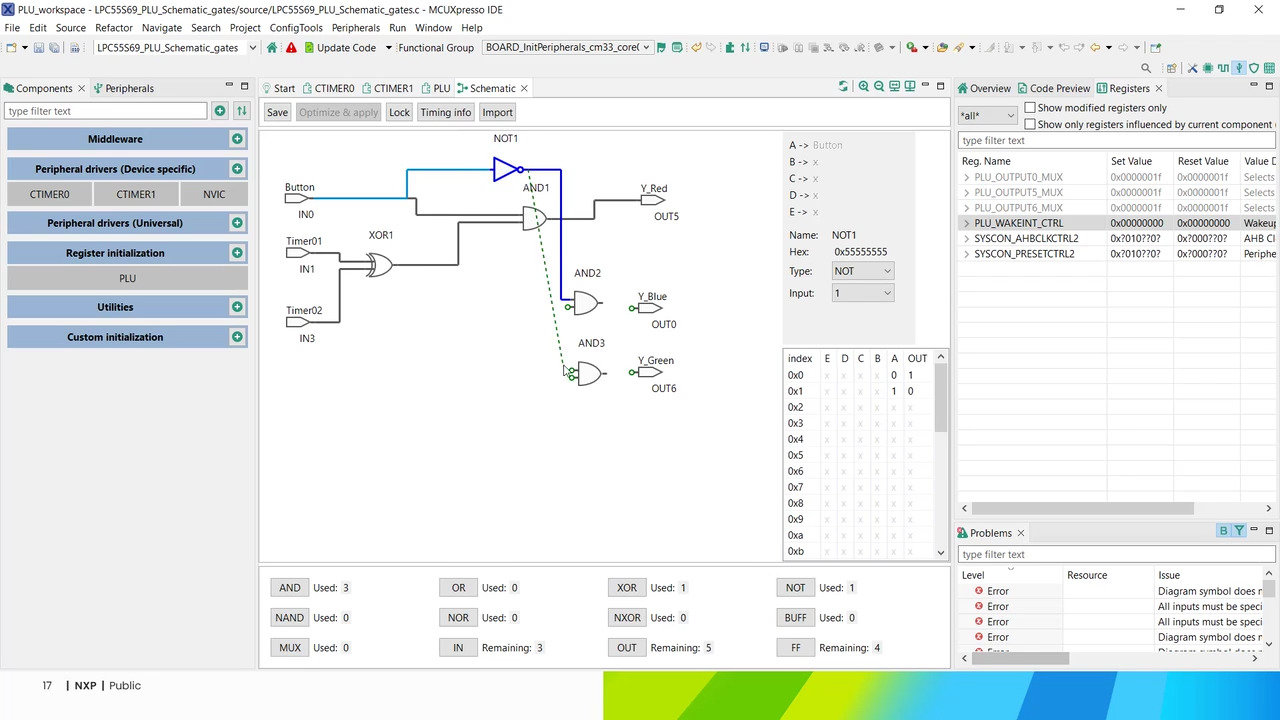

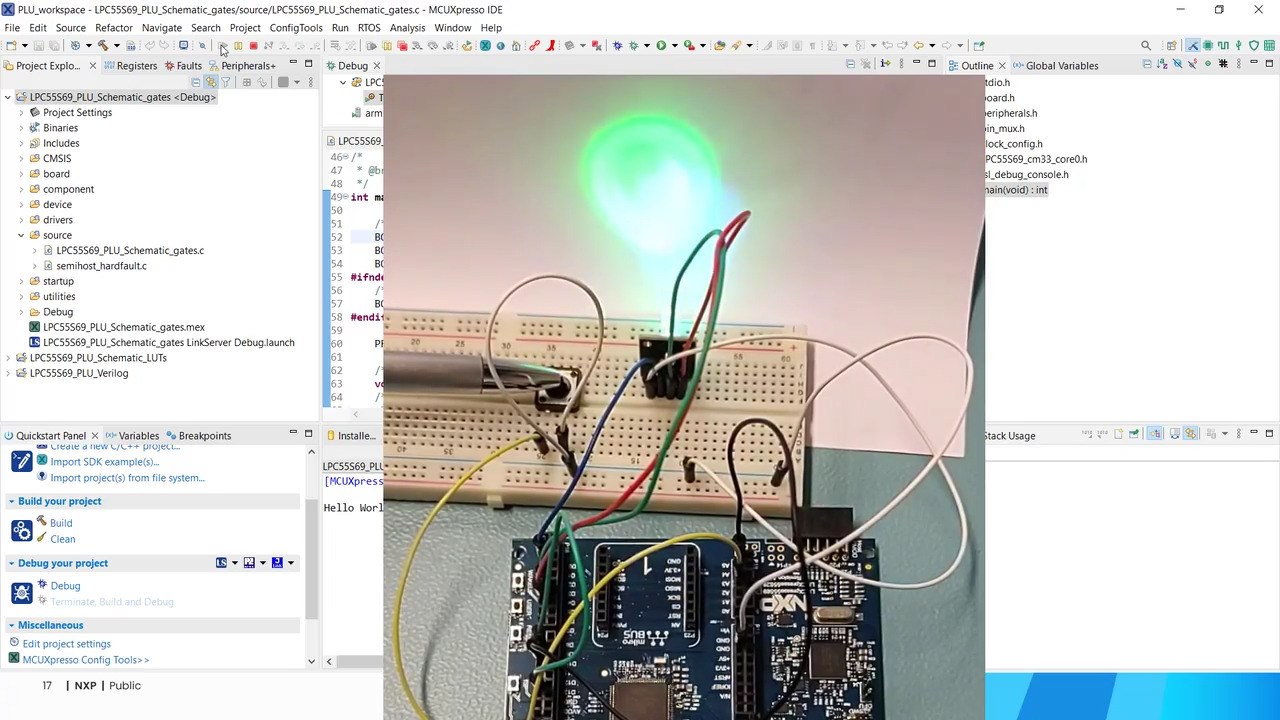

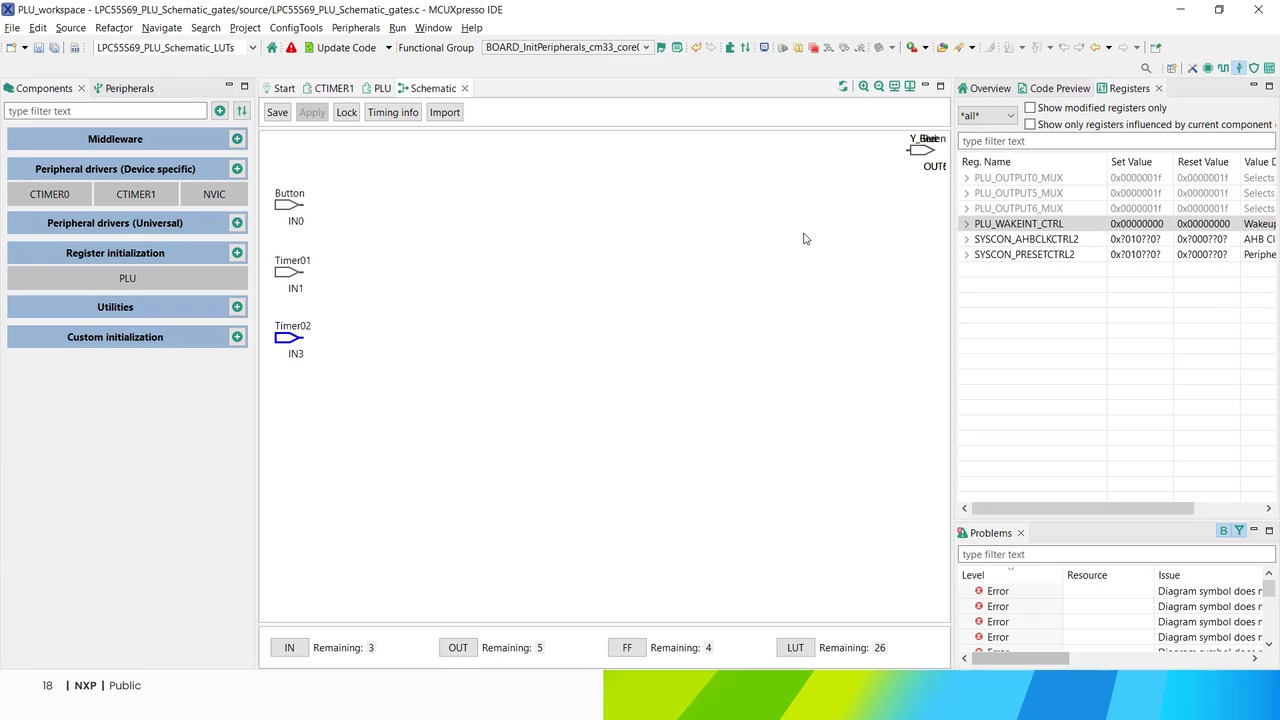

PLU enables you to create small logic networks that run independently on CPU. Lower the processing load or use it during deep-sleep mode. And configuration of this peripheral is very easy!

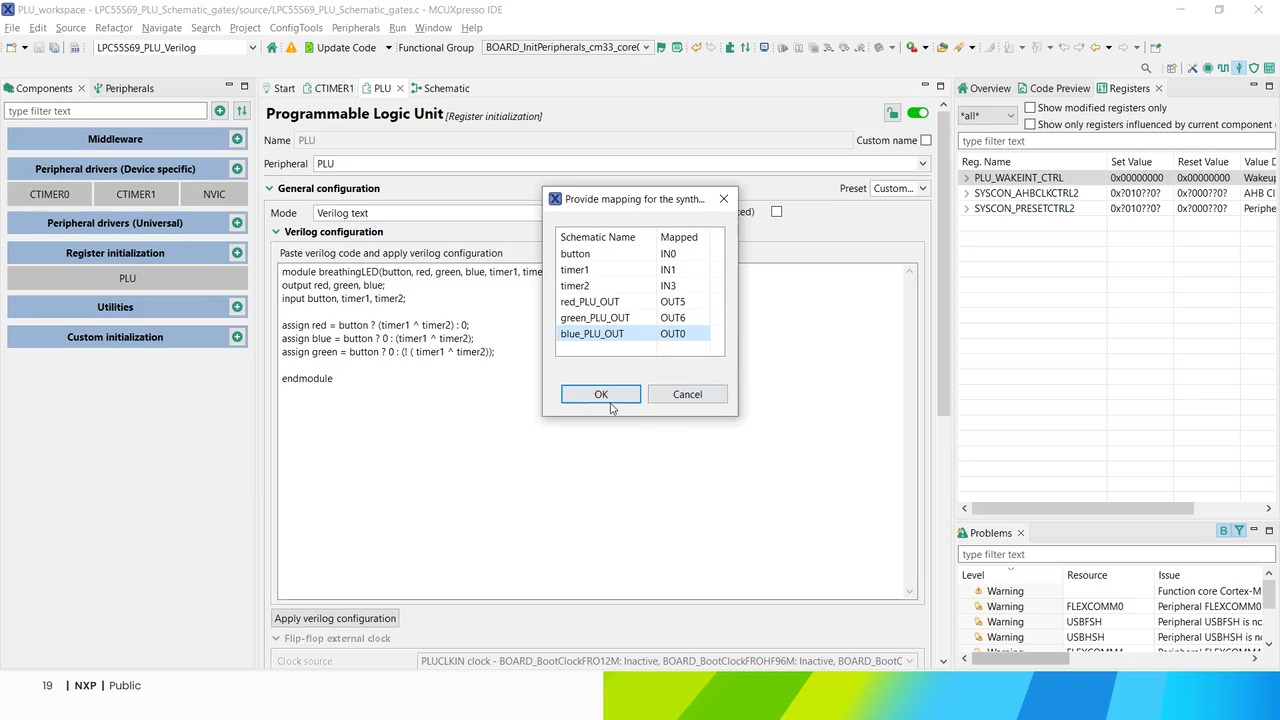

In this course you learn how to use MCUXpresso Config tools to configure PLU via schematic design either using logic gates or look up tables, or even via Verilog source code.

PLU enables you to create small logic networks that run independently on CPU. Lower the processing load or use it during deep-sleep mode. And configuration of this peripheral is very easy!

In this course you learn how to use MCUXpresso Config tools to configure PLU via schematic design either using logic gates or look up tables, or even via Verilog source code.

PLU enables you to create small logic networks that run independently on CPU. Lower the processing load or use it during deep-sleep mode. And configuration of this peripheral is very easy!

In this course you learn how to use MCUXpresso Config tools to configure PLU via schematic design either using logic gates or look up tables, or even via Verilog source code.

PLU enables you to create small logic networks that run independently on CPU. Lower the processing load or use it during deep-sleep mode. And configuration of this peripheral is very easy!

In this course you learn how to use MCUXpresso Config tools to configure PLU via schematic design either using logic gates or look up tables, or even via Verilog source code.

PLU enables you to create small logic networks that run independently on CPU. Lower the processing load or use it during deep-sleep mode. And configuration of this peripheral is very easy!

In this course you learn how to use MCUXpresso Config tools to configure PLU via schematic design either using logic gates or look up tables, or even via Verilog source code.

PLU enables you to create small logic networks that run independently on CPU. Lower the processing load or use it during deep-sleep mode. And configuration of this peripheral is very easy!

In this course you learn how to use MCUXpresso Config tools to configure PLU via schematic design either using logic gates or look up tables, or even via Verilog source code.

PLU enables you to create small logic networks that run independently on CPU. Lower the processing load or use it during deep-sleep mode. And configuration of this peripheral is very easy!

In this course you learn how to use MCUXpresso Config tools to configure PLU via schematic design either using logic gates or look up tables, or even via Verilog source code.

We are looking for ways to improve.

Ask our MCUXpresso Software and Tools community and get expert advice.

Subscribe to our newsletter to stay updated with our latest developments and if you need further assistance, we are here to help.

Subscribe Contact Support

Help us improve your experience on our site. We invite you to take our five-question survey.