# MPC8360EA MDS Processor Board

**User Manual**

Rev. 0.1 12/2006

# **Contents**

# Chapter 1 General Information

| 1.1                                 | Introduction                                | 1-1        |

|-------------------------------------|---------------------------------------------|------------|

| 1.2                                 | Working Configurations                      | 1-1        |

| 1.2.1                               | Stand-Alone Mode (Host)                     | 1-1        |

| 1.2.2                               | PIB Combined Mode (as Host)                 | 1-2        |

| 1.2.3                               | Agent Mode (in PC or PIB)                   | 1-2        |

| 1.3                                 | MPC8360EA MDS Processor Board               | 1-2        |

| 1.3.1                               | Features                                    | 1-2        |

| 1.3.2                               | External Connections                        | 1-3        |

| 1.3.3                               | Block Diagram                               | 1-5        |

| 1.4                                 | Definitions, Acronyms, and Abbreviations    | 1-6        |

| 1.5                                 | Related Documentation                       |            |

| 1.6                                 | Specifications                              | 1-7        |

|                                     | oter 2<br>ware Preparation and Installation |            |

| 2.1                                 | Unpacking Instructions                      | 2-1        |

| 2.2                                 | Installation Instructions.                  |            |

| 2.2.1                               | For Stand-Alone Mode                        |            |

| 2.2.2                               | For PIB Combined Mode                       |            |

| 2.2.3                               | For Agent Mode                              |            |

|                                     | oter 3<br>ory Map                           |            |

| 3.1<br>3.2                          | MPC8360EA MDS Processor Board Mapping       |            |

|                                     | oter 4<br>crols and Indicators              |            |

| 4.1                                 | Switches                                    | 4-1        |

| 4.2                                 | Jumpers                                     | <b>1-4</b> |

| 4.3                                 | LEDs                                        |            |

| r. J                                | Other Centrals and Indicators               | 1 /        |

| 4.4                                 | Other Controls and Indicators               | 4-6        |

|                                     | Push Buttons                                |            |

| 4.4<br>4.4.1<br><b>Chap</b>         |                                             |            |

| 4.4<br>4.4.1<br><b>Chap</b>         | Push Buttons                                | 4-6        |

| 4.4<br>4.4.1<br>Chap<br>Func        | Push Buttons                                | 4-6<br>5-1 |

| 4.4<br>4.4.1<br>Chap<br>Func<br>5.1 | Push Buttons                                | 4-6<br>5-1 |

MPC8360EA MDS Processor Board, Rev. 0.1

| 5.1.3  | MPC8360EA MDS Processor Board Reset Principles          |      |

|--------|---------------------------------------------------------|------|

| 5.1.4  | Power - On Reset                                        | 5-4  |

| 5.1.5  | Hard Reset                                              | 5-5  |

| 5.1.6  | COP/JTAG Port Hard - Reset (stand-alone only)           | 5-5  |

| 5.1.7  | Manual Hard Reset                                       | 5-5  |

| 5.1.8  | Manual Soft Reset.                                      | 5-5  |

| 5.2    | Default Settings.                                       | 5-6  |

| 5.3    | Clocking                                                | 5-6  |

| 5.4    | FPGA - Board Control & Status Registers (BCSR)          | 5-8  |

| 5.4.1  | BCSR0 - Status Register                                 |      |

| 5.4.2  | BCSR1 - Status Register                                 | 5-9  |

| 5.4.3  | BCSR2 - Status Register                                 |      |

| 5.4.4  | BCSR3 - Status Register                                 | 5-10 |

| 5.4.5  | BCSR4 - Status Register                                 | 5-10 |

| 5.4.6  | BCSR5 - Status Register                                 | 5-11 |

| 5.4.7  | BCSR6 - Status Register                                 |      |

| 5.4.8  | BCSR7 - Status Register                                 | 5-12 |

| 5.4.9  | BCSR8 - Status Register                                 | 5-12 |

| 5.4.10 | BCSR9 - Status Register                                 | 5-13 |

| 5.4.11 | BCSR10 - Status Register                                | 5-15 |

| 5.4.12 | BCSR11 - Status Register                                | 5-16 |

| 5.4.13 | BCSR12 - Status Register                                | 5-16 |

| 5.4.14 | BCSR13 - Status Register                                | 5-17 |

| 5.4.15 | BCSR14 - Board Status Register 14                       | 5-18 |

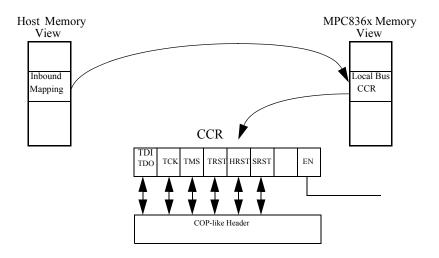

| 5.4.16 | CCR - COP Control Register                              | 5-18 |

| 5.5    | External Connections                                    | 5-19 |

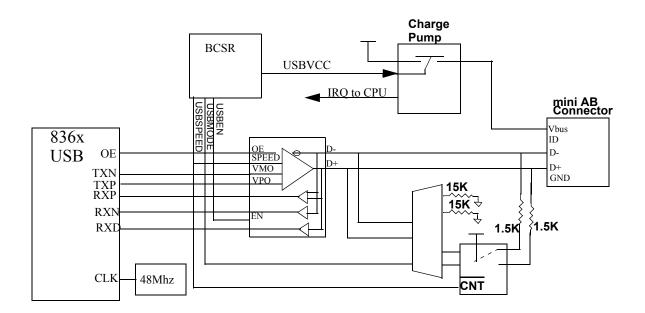

| 5.5.1  | P1 - MiniAB USB Connector                               | 5-19 |

| 5.5.2  | P2 - DUART Port                                         | 5-20 |

| 5.5.3  | P3 - 32-bit PCI Edge Connector                          | 5-20 |

| 5.5.4  | P4, P5, P6 - Logic Analyzer Connectors                  | 5-20 |

| 5.5.5  | P7 - SMB Connector                                      | 5-21 |

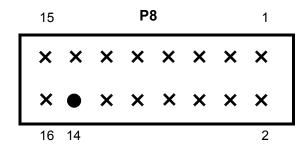

| 5.5.6  | P8 - Debug COP Connector                                | 5-21 |

| 5.5.7  | P9 - FPGA's In-System-Programming (ISP)                 | 5-22 |

| 5.5.8  | P10 - Power Connector                                   |      |

| 5.5.9  | J1,J2 - GETH Port Connector                             | 5-23 |

| 5.6    | PCI                                                     |      |

| 5.6.1  | General                                                 |      |

| 5.6.2  | PCI Setting when MPC8360EA MDS Processor Board is Host  | 5-24 |

| 5.6.3  | PCI Setting when MPC8360EA MDS Processor Board is Agent |      |

| 5.7    | DDR                                                     |      |

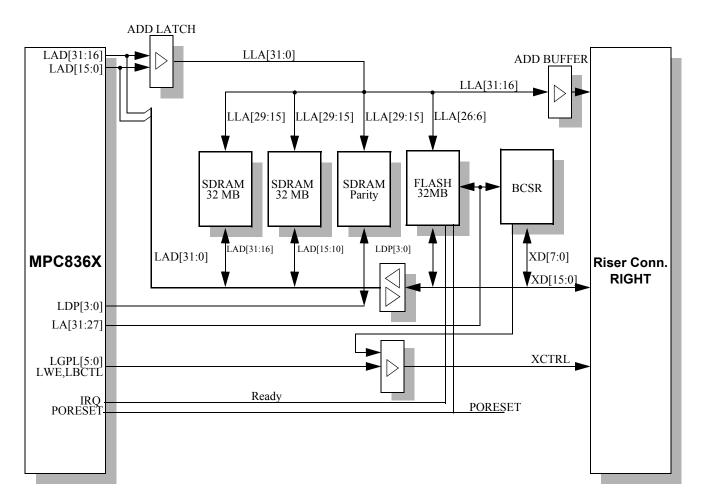

| 5.8    | Local Bus                                               | 5-27 |

| 5.8.1  | Address Latch/ Data Transceiver                         |      |

| 5.8.2  | SDRAM                                                   |      |

| 5.8.3  | Flash Memory                                            |      |

| 5.9    | GETH                                                    | 5-29 |

ii Freescale Semiconductor

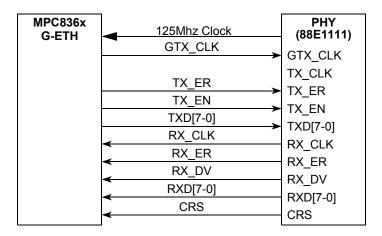

| 5.9.1        | GMII Interface                                       | 5-30  |

|--------------|------------------------------------------------------|-------|

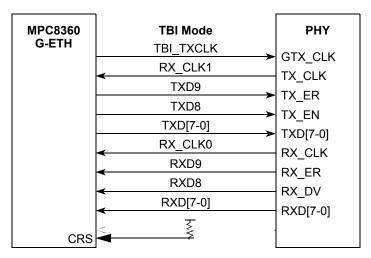

| 5.9.2        | Ten Bit Interface (TBI)                              | 5-30  |

| 5.9.3        | Reduced Pin Count GMII (RGMII)                       | 5-31  |

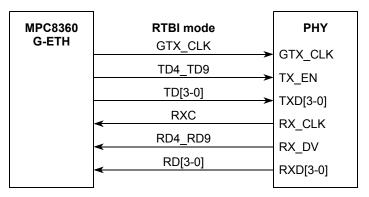

| 5.9.4        | Reduced Ten Bit Interface (RTBI)                     | 5-32  |

| 5.9.5        | RGMII or RTBI via the PIB                            | 5-33  |

| 5.9.6        | RMII via the PIB                                     | 5-33  |

| 5.9.7        | Summary                                              | 5-35  |

| 5.10         | USB                                                  | 5-36  |

| 5.11         | Debugging Applications                               | 5-38  |

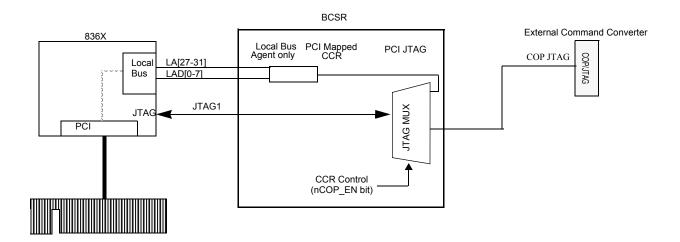

| 5.11.1       | Stand-Alone and on PIB                               | 5-38  |

| 5.11.2       | Inserted in PC                                       | 5-38  |

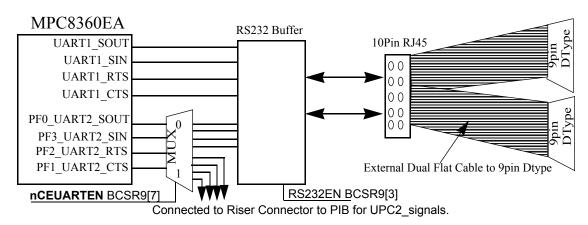

| 5.12         | UART Ports                                           | 5-40  |

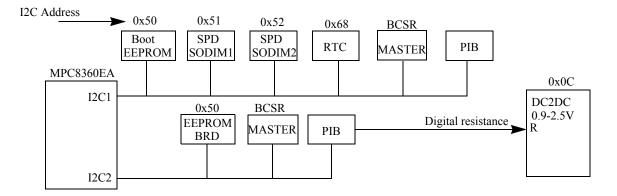

| 5.13         | I2C (Dual) Port                                      | 5-41  |

| 5.13.1       | I2C-1                                                | 5-41  |

| 5.13.2       | I2C-2                                                | 5-42  |

| 5.14         | External Interrupts                                  | 5-42  |

| 5.14.1       | ABORT Interrupt                                      | 5-43  |

| 5.14.2       | PIB Interrupt                                        | 5-43  |

| 5.14.3       | PCI Interrupt                                        | 5-43  |

| 5.14.4       | RTC Interrupt                                        | 5-43  |

| 5.14.5       | FLASH Interrupt                                      | 5-43  |

| 5.14.6       | JTAG/COP Interrupt                                   | 5-43  |

| 5.14.7       | GETH Interrupt                                       | 5-43  |

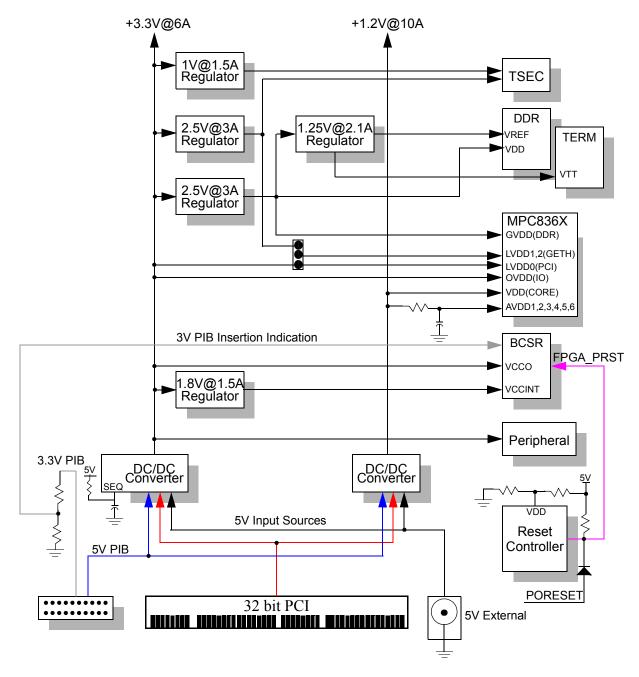

| 5.15         | Power Supply                                         | 5-43  |

| 5.15.1       | Primary Power Supply                                 | 5-44  |

| 5.15.2       | MPC8360EA MDS Processor Board Power Supply Structure | 5-44  |

| 5.15.3       | Power Supply Operation.                              | 5-44  |

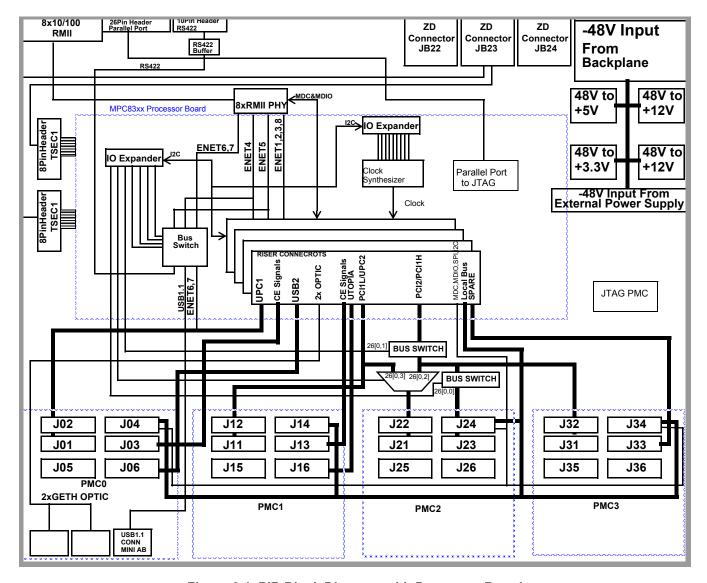

| Chap<br>Work | iter 6<br>ing with the PIB                           |       |

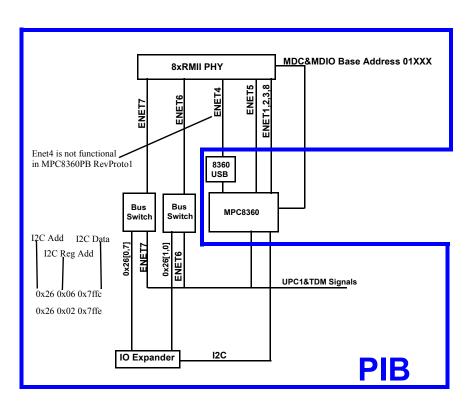

| 6.1          | Platform I/O Board Concept                           | . 6-1 |

| 6.2          | MPC8360EA MDS Processor Board as Host.               |       |

| 6.3          | MPC8360EA MDS Processor Board as Agent.              |       |

| 6.4          | MPC8360EA MDS Processor Board - PIB Signals          |       |

| Chap         |                                                      | . 0 2 |

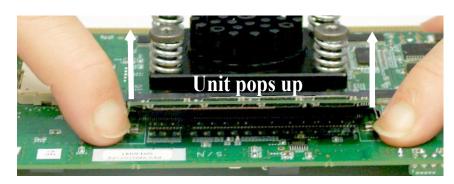

| 7.1          | Replacing Flash Memory                               | . 7-1 |

| 7.1.1        | Cleaning Flash Memory                                |       |

| 7.2          | Replacing SODIMM units                               |       |

| 7.3          | Replacing MPC860EA Processor.                        |       |

Freescale Semiconductor iii

# Chapter 1 General Information

#### 1.1 Introduction

This document describes the MPC8360EA MDS Processor Board; in its stand-alone operating mode, in its operating mode via a PCI slot in a PC, and in its operating mode on the "PowerQUICC MDS Platform I/O Board (PIB)".

The MPC8360EA MDS Processor Board is an application devlopment system that provides a complete debugging environment for engineers developing applications for the MPC8360 series of Freescale processors.

The MPC8360EA is a cost-effective, highly integrated communications processor that addresses the needs of the networking, wireless infrastructure and telecommunications markets. Target applications include next generation DSLAMs, network interface cards for 3G base stations (Node Bs), routers, media gateways and high end IADs. The 8360EA extends current PowerQUICC II offerings, adding higher CPU performance, additional functionality, faster interfaces and interworking between ATM and Ethernet based protocols while addressing the requirements related to time-to-market, price, power, and package size. The MPC8360EA can be used for the control plane along with data plane functionality.

The MPC8360EA MDS Processor Board includes various peripherals, such as data input/output devices (GETH, USB, DUART), memories (DDR, SDRAM (optional), Serial EEPROM, FLASH and BCSR registers), and control switches and LED indicators.

Using its on-board resources and debugging devices, a developer is able to upload code, run the code, set breakpoints, display memory & registers and connect his own proprietary hardware to be incorporated into a target system that uses the MPC8360EA as a processor.

The software application developed for the MPC8360EA can be run in a "bare bones" operation (with only the MPC8360EA processor), or with various input or output data streams, such as from the GETH connection, PCI or the USB connections. Results can be analyzed using the *Code Warrior*<sup>®</sup> debugger in addition to using other methods for directly analyzing the input or output data stream. The BSP is built using the Linux OS.

This board can also be used as a demonstration tool for the developer. For instance, the developer's application software may be programmed into its Flash memory and run in exhibitions.

# 1.2 Working Configurations

## 1.2.1 Stand-Alone Mode (Host)

The MPC8360EA MDS Processor Board can be run in a stand-alone mode, like other application development systems, with direct connections to debuggers (via a JTAG/COP connector and JTAG/Parallel Port command converter), power supply, and the GETH, MiniAB USB and Dual RS-232 (DUART) connections. In this mode, the MPC8360EA MDS Processor Board acts as a Host.

### 1.2.2 PIB Combined Mode (as Host)

The MPC8360EA MDS Processor Board can be connected to the PIB - the Platform I/O Board, which allows it to be used in a back plane, and provides room and connections for additional modules. There are many modules, some of which are TDM or ATM modules. There can also be additional Processor Boards from the MPC83xx family, acting as Agents. This capability allows the MPC8360EA processor on the MPC8360EA MDS Processor Board to act as a Host for Agent processors in the MPC83xx family.

Power for the MPC8360EA MDS Processor Board in this case is provided via the PIB. The PIB also provides an additional 2x4 twisted pair for GETH signals to be connected via the back plane (if used). Optical signals via 2x SFP connectors for GETH on the front plane side of the PIB are also provided. The MPC8360EA MDS Processor Board can be connected to a PC in this configuration (via a parallel port connector), without needing an external command converter.

### 1.2.3 Agent Mode (in PC or PIB)

Using its PCI edge connector, the MPC8360EA MDS Processor Board can be inserted into a PC, or onto the PIB. Power and debugging are supplied from the PC (no command converter necessary). Other external connections are the same as in the Stand-Alone Mode. In this mode, the MPC8360EA MDS Processor Board acts as an Agent.

#### 1.3 MPC8360EA MDS Processor Board

#### 1.3.1 Features

- Supports MPC8360EA running up to 533MHz at 1.2V Core voltage.

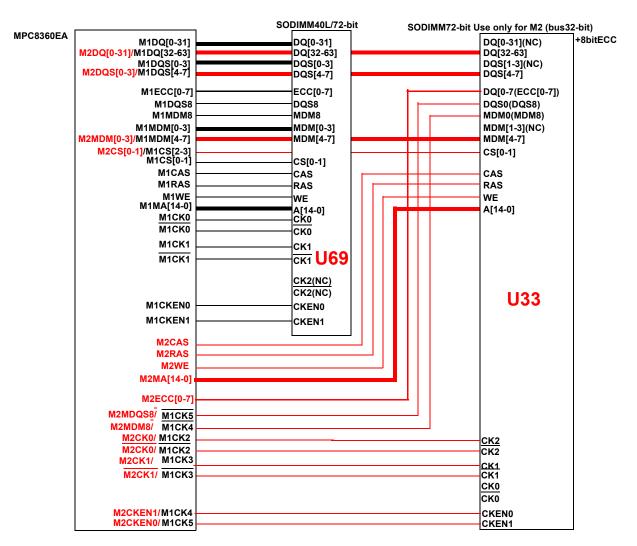

- DDR 72-bit on SODIMM, at a rate up to 400MHz or 2 x DDR 40bit units on two SODIMM, each at a rate up to 400MHz.

- PCI edge connector interfaces with 32bit PCI bus (used when inserted in a PC, or as an agent on the PIB).

- Two 10/100/1000Mb/sec Ethernet Phys on GETH ports.

- USB 1.1 Transceiver.

- Dual RS232 transceiver on one DUART port.

- Local Bus interface:

- 133MHz SDRAM memory (implemented using three units), 64Mbyte size with parity.

- One 32Mbyte (expandable) Flash with 16bit port size in socket.

- Address Latch and Buffers to support slow devices on the PIB Board.

- Mictor Logic Analyzer Connectors on mux bus for evaluation only.

- Three Hi-speed Riser Connectors to enable connection to the PIB Board.

- Debug port access via dedicated 16-pin connector (COP), via PCI port or from parallel port interface on the PIB.

- One I2C port for EEPROM 256Kbyte, Real Time Clock (RTC) and SODIMM SPD EEPROM A second I2C port is used to connect to the Board Revision Detect 256Kbyte EEPROM.

1-2 Freescale Semiconductor

- Can function in one of three configurations:

- Stand-alone.

- As a PCI add-in card for a standard PC computer, or as an agent on the PIB.

- PIB combined mode development platform with Processor Board (as a Host) and PIB connected together.

- Board Control and Status Register (BCSR) implemented in Xilinx FPGA.

- Three power options:

- Main 5V power is fed from external power supply for stand-alone mode.

- Power from PC supply when acting as a PCI add-in card.

- Power from the PIB when PIB and Processor Boards are combined.

- PCI add-in card form factor dimensions: 285mm x 106mm.

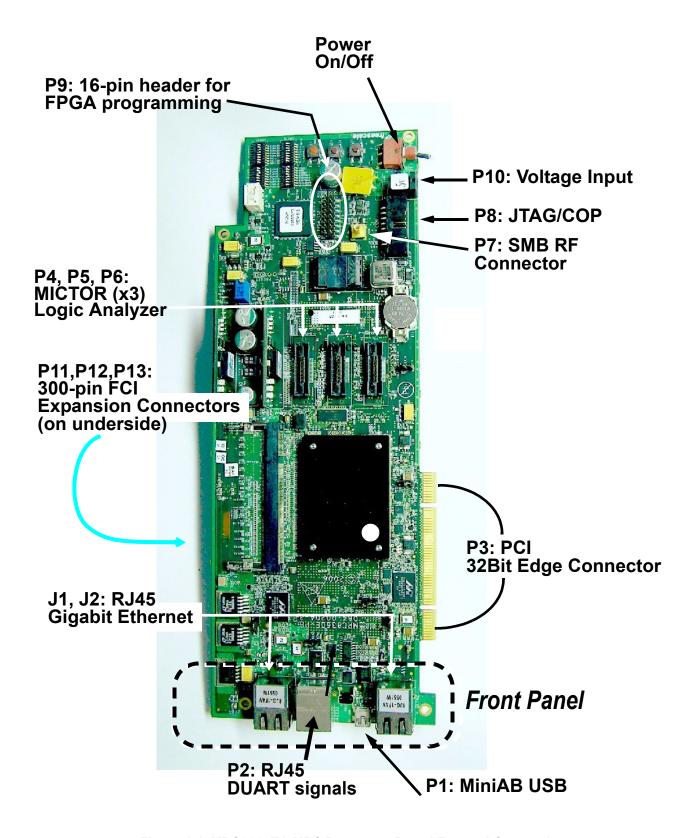

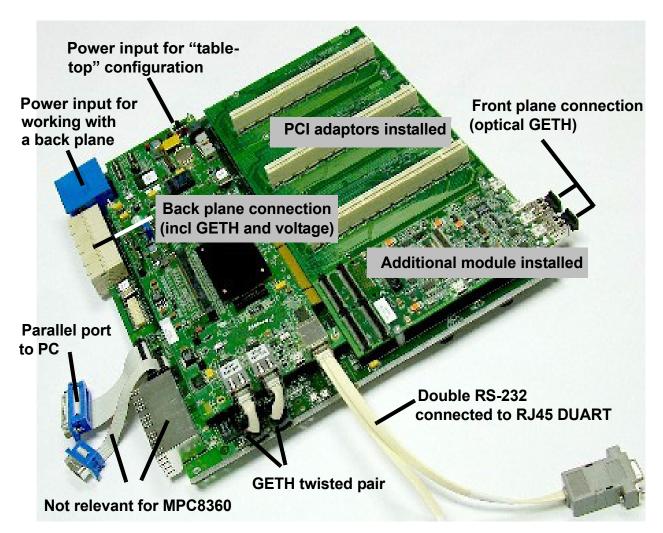

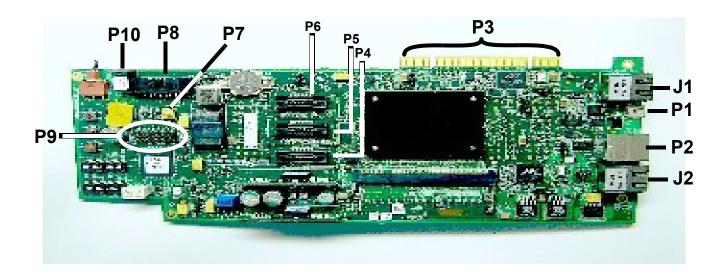

#### 1.3.2 External Connections

The MPC8360EA MDS Processor Board interconnects with external devices via the following set of connectors:

- P1 MiniAB USB connector.

- P2 RJ45 (10-pin) for DUART signals.

- P3 32bit PCI Edge Connector.

- P4, P5, P6 Three Logic Analyzer MICTOR Connectors.

- P7 SMB RF Connector for external pulse generator.

- P8 16-pin COP/JTAG Connector.

- P9 16-pin header for FPGA In-System Programming.

- P10 Voltage Input

- P11,P12,P13 300-pin FCI Expansion Connectors.

- J1,J2 RJ45 8-pin Gigabit Ethernet Connectors.

Freescale Semiconductor 1-3

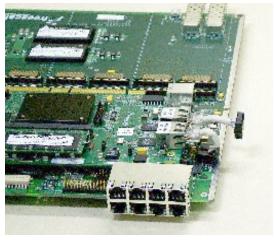

Figure 1-1. MPC8360EA MDS Processor Board External Connections

MPC8360EA MDS Processor Board, Rev. 0.1

1-4 Freescale Semiconductor

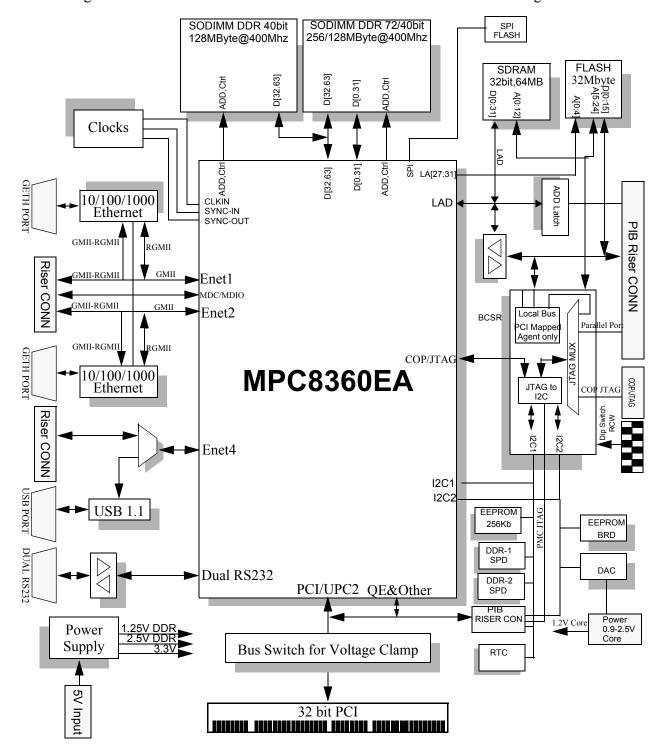

## 1.3.3 Block Diagram

The block diagram of the MPC8360EA MDS Processor Board is shown below in Figure 1-2.

Figure 1-2. MPC8360EA MDS Processor Board Block Diagram

Freescale Semiconductor 1-5

# 1.4 Definitions, Acronyms, and Abbreviations

| ADS    | Application Development System             |  |  |

|--------|--------------------------------------------|--|--|

| BCSR   | Board Control and Status Register          |  |  |

| BRD    | Board Revision Detect (I2C EEPROM)         |  |  |

| BSP    | Board Support Package                      |  |  |

| CCR    | COP Control Register (FPGA)                |  |  |

| COP    | Common On-chip Processor (JTAG Debug Port) |  |  |

| CS     | Chip Select                                |  |  |

| CW     | Code Warrior <sup>®</sup> IDE for PowerPC  |  |  |

| DAC    | Digital-to-Analog Converter                |  |  |

| DDR    | Double Data Rate                           |  |  |

| DIP    | Dual-In-Line Package.                      |  |  |

| DMA    | Direct Memory Access                       |  |  |

| DUART  | Dual UART                                  |  |  |

| EEPROM | Electrical Erasable Programmable Memory    |  |  |

| FCFG   | Flash Configuration Select                 |  |  |

| FCI    | Type of Riser Connector                    |  |  |

| FLASH  | Non volatile reprogrammable memory.        |  |  |

| FPGA   | Field-Programmable Gate Array              |  |  |

| GbE    | Gigabit Ethernet                           |  |  |

| GETH   | Gigabit Ethernet                           |  |  |

| GPCM   | General Purpose Chip-select Machine        |  |  |

| GPL    | General Purpose Line                       |  |  |

| I2C    | Philips Semi Serial Bus                    |  |  |

| LBIU   | Local Bus Interface Unit                   |  |  |

| LED    | Light Emitting Diode                       |  |  |

| Isb    | least significant bit                      |  |  |

| MII    | Media Independent Interface                |  |  |

| GMII   | General Media Independent Interface        |  |  |

| JTAG   | Joint Test Access Group                    |  |  |

| OTG    | On-the-Go                                  |  |  |

| PC     | IBM-compatible Personal Computer           |  |  |

| PCI    | Peripheral Components Interconnect         |  |  |

|        |                                            |  |  |

MPC8360EA MDS Processor Board, Rev. 0.1

1-6 Freescale Semiconductor

| Phy      | Physical Layer                                                  |  |  |

|----------|-----------------------------------------------------------------|--|--|

| PIB      | Platform I/O Board - expands the ADS functionality.             |  |  |

| PSRAM    | Pseudo-Static Random Access Memory                              |  |  |

| PSU      | Power Supply Unit                                               |  |  |

| RCW(L,H) | Reset Configuration Word (Low/High)                             |  |  |

| RGMII    | Reduced General Media Independent Interface                     |  |  |

| RTC      | Real Time Clock                                                 |  |  |

| SDRAM    | Synchronous Dynamic Random Access Memory                        |  |  |

| SMB      | Type of Mini-RF connector                                       |  |  |

| SODIMM   | Mini DIMM Form Factor                                           |  |  |

| SPD      | Serial Present Detect                                           |  |  |

| TSEC     | Triple Speed Ethernet Controller                                |  |  |

| ULPI     | UTMI+ Low Pin Interface                                         |  |  |

| UPM      | User Programmable Machine                                       |  |  |

| USB      | Universal Serial Bus                                            |  |  |

| ZD       | Zero Delay clock buffer, with internal PLL for skew elimination |  |  |

## 1.5 Related Documentation

- MPC8360EA HW Specification

- MPC8360EA User's Manual

- PowerQUICC MDS Platform I/O Board User's Manual

- MPC8360EA Hardware Getting Started

# 1.6 Specifications

The MPC8360EA MDS Processor Board specifications are given in Table 1-1.

Table 1-1. MPC8360EA MDS Processor Board specifications

| CHARACTERISTICS    | SPECIFICATIONS                                     |

|--------------------|----------------------------------------------------|

| Power requirements | Stand-Alone Mode: 5V @ 3A external DC power supply |

|                    | PIB Combined Mode: Power supplied by PIB           |

|                    | Working in PC: Power supplied by PC                |

Table 1-1. MPC8360EA MDS Processor Board specifications

| SPECIFICATIONS                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Internal clock runs at 533MHz @ 1.2V (note that the board supports any working frequency that the MPC8360EA supports. To change the working frequency, see Section 5.3) |

| 2 x 128MB space 40bit wide (32bits data, 8 bits ECC) in two SODIMM-200's . Data rate 400MHz.                                                                            |

| 64MB space 32bit wide + 4bit parity implemented in three SDRAM parts. 133MHz clock.                                                                                     |

| 32MB space 16bits wide.                                                                                                                                                 |

| 16-registers, 8bits wide.                                                                                                                                               |

| Four banks with 16bit- Address bus, 16bit- Data bus connected to riser connectors                                                                                       |

| 0°C - 70°C                                                                                                                                                              |

| -25°C to 85°C                                                                                                                                                           |

| 5% to 90% (non-condensing)                                                                                                                                              |

| 285 mm<br>106 mm<br>16 mm                                                                                                                                               |

|                                                                                                                                                                         |

# **Chapter 2 Hardware Preparation and Installation**

This chapter provides unpacking instructions, hardware preparation, and installation instructions for the MPC8360EA MDS Processor Board, including all three configurations: Stand-Alone, PIB Combined Mode, and Agent Mode (either on the PIB, or inserted in a PC). For more details on hardware preparation, see the "Hardware Getting Started" document for the MPC8360EA MDS Processor Board.

## 2.1 Unpacking Instructions

#### **NOTE**

If the shipping carton is damaged upon receipt, request carrier's agent to be present during unpacking and inspection of equipment.

#### **CAUTION**

AVOID TOUCHING AREAS OF INTEGRATED CIRCUITRY; STATIC DISCHARGE CAN DAMAGE CIRCUITS.

- 1. Unpack equipment from shipping carton.

- 2. Refer to packing list and verify that all items are present.

- 3. Save packing material for storing and reshipping of equipment.

#### 2.2 Installation Instructions

Do the following *in the order indicated* to install the MPC8360EA MDS Processor Board properly:

- 1. Verify that Jumpers and Switches are in default positions. For default positions, see the "Hardware Getting Started Guide" document for the MPC8360EA MDS Processor Board.

- 2. Determine in which working configuration you will operate the MPC8360EA MDS Processor Board:

- Stand-Alone continue from Section 2.2.1

- PIB Combined Mode, with the PIB Board continue from Section 2.2.2

- Agent Mode continue from Section 2.2.3

#### 2.2.1 For Stand-Alone Mode

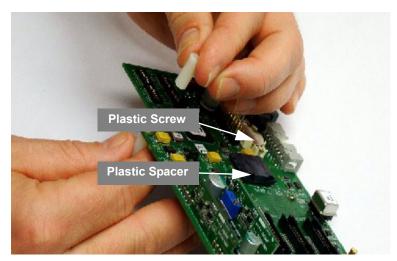

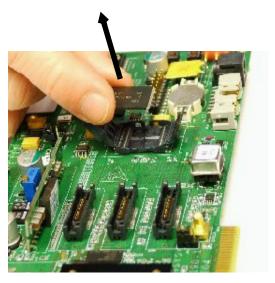

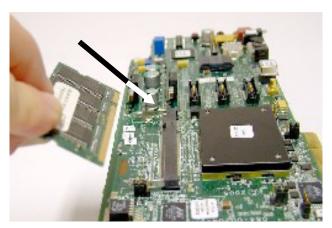

- 1. For Stand-Alone Mode only: Connect the four plastic spacers. See Figure 2-1.

- 2. Connect external cables in accordance with your development needs.

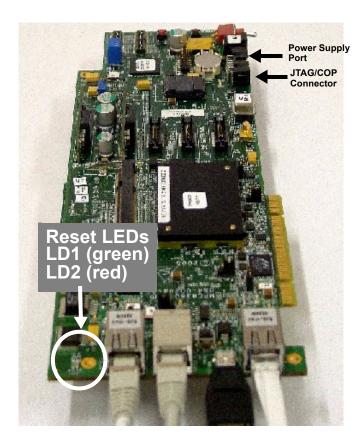

- 3. Connect PSU (to P10), and turn the power on-off switch to ON.

- 4. Verify that LD1 and LD2 turn on and turn off (see Figure 2-2 for location). They should be on for only a few moments. This indicates that the board has successfully completed the boot-up sequence.

Figure 2-1. Connecting Plastic Spacers

Figure 2-2. Boot-Up sequence: LD1 and LD2 (turn on, then off)

2-3

#### 2.2.2 For PIB Combined Mode

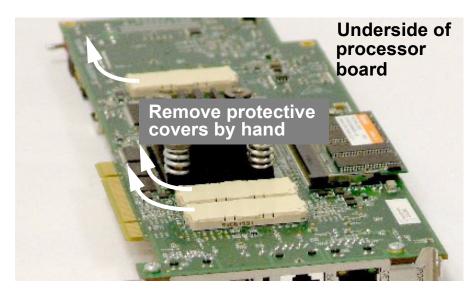

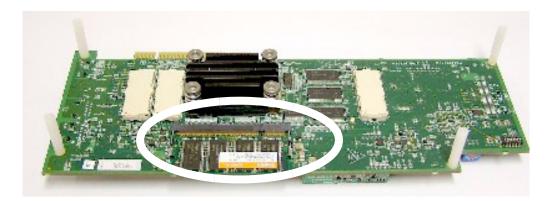

- 1. Remove protective covers from the 300-pin connectors on the bottom side of the processor board (See Figure 2-3.).

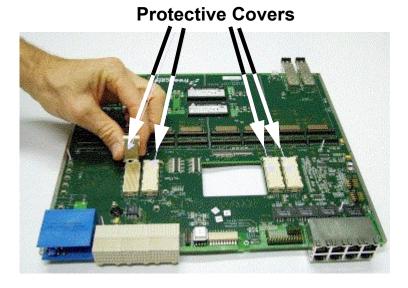

- 2. Remove protective covers from the 300-pin connectors on the PIB board (see Figure 2-4).

Figure 2-3. Remove Protective Covers from 300-pin connectors (underside of MPC8360EA MDS Processor Board shown)

Figure 2-4. Remove Protective Covers from 300-pin connectors

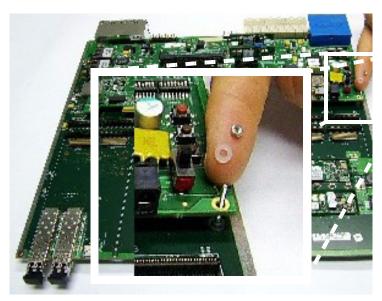

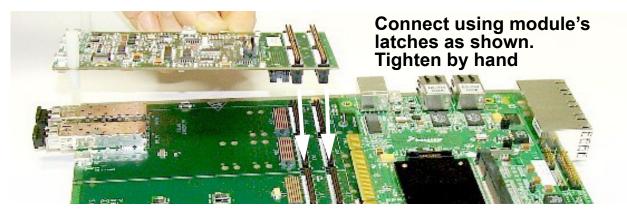

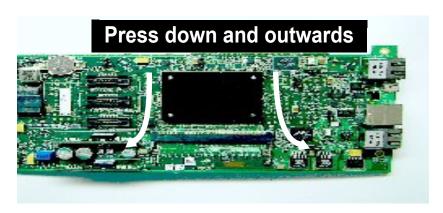

- 3. Connect processor board to PIB board as shown in Figure 2-5.

- 4. Ensure a tight fit by pressing down on the processor board **by hand only** until the pins engage (see Figure 2-5.)

- 5. Manually fasten the four screws as shown in Figure 2-6.

Figure 2-5. Connect Processor board to PIB and press down with fingers <sup>1</sup>

Figure 2-6. Fasten the four tightening screws

MPC8360EA MDS Processor Board, Rev. 0.1

Freescale Semiconductor 2-5

<sup>1.</sup> Although an MPC8349 Processor Board is shown, this step is the same for the MPC8360EA

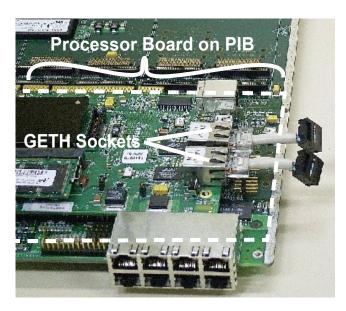

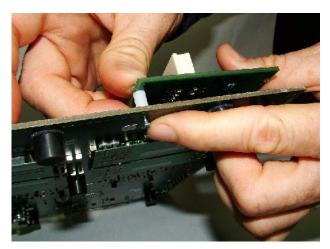

6. If you will be working with a back plane, and wish GETH signals to traverse either the back plane connection, or the front plane optical connection, connect the two GETH sockets on the MPC8360EA MDS Processor Board with sockets on the PIB board as shown in Figure 2-7 and Figure 2-8.

Note that if you do not do this, you can still connect GETH cables directly to the Processor board's sockets, if they are accessible in your laboratory configuration.

GETH Interconnecting Cables

Figure 2-7. Insert GETH interconnecting cables to GETH sockets on Processor board

GETH Interconnecting Cable connected

Figure 2-8. Connect GETH interconnecting cables to sockets on PIB

7. Connect the power supply to the voltage input as shown in Figure 2-9.

2-6 Freescale Semiconductor

Figure 2-9. Connecting Power input to the PIB

2-7

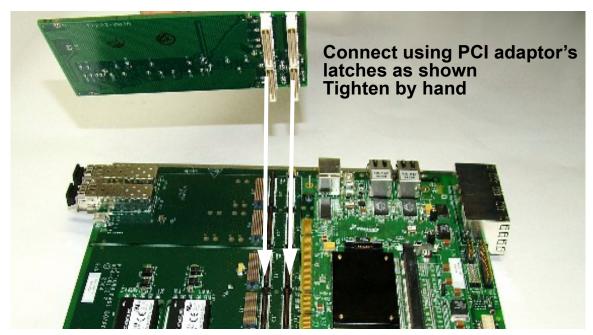

8. If you wish to work with a module connected to a PCI adaptor, follow the illustrations in Figure 2-10, Figure 2-11, and Figure 2-12 to connect these items to the PIB.

Note that the ATM card can only be inserted in the PMC0 and PMC1 (PMC0 shown). The PCI adaptors can be inserted in any section, for up to 4 PCI adaptors, if space allows.

Figure 2-10. Connecting module card to PIB

Figure 2-11. Connecting PCI adaptor to PIB

Figure 2-12. Inserting spacers between PCI card and PIB

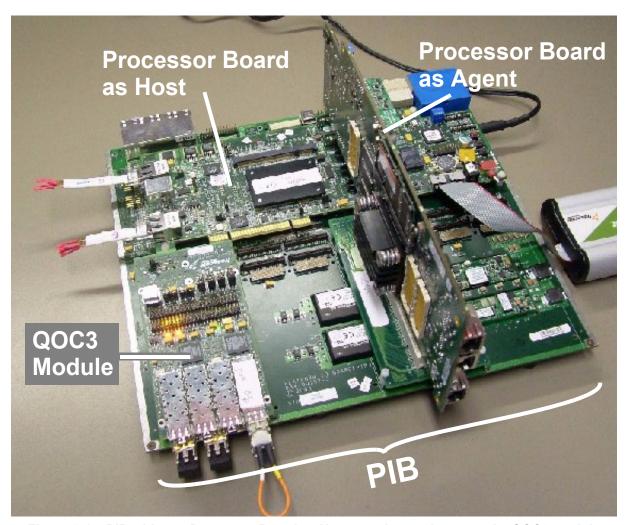

9. The fully assembled PIB-Processor board is shown in Figure 2-13, which also shows the PIB external connections relevant when the MPC8360EA is used.

All external connections of the Processor board are active when the Processor board is installed on the PIB, except the voltage input (receives power from the PIB power input, or the back plane only), and the JTAG/COP connection (P8), which is replaced by the parallel port connection to a PC.

In Figure 2-13, three PCI adaptors and one additional module are shown installed on the PIB. The PCI cards are ready to receive any PCI- compatible board, including an 83xx Processor board, installed in this case in the same manner as they are in a PC. Using this system, these boards (up to three) function as agents, while the Processor board already installed functions as a host. This allows you to take advantage of the parallel processing capabilities of the 83xx line of products.

- 10. Operate *Code Warrior*<sup>®</sup> to verify that the processor board has been installed properly.

- 11. Connect power cable to the PIB, and external cables in accordance with your development needs.

- 12. Verify that LD1 and LD2 turn on and then turn off (see Figure 2-2 for location). They should be on for only a few moments. This indicates that the board has successfully undergone the boot-up sequence.

Figure 2-13. Fully Assembled Combined system: PIB, Processor Board, additional module, and PCI cards

### 2.2.3 For Agent Mode

1. **Installed in a PC**: Insert the MPC8360EA MDS Processor Board into a PC, using its PCI edge connector.

As an agent on the PIB: Insert PCI adaptor or adaptors into the PIB as shown in Figure 2-11 and Figure 2-12, then insert the Processor Board into an adaptor, using its PCI edge connector, as shown in Figure 2-13.

- 2. Operate *Code Warrior*® to verify that the processor board has been installed properly.

- 3. Connect external cables in accordance with your development needs.

- 4. Verify that LD1 and LD2 turn on and then turn off (see Figure 2-2 for location). They should be on for only a few moments. This indicates that the board has successfully undergone the boot-up sequence.

Figure 2-14. PIB with one Processor Board as Host, another as Agent, and a QOC3 module

2-12 Freescale Semiconductor

# Chapter 3 Memory Map

## 3.1 MPC8360EA MDS Processor Board Mapping

The MPC8360EA Memory Controller governs all access to the processor memory slaves. Consequently the memory map may be reprogrammed according to user needs. The memory map defined in Table 3-1 is only a recommendation. The user can choose to work with alternative memory mapping. It should be noted that the described mode is supported by Metrowerks' *Code Warrior*® debug tool.

After performing Hard Reset, the debug host may initialize the memory controller via the JTAG/COP connector so this allows additional access to bus addressable peripherals. The DDR72, 2xDDR36, SDRAM and FLASH memory respond to all types of memory access - program/data and Direct Memory Access (DMA).

The following table (Table 3-1) presents the Memory Map of the MPC8360EA MDS Processor Board. It includes an address range for each target that utilizes memory, the "target" itself on the board, the specific device that is used to implement the target's function, the amount of memory allotted to the target (volume in bytes), and its port size (in bits). Note the information on the DDR SDRAM. There are two main options: using one 72-bit device, or one or two 36-bit devices. The one 72-bit device can be used to implement a memory capacity of 256MB, or 1GB. Alternatively, a memory capacity of 256MB (128 + 128) can be implemented using two 36-bit devices.

Table 3-1. MPC8360EA MDS Processor Board Memory Map

| No. | Address Range                                                                          | Target                                       | Device Name                                                                                                                             | Volume<br>in Bytes | Port<br>Size<br>in Bits |

|-----|----------------------------------------------------------------------------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------------|

|     |                                                                                        | DDR SDRAM :                                  |                                                                                                                                         |                    |                         |

| 0   | 00000000 - 0FFFFFF<br>(for 256MB volume)<br>(000000000 - 3FFFFFFF)<br>(for 1GB volume) | Main SODIMM<br>MEMC1CS0, MEMC1CS1<br>72-bit  | WV3HG32M72EEU403PD4GG with ECC (for 256MB space) - or - WV3HG128M72EEU-PD4 with ECC (for 1GB space) (optional, not supplied with board) | 256MB<br>(1GB)     | 64+8<br>ECC             |

| 1   | 00000000 - 0FFFFFF<br>(for 128MB volume)                                               | Main SODIMM<br>MEMC1CS0, MEMC1CS1<br>40-bit  | WV3HG32M72EEU403PD4GG<br>w/o ECC                                                                                                        | 128MB              | 32+8<br>ECC             |

| 2   | 00000000 - 0FFFFFF<br>(for additional 128MB<br>volume)                                 | Second SODIMM<br>MEMC2CS0,MEMC2CS1<br>40-bit | WV3HG32M40SEU-PD4                                                                                                                       | 128MB              | 32+8<br>ECC             |

| 3   | 10000000 - 7FFFFFF                                                                     | Empty Space                                  | -                                                                                                                                       | 3GB                | -                       |

| 4   | 80000000 - 9FFFFFF                                                                     | PCI1                                         | Inbound/Outbound window                                                                                                                 | 512MB              | 32                      |

| 5   | A0000000 - DFFFFFF                                                                     | Empty Space                                  | -                                                                                                                                       | 1GB                | -                       |

Freescale Semiconductor 3-1

Table 3-1. MPC8360EA MDS Processor Board Memory Map (continued)

| No. | Address Range                                      | Target                                   | Device Name                                                                                       | Volume<br>in Bytes    | Port<br>Size<br>in Bits |

|-----|----------------------------------------------------|------------------------------------------|---------------------------------------------------------------------------------------------------|-----------------------|-------------------------|

| 6   | E0000000 - E01FFFF                                 | 8360                                     | Internal Memory Register Space                                                                    | 2MB                   | 32                      |

| 7   | E0200000 - EFFFFFF                                 | Empty Space                              | -                                                                                                 | ~256MB                | -                       |

| 8   | F0000000 - F3FFFFFF<br>or<br>(F0000000 - F7FFFFFF) | Local Bus SDRAM:<br>(optional)<br>on CS2 | MT48LC16M16A2TG-6A x 1<br>(with MT48LC32M16A2TG-7E<br>for parity)<br>or<br>MT48LC16M16A2TG-6A x 2 | 64MB<br>or<br>(128MB) | 32+8<br>parity          |

| 9   | F4000000 - F7FFFFF                                 | Empty Space                              | in case SDRAM is only 64MB                                                                        | 64MB                  | -                       |

| 10  | F8000000 - F8007FFF                                | BCSR on CS1                              | Xilinx FPGA                                                                                       | 32KB                  | 8                       |

| 11  | F8008000 - F800FFFF                                | PIB CS4                                  | (see PIB documentation)                                                                           | 32KB                  |                         |

| 12  | F8010000 - F8017FFF                                | PIB CS5                                  | (see PIB documentation)                                                                           | 32KB                  |                         |

| 13  | F8018000 - F801FFFF                                | PIB CS3                                  | (see PIB documentation)                                                                           | 32KB                  |                         |

| 14  | F8020000 - FDFFFFF                                 | Empty Space                              |                                                                                                   | ~100MB                | -                       |

| 15  | FE000000 - FEFFFFF                                 | FLASH on CS0                             | S29GL256M                                                                                         | 16MB                  | 16                      |

| 16  | FE800000 - FFFFFFF                                 | Empty Space                              | -                                                                                                 | 24MB                  | -                       |

# 3.2 Configuration Registers Mapping

The table below shows how to initialize the registers in the MPC8360EA. It shows the register name, its address, and what value must be written to that register for proper initialization. There are several instances that require repeat actions (such as writing FF to LSDMR several times). These must be carried out as described.

Table 3-2. MPC8360EA MDS Processor Board Configuration Registers

| Register Name            | Register<br>Address | Register<br>Value | Description |

|--------------------------|---------------------|-------------------|-------------|

| IMMRBAR                  | 0xff400000          | 0xE0000000        |             |

| Local A                  | ccess Window FLASI  |                   |             |

| LBLAWBAR0                | 0xE0000020          | 0xFE000000        |             |

| LBLAWBAR0                | 0xE0000024          | 0x80000017        | 16M         |

| Local Access Window BCSR |                     |                   |             |

| LBLAWBAR1                | 0xE0000028          | 0xF8000000        |             |

| LBLAWBAR1                | 0xE000002C          | 0x8000000E        | 32K         |

| Local Ac                 | cess Window SDRA    |                   |             |

MPC8360EA MDS Processor Board, Rev. 0.1

3-2 Freescale Semiconductor

Table 3-2. MPC8360EA MDS Processor Board Configuration Registers (continued)

| Register Name | Register<br>Address | Register<br>Value | Description                  |

|---------------|---------------------|-------------------|------------------------------|

| LBLAWBAR2     | 0xE0000030          | 0xF0000000        |                              |

| LBLAWBAR2     | 0xE0000034          | 0x80000019        | 64M                          |

| LBLAWBAR2     | 0xE0000034          | 0x8000001A        | 128M                         |

| Local         | Access Window PIB   |                   |                              |

| LBLAWBAR3     | 0xE0000038          | 0xF8008000        |                              |

| LBLAWBAR3     | 0xE000003c          | 0x8000000F        | 64K                          |

|               | PIB (CS4)           |                   |                              |

| OR4           | 0xE0005024          | 0xFFFFE9F7        | 32K                          |

| BR4           | 0xE0005020          | 0xF8008801        | Port-size=8bit, MSEL=GPCM    |

|               | PIB (CS5)           |                   |                              |

| OR5           | 0xE000502C          | 0xFFFFE9F7        | 32K                          |

| BR5           | 0xE0005028          | 0xF8010801        | Port-size=8bit, MSEL=GPCM    |

| Local         | Access Window PCI   |                   |                              |

| PCILAWBAR0    | 0xE0000060          | 0x80000000        |                              |

| PCILAWBAR0    | 0xE0000064          | 0x8000001C        | 512M                         |

| QE Secon      | dary Bus Access Win |                   |                              |

| LBMCSAR       | 0xE0001800          | 0x000F0000        |                              |

| LBMCEAR       | 0xE0001840          | 0x000F3FFF        |                              |

| LBMCAR        | 0xE0001880          | 0x00000001        |                              |

|               | LBIU registers      |                   |                              |

| LCRR          | 0xE00050D4          | 0x00000004        |                              |

|               | Flash (CS0)         |                   |                              |

| BR0           | 0xE0005000          | 0xFE001001        | Port-size=16bit, MSEL=GPCM   |

| OR0           | 0xE0005004          | 0xFF006FF7        | 16M                          |

| BCSR (CS1)    |                     |                   |                              |

| BR1           | 0xE0005008          | 0xF8000801        | Port-size=8bit, MSEL=GPCM    |

| OR1           | 0xE000500C          | 0xFFFFE9F7        | 32K                          |

|               | SDRAM (CS2)         |                   |                              |

| OR2           | 0xE0005014          | 0xFC006901        | 64M                          |

| BR2           | 0xE0005010          | 0xF0001861        | Port-size=32-bit, MSEL=SDRAM |

|               |                     |                   |                              |

Freescale Semiconductor 3-3

Table 3-2. MPC8360EA MDS Processor Board Configuration Registers (continued)

| Register Name | Register<br>Address | Register<br>Value | Description                                                                                                                                          |

|---------------|---------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| LSRT          | 0xE00050A4          | 0x3F000000        | LSRT - SDRAM refresh, timer period.                                                                                                                  |

| MRTPR         | 0xE0005084          | 0x20000000        |                                                                                                                                                      |

| LSDMR         | 0xE0005094          | 0x0063B723        |                                                                                                                                                      |

|               | SDRAM               |                   |                                                                                                                                                      |

| LSDMR         | 0xE0005094          | 0x2863B723        |                                                                                                                                                      |

|               | 0xF0000000          | 0x000000FF        |                                                                                                                                                      |

| LSDMR         | 0xE0005094          | 0x0863B723        |                                                                                                                                                      |

|               | 0xF0000000          | 0x000000FF        |                                                                                                                                                      |

| LSDMR         | 0xE0005094          | 0x1863B723        |                                                                                                                                                      |

|               | 0xF00000cc          | 0x000000FF        |                                                                                                                                                      |

| LSDMR         | 0xE0005094          | 0x4063B723        |                                                                                                                                                      |

| #LSRT         | 0xE00050A4          | 0x20000000        | LSRT - SDRAM refresh, timer period                                                                                                                   |

| MRTPR         | 0xE0005084          | 0x20000000        | MRTPR - Refresh timers prescaler - <period clk="" input="" of="" refresh="" the="" timers=""> = <sys_clk> / <ptp=0x20></ptp=0x20></sys_clk></period> |

Table 3-3. Init DDR values for DDR 72-bit

| Register Name                                         | Register<br>Address | Register<br>Value | Description            |

|-------------------------------------------------------|---------------------|-------------------|------------------------|

| DDRLAWBAR0                                            | 0xE00000A0          | 0x00000000        |                        |

| DDRLAWAR0                                             | 0xE00000A4          | 0x8000001B        | 256M                   |

| First DDR Controller Registers SODIMM initializations |                     |                   |                        |

| CLK_CNTL                                              | 0xE0002130          | 0x82000000        | SS_EN=1; CLK_ADJST = 2 |

| #CS0_BNDS                                             | 0xE0002000          | 0x0000007         | first 128MB            |

| #CS0_CONFIG                                           | 0xE0002080          | 0x80000101        |                        |

#### MPC8360EA MDS Processor Board, Rev. 0.1

3-4 Freescale Semiconductor

### Table 3-3. Init DDR values for DDR 72-bit (continued)

| #CS1_BNDS               | 0xE0002008 | 0x0008000f | last 128MB                             |

|-------------------------|------------|------------|----------------------------------------|

| #CS1_CONFIG             | 0xE0002084 | 0x80000101 |                                        |

| #TIMING_CFG_1           | 0xE0002108 | 0x37343321 |                                        |

| #TIMING_CFG_2           | 0xE000210C | 0x00000800 |                                        |

| #DDR_SDRAM_CFG          | 0xE0002110 | 0x42008000 | 32_BE=0 => 64-bit bus is used, 2T_EN=1 |

| #DDR_SDRAM_MODE         | 0xE0002118 | 0x20000162 |                                        |

| #DDR_SDRAM_INTERV<br>AL | 0xE0002124 | 0x045B0100 |                                        |

| delay before enable     |            |            |                                        |

| DDR_SDRAM_CFG           | 0xE0002110 | 0xC2008000 |                                        |

#### Table 3-4. Init DDR values for 2 x 36-bit

| Register Name                                         | Register<br>Address | Register<br>Value | Description                            |

|-------------------------------------------------------|---------------------|-------------------|----------------------------------------|

| Local Access                                          | Window DDR SDRA     | AM                |                                        |

| DDRLAWBAR0                                            | 0xE00000A0          | 0x00000000        |                                        |

| DDRLAWAR0                                             | 0xE00000A4          | 0x8000001A        | first 128M                             |

| Local Access Wind                                     | ow Secondary DDR    | SDRAM             |                                        |

| SDDRLAWBAR0                                           | 0xE00000E0          | 0x0800000         |                                        |

| SDDRLAWAR0                                            | 0xE00000E4          | 0x8000001A        | first 128M                             |

| QE Secondary Bus Access Windows                       |                     |                   |                                        |

| SDMCSAR                                               | 0xE0001804          | 0x00008000        |                                        |

| SDMCEAR                                               | 0xE0001844          | 0x0000FFFF        |                                        |

| SDMCAR                                                | 0xE0001884          | 0x00000001        |                                        |

| First DDR Controller Registers SODIMM initializations |                     |                   | SWISSBIT Half SODIMM                   |

| CLK_CNTL                                              | 0xE0002130          | 0x82000000        | SS_EN=1; CLK_ADJST = 2                 |

| CS0_BNDS                                              | 0xE0002000          | 0x00000007        | first 128MB                            |

| CS0_CONFIG                                            | 0xE0002080          | 0x80000102        | 13 row bits, 10 columns bits           |

| TIMING_CFG_1                                          | 0xE0002108          | 0x37343321        |                                        |

| TIMING_CFG_2                                          | 0xE000210C          | 0x00000800        |                                        |

| DDR_SDRAM_CFG                                         | 0xE0002110          | 0x42008000        | 32_BE=0 => 64-bit bus is used, 2T_EN=1 |

Freescale Semiconductor 3-5

#### Table 3-4. Init DDR values for 2 x 36-bit (continued)

| DDR_SDRAM_MODE                  | 0xE0002118 | 0x20000163 |  |

|---------------------------------|------------|------------|--|

| DDR_SDRAM_INTERVA<br>L          | 0xE0002124 | 0x045B0100 |  |

| delay before enable             |            |            |  |

| DDR_SDRAM_CFG                   | 0xE000D130 | 0xC2008000 |  |

| Second DDR Controller Registers |            |            |  |

#### **CAUTION**

CAUTION!!!!SDDRIOE (SECONDARY DDR IO ENABLE) MUST BE SET TO 1 !!!

# USE A CONFIGURATION WORD WHICH INCLUDES SDDRIOE=1 OR

SET SDDRIOE=1 THROUGH BCSR7[3] (AND CNFLOCK(BCSR13[3]) AND PORESET(BCSR11[4]))

|                         |            |            | <del>,</del>                |

|-------------------------|------------|------------|-----------------------------|

| CLK_CNTL                | 0xE000D130 | 0x82000000 |                             |

| CS0_BNDS                | 0xE000D000 | 0x0008000B | first 64MB                  |

| CS0_CONFIG              | 0xE000D080 | 0x80000101 | 13 row bits, 9 columns bits |

| CS1_BNDS                | 0xE000D008 | 0x000C000F | last 64MB                   |

| CS1_CONFIG              | 0xE000D084 | 0x80000101 | 13 row bits, 9 columns bits |

| #TIMING_CFG_1           | 0xE000D108 | 0x37343321 |                             |

| #TIMING_CFG_2           | 0xE000D10C | 0x00000800 |                             |

| #DDR_SDRAM_CFG          | 0xE000D110 | 0x420C8000 |                             |

| #DDR_SDRAM_MODE         | 0xE000D118 | 0x20000163 |                             |

| #DDR_SDRAM_INTERV<br>AL | 0xE000D124 | 0x045B0100 |                             |

| delay before enable     |            |            |                             |

| DDR_SDRAM_CFG           | 0xE000D110 | 0xC20C8000 |                             |

3-6 Freescale Semiconductor

# **Chapter 4 Controls and Indicators**

This chapter describes controls and indicators of the MPC8360EA MDS Processor Board, which includes switches, jumpers, LEDs, and push buttons.

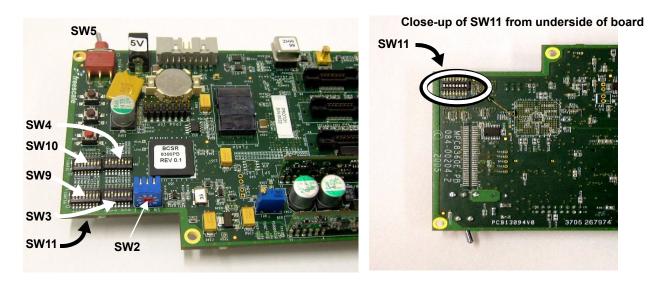

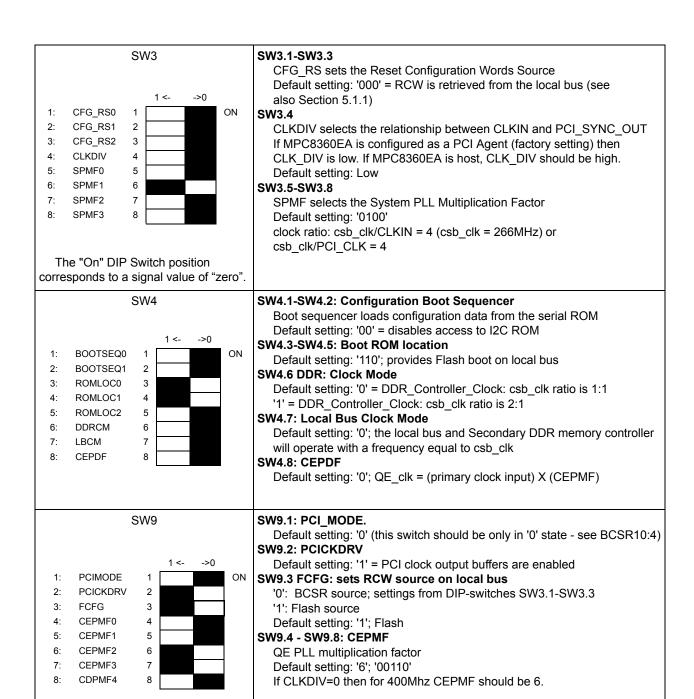

### 4.1 Switches

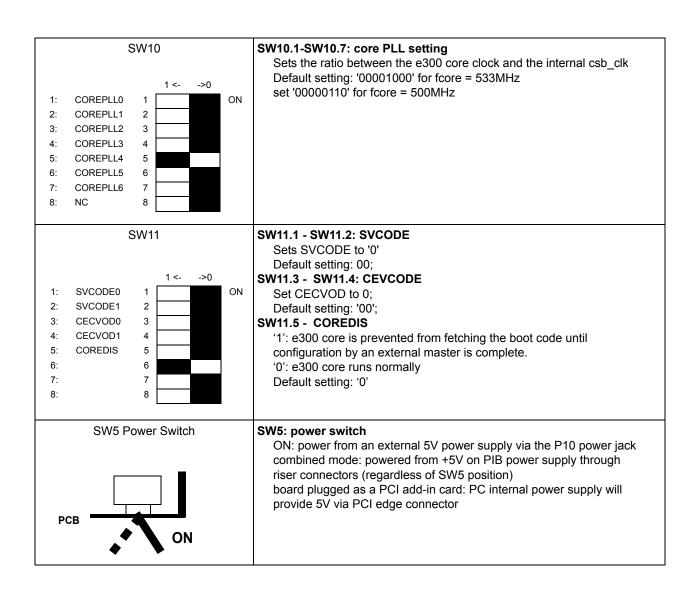

Figure 4-1 below shows the locations of the DIP Switches. Note that when "ON", the value of the switch is zero.

Figure 4-1. MPC8360EA MDS Processor Board Switches Locations

Descriptions of settings for the DIP switches are described below. For more detailed descriptions of the bits and fields, see the MPC8360 User Manual:

Freescale Semiconductor 4-3

# 4.2 Jumpers

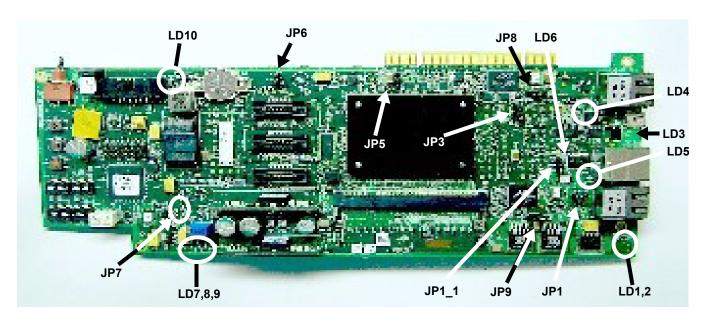

Figure 4-2 below shows the locations of the jumpers and LEDs.

Figure 4-2. MPC8360EA MDS Processor Board Jumpers and LEDs Locations

MPC8360EA MDS Processor Board jumpers settings are described in Table 4-1, below.

**Table 4-1. Jumper Settings**

| JP1:<br>3.3V/2.5V                          | GETH Voltage For 2.5V connect 1-2 For 3V JP1 connect 3-2                                    |

|--------------------------------------------|---------------------------------------------------------------------------------------------|

| JP1_1:<br>ATM/USB                          | JP1_1 Select between ATM function of USB function. For USB, connect 1-2 For ATM connect 3-2 |

| JP3: TDMATXCLK/M2GTX125                    | For GMII2, connect 1-2 (M2GTX125 for GTETH2). For TDMA when using PIB, connect 3-2.         |

| JP5:<br>LVDD2 3.3V/2.5V                    | 8360 LVDD2 Power For LVDD2 3.3V connect 2-3. For LVDD2 2.5V connect 1-2.                    |

| JP6:<br>Clock source PIB(onboard)/External | JP6 Clock<br>Connected 1-2 to configure for an external clock.                              |

| JP7:<br>Reset.                             | JP7 reset not connected.                                                                    |

| JP8, JP9:                                  | JP8, JP9: not in use                                                                        |

4-4 Freescale Semiconductor

## 4.3 LEDs

The MPC8360EA MDS Processor Board has the following LEDs (locations shown in Figure 4-2 above):

## LD1, LD2 - Signaling LEDs

LED's, LD1 (green) and LD2 (red), are program controlled. They are used for extra visibility on the running utility. They are lit up by setting bits BCSR0.5-6 respectively.

#### LD3 - USB Power

When lit (green), the USB Vbus is powered.

#### LD4, LD5 - GETH Enable

The green LED, LD4,5, indicates enable for GETH Transceivers U6,U5, respectively.

## **LD6 - DUART Enable**

A green LED, LD6, indicates enable for the RS232 Dual Transceiver.

### **LD7 - Power GOOD**

A green LED, LD7, indicates that the MPC8360EA MDS Processor Board power is operating normally.

#### LD8 - Not in Use

#### LD9 - BOOT Indicator

The LD9 indicates MPC8360 boot processing.

#### **LD10 - 5V Power Indicator**

The green LED, LD10, indicates a 5V power level on the MPC8360EA MDS Processor Board.

A 5V power supply is plugged into the P10 Power Connector on the board's front side for the Stand-Alone Mode. The MPC8360EA MDS Processor Board is powered by the 5V external power supply when the SW5 Power Switch is turned to the "ON" (up) position.

When the MPC8360EA MDS Processor Board is plugged into an PC via the PCI edge connector it is powered from the edge connector's 5V power rail (Agent Mode). In the PIB Combined Mode, 5V power is supplied from the PIB's power supply via risers connectors. Note that if working in either of these two modes, the position of SW1 is ignored.

# 4.4 Other Controls and Indicators

# 4.4.1 Push Buttons

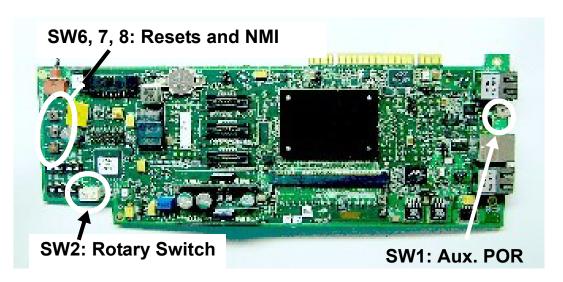

Table 4-2 below describes the functionality of the board's push buttons. See Figure 4-3 for the locations of these push buttons.

Table 4-2. The MPC8360EA MDS Processor Board Push Buttons

| SW1<br>Power-on-Reset  | PRESET | Pressing button SW1 results in Power-On-Reset for all components on the MPC8360EA MDS Processor Board.  Use this reset button when the MPC8360EA MDS Processor Board is installed in a PC.                 |

|------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SW2<br>Software Option | SW OPT | Rotary Switch SW2 allows the user to change the program flow according to eight available cases.  Not available when installed in a PC.                                                                    |

| SW6<br>Hard Reset      | HRESET | Pressing button SW6 results in a Hard Reset for the MPC8360EA.  Not available when installed in a PC.                                                                                                      |

| SW7<br>Soft Reset      | SRESET | Pressing button SW7 results in a Soft Reset for the MPC8360EA. Despite the reset, clock and chip-select data as well as SDRAM (if installed) contents are retained.  Not available when installed in a PC. |

| SW8<br>NMI (Abort)     | NMI    | Pressing button SW8 results in aborting program execution by issuing a level 0 interrupt to the MPC8360EA. The ABORT switch signal is de-bounced.                                                          |

4-6 Freescale Semiconductor

Figure 4-3. MPC8360EA MDS Processor Board Push Buttons and Auxiliary POR

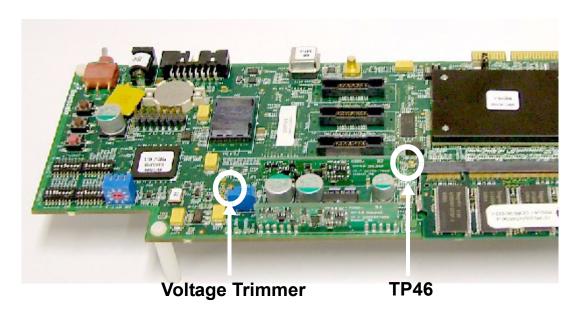

## 4.4.2 Test Points

TP46, shown below in Figure 4-4, is used in conjunction with the voltage trimmer for adjusting the core frequency. To change the core frequency to 500MHz, use the screw on the voltage trimmer to adjust the Vdd voltage to 1.3 V. Measure this voltage using Test Point 46, as shown. To return the core frequency to 533MHz, return this voltage to 1.2V.

Figure 4-4. Voltage Trimmer and Test Point

4-8 Freescale Semiconductor

# **Chapter 5 Functional Description**

In this chapter the design details of various modules of the MPC8360EA MDS Processor Board are described. This includes memory map details and software initialization of the board.

# 5.1 Reset & Reset - Configuration

## 5.1.1 Reset Clocking and Configuration Initialization

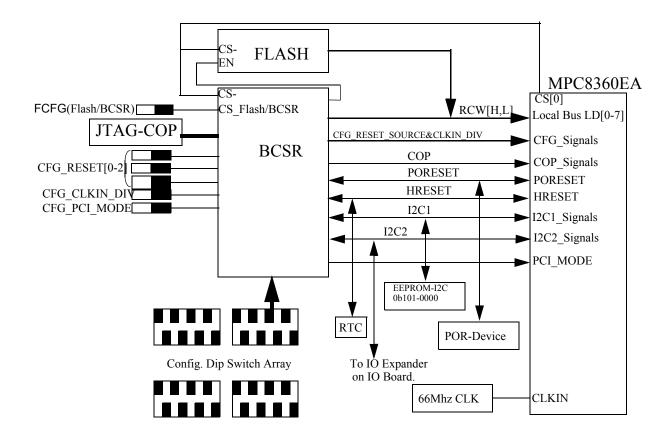

The MPC8360EA samples four configuration pins at Power-on-Reset negation. Three of these pins (CFG\_RESET[0-2]) allow setting up to eight variant reset configuration sources such as I2C EEPROM, parallel EPROM (Flash) or various hard coded options (see the *MPC8360 User Manual* for more details). See Table 5-1 for a list of the options. The fourth pin, CFG\_CLKIN\_DIV, determines whether or not CLKIN is divided by 2. Figure 5-1 below shows a schematic diagram of the reset circuit, including the various signals and their sources.

**Table 5-1. Reset Configuration Words Source**

| Reset Configuration Signal Name | Value<br>(Binary)<br>SW3(1-3) | Meaning                                                                                                                      |

|---------------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| CFG_RESET[0-2]                  | 000                           | Reset configuration word is loaded from a local bus EEPROM, or the BCSR (and DIP switches), depending on the value of SW9[3] |

|                                 | 001                           | Reset configuration word is loaded from an I <sup>2</sup> C EEPROM, PCI_CLK/PCI_SYNC_IN is in the range of 25-44 Mhz.        |

|                                 | 010                           | Reset configuration word is loaded from an I <sup>2</sup> C EEPROM, PCI_CLK/PCI_SYNC_IN is in the range of 44-66.666 Mhz.    |

|                                 | 011                           | Hard coded option #0. Reset configuration word is not loaded.                                                                |

|                                 | 100                           | Hard coded option #1. Reset configuration word is not loaded.                                                                |

|                                 | 101                           | Hard coded option #2. Reset configuration word is not loaded.                                                                |

|                                 | 110                           | Hard coded option #3. Reset configuration word is not loaded.                                                                |

|                                 | 111                           | Hard coded option #4. Reset configuration word is not loaded.                                                                |

Figure 5-1. Reset Circuit Block Diagram

Once the PORESET signal is negated, the MPC8360EA starts to load the reset configuration word (RCW) bits. These bits are latched from the DIP-switches into appropriate FPGA registers (the BCSR's).

Excluding the hard-coded options, there are three ways to drive the RCW:

- Via BCSR: CFG RESET SOURCE[0-2] = 000, & FCFG = 0 (SW9[3])

- Via FLASH: CFG\_RESET\_SOURCE[0-2] = 000 & FCFG = 1 (SW9[3])

- Via I2C 1 bus: CFG\_RESET\_SOURCE[0-2] is 001 or 010, depending on the value desired for PCI\_CLK. The setting for FCFG has no effect in this case.

All the RCW bits can be changed from their initial settings using either the FPGA BCSR through the local bus or using the LLD (low level debugger). The BCSR must then drive HRESET/ PORESET to load a new configuration word to the device. It is possible to read the value of the RCW from the BCSRs.

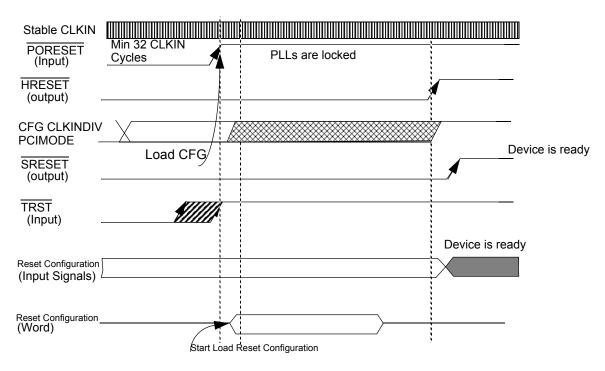

Figure 5-2 below shows the timing for the reset sequence.

Figure 5-2. Reset Timing Diagram

## 5.1.2 Reset Circuit

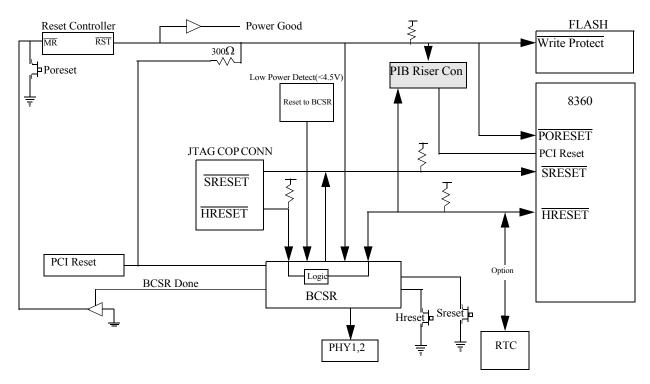

The Reset Circuit of the MPC8360EA MDS Processor Board has the following features:

- Reset controller (MIC2774N-23BM5 from MICREL) drives the PORESET signal.

- Low power detect device drives PORESET as follows:

- if the detected input power is less than 4.5V, PORESET is driven at 5V

- if the detected input power is less than 3V, PORESET is driven at 3.3V

- if the detected input power is less than 2V, PORESET is driven at 2.2V

- if the detected input power is less than 1.6V, PORESET is driven at 1.8V

- JTAG COP can drive HRESET or SRESET, depending on the command given from the JTAG device.

- Push button for PORESET, HRESET and SRESET.

- FLASH memory is protected during PORESET and after that until the system is enabled

- PCI RST signal is connected to PORESET signal.

- The BCSR resets the GETH PHYs.

# 5.1.3 MPC8360EA MDS Processor Board Reset Principles

*Upon power on:* The device MIC2774N-23BM5 drives PORESET low for 300msec to the

MPC8360EA, BCSR, FLASH and PIB (if connected).

The BCSR performs initialization procedures, and drives the  $\overline{\text{BCSR Done}}$  signal to logical 1, in order to keep PORESET low. After finishing initialization the  $\overline{\text{BCSR Done}}$  signal is logical 0.

The BCSR drives a RESET signal to the GETH - PHYs.

In Agent mode:

When the MPC8360EA MDS Processor Board is in Agent Mode, PORESET can be driven by PCI RST signal.

The PCI edge connector PIN RST is connected to the PORESET in order to reset the MPC8360EA MDS Processor Board.

There are several reset sources on the MPC8360EA MDS Processor Board:

- Power On Reset

- Manual Hard Reset

- Manual Soft Reset

- MPC8360 device

HRESET & SRESET can be driven through JTAG COP connector, by BCSR, by RTC when it reaches its count value, or by push buttons.

Figure 5-3. Reset Block Scheme

#### 5.1.4 Power - On Reset

The power on reset to the MPC8360EA MDS Processor Board initializes the processor's state after power up. A dedicated logic unit asserts PORESET input for a period long enough to cover the MPC8360EA core

MPC8360EA MDS Processor Board, Rev. 0.1

voltage stabilization. A Power-On-Reset may be generated manually as well by an on-board dedicated push-button (SW1).

In addition, a power on reset for the MPC8360EA can be done by toggling bit #4 in BCSR11.

### 5.1.5 Hard Reset

Hard Reset may be generated on the MPC8360EA MDS Processor Board by any one of the following sources:

- COP/JTAG Port (in Stand-Alone Mode only)

- Manual Hard Reset.

- Board Internal sources.

Hard Reset, when generated, causes the MPC8360EA to reset all its internal hardware except for PLL logic and re-acquires the Hard Reset configuration from its current source. Since Hard Reset also resets the refresh logic for dynamic RAMs, their content is lost as well.

#### CAUTION

HRESET is an open-drain signal and must be driven with an open-drain gate by whatever external source is driving it. Otherwise, contention will occur over that line, and that might cause permanent damage to either board logic and/or to the MPC8360EA.

## 5.1.6 COP/JTAG Port Hard - Reset (stand-alone only)

To provide convenient Hard Reset capability for a COP/JTAG controller, an HRESET line has been connected to the COP/JTAG port connector. The COP/JTAG controller may directly generate a Hard Reset by asserting (low) this line. The HRST signal from the COP/JTAG is then driven to the FPGA and from the FPGA to the MPC8360EA. This technique is used in order to cooperate with the low level debugger, although it can operate properly without connecting it to the FPGA.

## 5.1.7 Manual Hard Reset

To allow a run-time Hard Reset, a manual Hard Reset is facilitated, via SW6. Note that this cannot be done when the MPC8360EA MDS Processor Board is connected in a PC (Agent Mode), but instead SW1 (PORESET) can be used.

In addition, a manual Hreset for the MPC8360EA can be done by toggling bit #4 in the CCR (Address F800000F) register in the FPGA.

## 5.1.8 Manual Soft Reset

To allow a run-time Soft Reset, manual Soft Reset is facilitated, via SW8. Note that this cannot be done when the MPC8360EA MDS Processor Board is connected in a PC (Agent Mode).

In addition, a manual Sreset for the MPC8360EA can be done by toggling bit #5 in the CCR (Address F800000F) register.

MPC8360EA MDS Processor Board, Rev. 0.1

# 5.2 Default Settings

The default settings for the MPC8360EA MDS Processor Board are as follows:

- Clock in (primary clock) = 66Mhz

- Core freq = 533Mhz

- CCB = 266Mhz

- DDR = 400Mhz

- QE = 400Mhz [QE Clock = (Primary clock) x (CEPMF)], CEPMF set by SW9[4-8]

- Local Bus 66Mhz LBIU.LCRR = 0x4

- Primary DDR = DDR2

- CFG RS[0-2], BootSeq, RomLoc = Read configuration word from Local Bus (BCSR)

- PCI MODE = Enable PCI Clock drive

# 5.3 Clocking

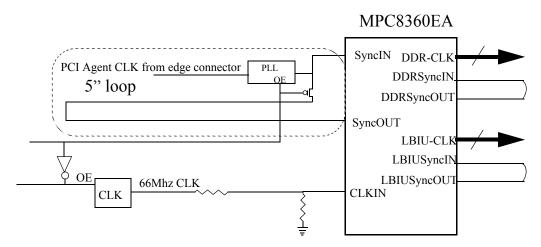

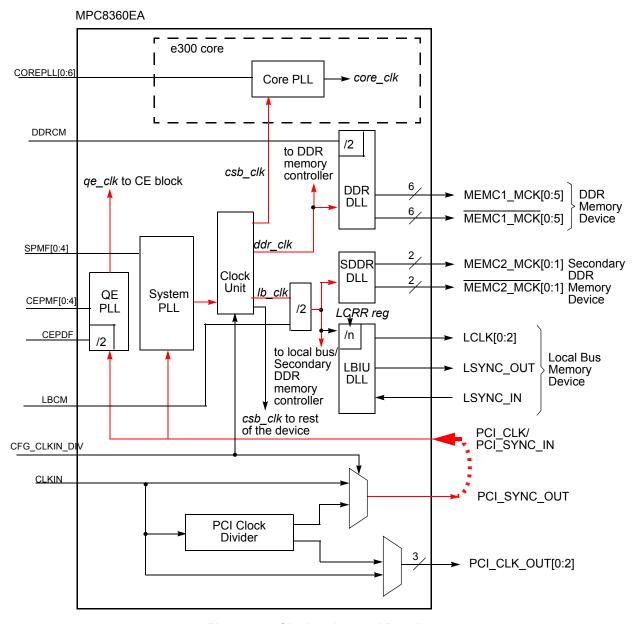

A block diagram showing internal details for the clocks of the MPC8360EA MDS Processor Board is shown below in Figure 5-5. As can be seen from the diagram, all input signals (those that are on the left of the block), except CFG\_CLKIN\_DIV and CLKIN are from the configuration word, and should be set according to information in the MPC8360EA Reference Manual.

A diagram showing certain electrical aspects of the clocking connections is shown below in Figure 5-4.

There are two modes of clock operations:

- Agent

- Host

In **Agent mode**, the MPC8360EA MDS Processor Board is inserted in a PC or in an adaptor on the PIB. Its edge connector (P3), which is inserted in the PC's or PIB's PCI slot, causes an open circuit between PCI\_SYNC\_OUT and PCI\_SYNC\_IN. The PC or the host processor on the PIB therefore supplies the input clock signal via the PCI\_SYNC\_IN pin. In this case, the CLKIN pin is connected to GND.

In **Host mode**, the edge connector (P3) is not connected. As a result, CLKIN is not connected to ground, and supplies a clock signal to PCI\_SYNC\_OUT via a 5" loop trace (which covers the PCI clock routing on the PIB), which in turn is connected to PCI\_SYNC\_IN, thus supplying a clock to the MPC8360E device.

Figure 5-4. Clocks - Showing External Connection Scheme, and 5" Loop

Figure 5-5. Clocks - Internal Details

5-8 Freescale Semiconductor

#### **Working with ATM signals:**

It is important to note that if working with ATM/UPC2 signals, the MPC8360EA must receive a 66MHz signal on the PCI\_SYNC\_IN pin. Since this is the frequency of the CLKIN signal, this is not a problem in Host mode. However, in Agent mode, when the clock signal comes from an outside source, and the CLKIN is connected to GND, the user must ensure that the ATM nevertheless uses this 66MHz signal. Do this as follows:

First, write to the following, **before** you set the PCIMODE bit (BCSR10[4]) bit to '1':

0X'EFE35010' to offset 0x'XX00148C' and then 0X'FFE3A030' to offset 0x'XX00148C'

# 5.4 FPGA - Board Control & Status Registers (BCSR)

The FPGA contains the BCSR, which is an 8-bit wide read / write register file that controls or monitors most of the MPC8360EA MDS Processor Board hardware options. The BCSR's register may be accessed from the Local Bus. The BCSR includes up to 16 registers, some of which are optional.

BCSR registers are duplicated numerous times within a CS1 region. This is due to the CS region's 32KB minimum block size and the fact that only address lines A[27-31] are decoded for register selection by the BCSR. BCSR is implemented on a Xilinx FPGA device that provides register and logic functions over some MPC8360EA MDS Processor Board signals.

The BCSR controls or monitors the following functions:

- Power-on-Reset & Hardware configuration setting for the processor.

- Hardware Reset Configuration bits are stored in BCSR registers available from the Local Bus.

- Hard- Soft- Reset and NMI (IRQ) push buttons debounce function.

- Hardware Configuration for both GETH transceivers.

- Enable/Disable to:

- Two GETH1,2 Transceivers.

- Dual RS232 Transceiver.

- LED off.

- Provides hardware write protection for FLASH and BRD I2C EEPROM.

- Two LEDs (one green, one red), which provide software signaling.

- Special CCR COP register for JTAG port connectivity.

- Status registers include:

- PCI Host Mode indicates if the Board is working in a Host Mode (Stand-Alone or PIB Combined) or the Agent Mode BCSR4[0]

- Processor Low Power Mode (QUISCE) BCSR11[0]

- BCSR Revision code BCSR12[0-3] REV BCSR12[4-7] SUBREV.

Sections of the BCSR slice control registers generally have **low** active notations. This means that a bit function is realized while the bit is zero. When a bit is set to **high** a related function is disabled. The default setting is assumed to be non-functional. The most significant bit is bit 0.

The BCSR (No.'s 0...7) registers reflect the values in the RCW High and Low registers of the MPC8360EA chip. The correspondence is indicated in the "CWL" or "CWH" column.

## 5.4.1 BCSR0 - Status Register

BCSR0 serves as a 8-bit control register on the board. BCSR0 may be read or written at any time. BCSR0 defaults are attributed immediately after a Power-On Reset or HRESET. BCSR0 fields are described below in Table 5-2

| CWL | ВІТ | MNEMONIC   | Function                                                                                                                                                                                                                                                                                                                       | DEF on PORESET                         |

|-----|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 0   | 0   | LBCCM      | Local Bus/Secondary DDR Controller. Selects local bus and secondary DDR memory controllers clock ratio. The bit is set by default by appropriate DIP switch. May be rewritten via LBIU.                                                                                                                                        | SW4[7] Sampled at<br>HRESET            |

| 1   | 1   | DDRCM      | DDR SDRAM Clock Mode. If this bit set high, the DDR SDRAM memory controller will operate with frequency equal to twice the frequency of the csb_clk. If this bit is low, the DDR SDRAM memory controller will operate at the csb_clk frequency. A DIP-switch may change DDRCM bit setting. May be rewritten any time via LBIU. | SW4[6]<br>Sampled at<br>HRESET         |

| 2-3 | 2-3 | SVCOD[0-1] | VCO Division. The two bits reflect SVCOD[2-3] signals logic level during Hard Reset Configuration sequence. The bits are set low by default. May be rewritten via LBIU.                                                                                                                                                        | SW11[1-2]<br>Sampled at<br>HRESET      |

| 4-7 | 4-7 | SPMF       | System PLL Multiplication Factor. The four bits reflect SPMF[0-3] signals logic level during Hard Reset Configuration sequence. The bits are set by default by appropriate DIP switch. May be rewritten via LBIU.                                                                                                              | SW3[5-8]<br>Sampled at<br>PORESET neg. |

Table 5-2. BCSR0 Register Description

# 5.4.2 BCSR1 - Status Register

On the board, BCSR1 acts as a control register. BCSR1, which may be read or written at any time, receives its defaults immediately after Power-On or PORESET. BCSR1 fields are described below in Table 5-3:

DEF on CWL BIT **MNEMONIC Function PORESET** 0 Reserved Reserved 8 9-15 1-7 **COREPLL** Core PLL Multiplication Factor. The seven bits reflect COREPLL[0-6] SW10[1-7] signals logic level during Hard Reset Configuration sequence. The bits Sampled at are set by appropriate DIP switch (default). May be rewritten via LBIU. **HRESET**

Table 5-3. BCSR1 Register Description

MPC8360EA MDS Processor Board, Rev. 0.1

5-10 Freescale Semiconductor

## 5.4.3 BCSR2 - Status Register

This register is reserved.

## 5.4.4 BCSR3 - Status Register

On the board, BCSR3 acts as a control register. BCSR3, which may be read or written at any time, receives its defaults immediately after the PORESET signal. BCSR3 fields are described below in Table 5-4:

DEF on **CWL** BIT **MNEMONIC Function** ATT. **PORESET** SW11[3-4] 24-25 0-1 CEVCOD[0-1] CE PLL VCO. The two bits reflect CEVCOD[0-1] signals logic R,W level during Hard Reset Configuration sequence. The bits are Sampled at set low by default. May be rewritten via LBIU. HRESET 2 26 CEPDF CE PLL Division Factor. This bits reflect CEPDF signal logic SW4[8] R.W level during Reset Configuration sequence. The bits are set by Sampled at appropriate DIP switch. May be rewritten via LBIU. **HRESET** CE PLL Multiplication Factor. The five bits reflect CEPMF 27-31 3-7 **CEPMF** SW9[4-8] R,W signals logic level during Reset Configuration sequence. The Sampled at bits are set by appropriate DIP switch. May be rewritten via **HRESET** LBIU.

Table 5-4. BCSR3 Register Description

# 5.4.5 BCSR4 - Status Register

On the board, BCSR4 acts as a control register. BCSR4, which may be read or written at any time, receives its defaults immediately after PORESET signal. BCSR4 fields are described below in Table 5-5:

| CWH | BIT | MNEMONIC | Function                                                                                                                                                                                                                                                                                                                                                 | DEF on PORESET                                                                         |