Rev. 0 — 01/2020 Application Note

**Contents**

1 Introduction..... 1

2 Board overview......1

3 Components of K32L2B Headset...... 4

4 Conclusion...... 8

### 1 Introduction

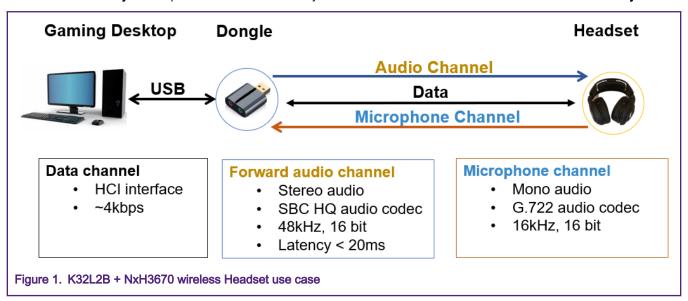

This document provides the necessary information of K32L2B Headset in the **Bluetooth LE Audio System** as below.

The system contains a K32L2B\_Dongle and a K32L2B\_Headset.

- **K32L2B\_Dongle**: The Dongle has a USB interface connected to the PC. It is responsible for creating a wireless audio link with one extra Headset.

- K32L2B\_Headset: The Headset has a speaker, a microphone, and some User Interface (UI) components, such as, buttons, sliders, rotary switches and LED.

This document mainly described the hardware design and software architecture (top-level design) of K32L2B Headset in the **Bluetooth LE Audio System**. It provides audience with a systematic view of K32L2B Headset in the **Bluetooth Audio System**.

### 2 Board overview

# 2.1 Block diagram

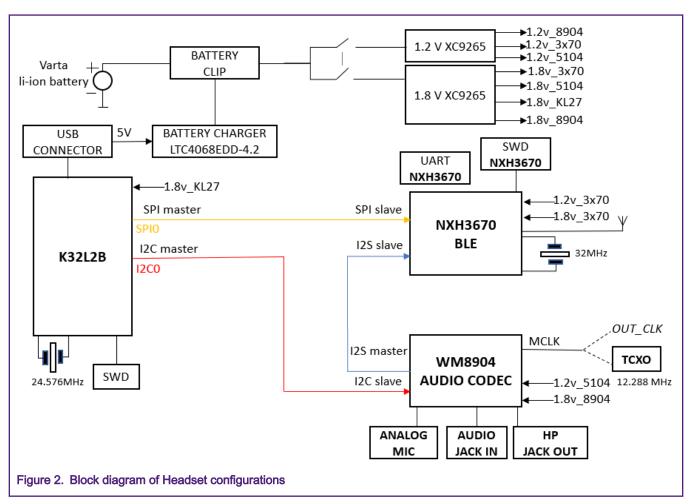

Figure 2 shows the block diagram of K32L2B\_Headset.

As shown in Figure 2,

- Host Controller (K32L2B) is used to run Headset and OTA\_Headset demos.

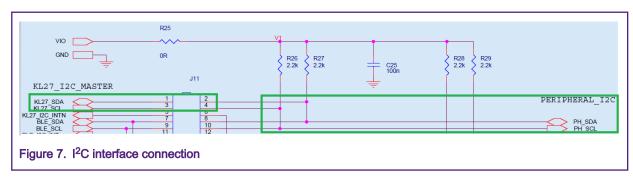

- CODEC (WM8904) is used to program for encoding or decoding a digital data stream or signal. In the software, the I<sup>2</sup>C interface is used to configure the CODEC.

NOTE

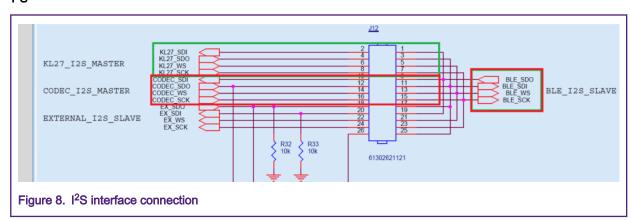

NXH3670 (I<sup>2</sup>S slave) communicates with CODEC (I<sup>2</sup>S master) via the I<sup>2</sup>S directly.

• NXH3670 communicates with K32L2B through the SPI interface.

### 2.2 USB headset software architecture

This document lists only the software design.

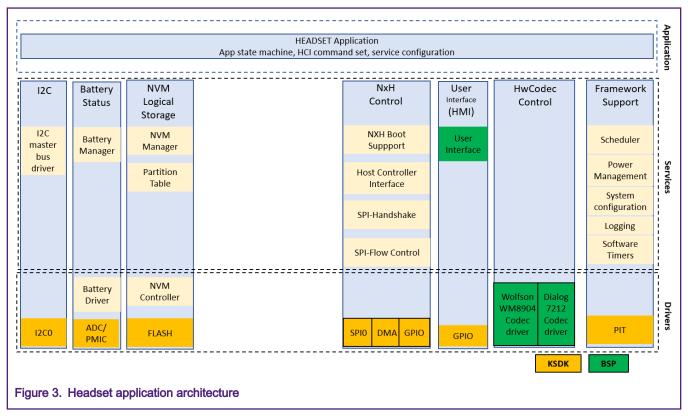

As shown in Figure 3, the Headset application contains NVM service, CODEC service, NXH service, and User Interface service. This document just lists the following functions:

- 1. Nvm service: To read Partition Table.

- 2. NxH Control: To boot, start and transfer data with K32L2B using the SPI interface.

- 3. User Interface: Buttons used to control the volume, start and pause.

- 4. **CODEC service**: To configure CODEC via the I<sup>2</sup>C interface.

In the hardware design, NXH3670 and CODEC are connected via  $I^2S$ , so the audio data can be transmitted directly from NXH3670 to CODEC via  $I^2S$  (users need to initialize the  $I^2C$  peripheral instead of  $I^2S$  peripheral).

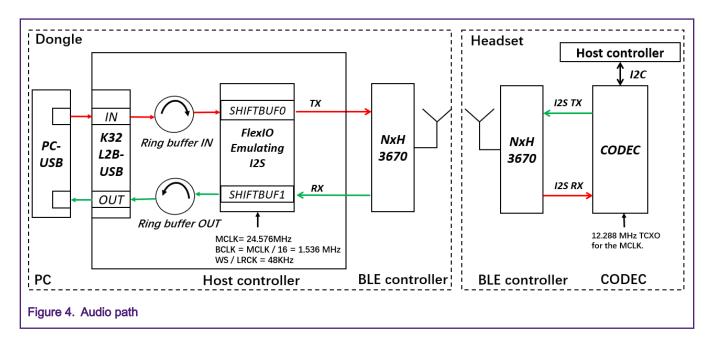

Figure 4 shows the audio transfer process.

Playback (forward channel): The audio path is from the PC to the Headset.

: Record (backward channel): The audio path is from the Headset to the PC.

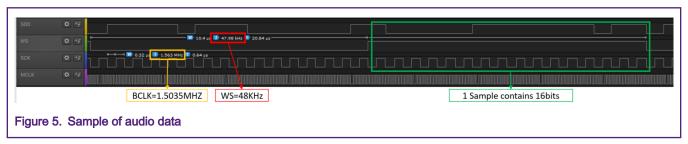

Users can download the demo for 48 KHz/16 bits down stream to test playback function and 48 KHz/16 bits up stream to test record function.

This document only introduces the audio transfer process of the Headset section. For more information on the Dongle section, refer to *K32L2B USB Dongle with NXH3670* (document AN12647).

# 3 Components of K32L2B Headset

#### 3.1 K32L2B

#### 3.1.1 Host controller

The device is highly-integrated, market leading ultra low-power 32-bit microcontroller based on the enhanced Cortex-M0+ (CM0+) core platform. **K32L2B Headset with NXH3670** uses the following features:

- · Core platform clock up to 48 MHz, bus clock up to 24 MHz.

- · Memory option is up to 256 KB flash and 32 KB RAM.

- Wide operating voltage ranges from 1.71–3.6 V with fully functional flash program/erase/read operations.

- Two SPI modules that support 16-bit data length.

- Two inter-integrated circuit (I2C) modules.

- · One FlexIO module.

### 3.1.2 Clock

Two crystals used on the board:

- 32 MHz crystal connected with the NxH3670.

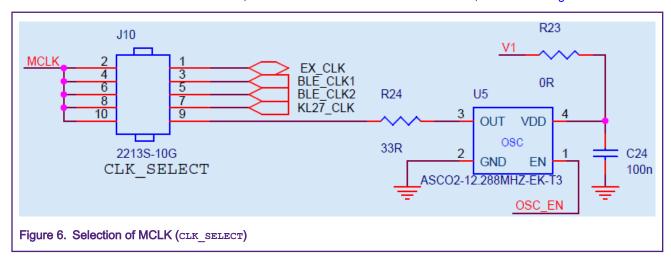

- 12.288 MHz TCXO for the CODEC's MCLK, users can select their clock source via J10, as shown in Figure 6.

# 3.1.3 Serial Wire Debug (SWD)

- A serial wire debug interface is provided on FRDM-K32L2B3 board.

- Users can also download or debug project to FRDM-K32L2B board using CMSIS-DAP or JLINK firmware.

### 3.1.4 Pin connections

Table 1 lists the connection information between K32L2B and other components.

Table 1. Connection information

| Function                                                      | Jumper (K32L2B<br>Headset) | Name       | Jumper (NXH3670)          | Name    |

|---------------------------------------------------------------|----------------------------|------------|---------------------------|---------|

| I <sup>2</sup> S (K32L2B have no I <sup>2</sup> S peripheral) | _                          | CODEC_SDI  | J12_1/9 (I2S_CONFIG)      | BLE_SDO |

|                                                               | _                          | CODEC_SDO  | J12_3/11<br>(I2S_CONFIG)  | BLE_SDI |

|                                                               | _                          | CODEC_WS   | J12_5/13<br>(I2S_CONFIG)  | BLE_WS  |

|                                                               | _                          | CODEC_SCK  | J12_7/15<br>(I2S_CONFIG)  | BLE_SCK |

| I2C0                                                          | J4-4 (PIN PTB1)            | K32L2B_SDA | J11_2<br>(PERIPHERAL_I2C) | PH_SDA  |

Table continues on the next page...

Table 1. Connection information (continued)

| Function      | Jumper (K32L2B<br>Headset) | Name          | Jumper (NXH3670)          | Name          |

|---------------|----------------------------|---------------|---------------------------|---------------|

|               | J4-2 (PIN PTB0)            | K32L2B_SCL    | J11_4<br>(PERIPHERAL_I2C) | PH_SCL        |

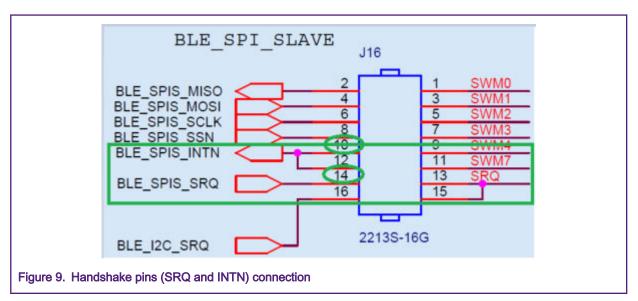

| NXH Handshake | J1_2 (PIN PTA1)            | BLE_SPIS_INTN | J16_9 (BLE_SPI)           | SWM4 (- INTN) |

|               | J1_8 (PIN PTA12)           | BLE_SPIS_SRQ  | J16_13 (BLE_SPI)          | SRQ           |

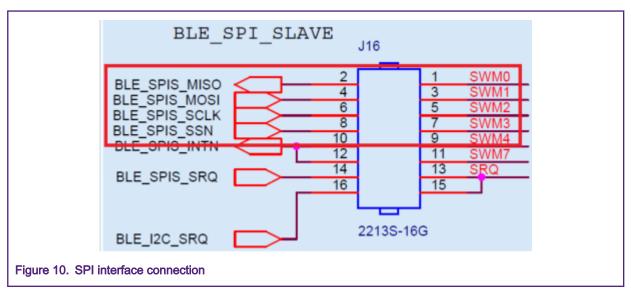

| SPI0          | J1-11 (PIN PTC7)           | BLE_SPIS_MISO | J16_1 (BLE_SPI)           | SW0           |

|               | J1-9 (PIN PTC6)            | BLE_SPIS_MOSI | J16_3 (BLE_SPI)           | SW1           |

|               | J1-15 (PIN PTC5)           | BLE_SPIS_SCLK | J16_5 (BLE_SPI)           | SW2           |

|               | J1-7 (PIN PTC4)            | BLE_SPIS_SSN  | J16_7 (BLE_SPI)           | SW3           |

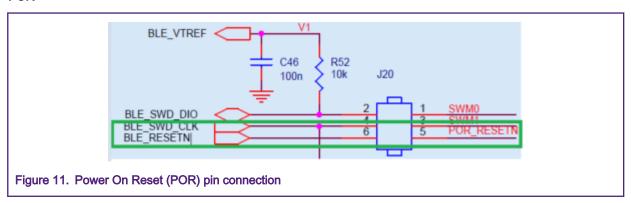

| NXH reset     | J1_4 (PIN PTA2)            | BLE_RESETN    | J20_5 (BLE_SWD)           | POR_RESETN    |

#### 3.1.5 Schematic

- 1. Section 1: Audio transfer

- · I<sup>2</sup>C

Audio data will be transmitted directly from NXH3670 to CODEC via I<sup>2</sup>S. For software,I<sup>2</sup>C peripheral needs to be initialized to configure CODEC instead of I<sup>2</sup>S peripheral.

I<sup>2</sup>S

The NXH3670 is connected with CODEC instead of Host Controller (K32L2B) through I<sup>2</sup>S interface.

- 2. Section 2: NXH3670

- NXH Handshake pin

#### · SPI

### POR

# 3.1.6 Pin configurations

• SPI

8/9

- Interface: SPI0.

- Pins: CS (PTC4), SCK (PTC5), MISO (PTC7), MOSI (PTC6).

- Polarity: Active-high SPI clock (idles low).

- Phase: First edge on SPSCK occurs at the middle of the first cycle of a data transfer.

- Baud Rate: Configure the value of Baud Rate for SPI to 8000000u.

- I<sup>2</sup>C

- Interface: I2C0.

- Pin: SCL (PB.0), SDA (PB.1)

- Configure the value of I<sup>2</sup>C Address to 0x1A.

- · NxH3670 relevant pins

- INIT (PTA1): Configured as digital input.

- SRQ (PTA12): Configured as digital output.

- POR (PTA2): Configured as digital output.

### 3.2 NXH3670

For more information of NXH3670, refer to K32L2B USB dongle with NXH3670 (document AN12647).

# 4 Conclusion

This document describes the hardware design and software architecture (top-level design) of K32L2B\_Headset in the **Bluetooth LE Audio System**. It can be a reference for users to build their own demo.

Application Note

How To Reach Us

Home Page:

nxp.com

Web Support:

nxp.com/support

Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/

SalesTermsandConditions.

While NXP has implemented advanced security features, all products may be subject to unidentified vulnerabilities. Customers are responsible for the design and operation of their applications and products to reduce the effect of these vulnerabilities on customer's applications and products, and NXP accepts no liability for any vulnerability that is discovered. Customers should implement appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, COOLFLUX, EMBRACE, GREENCHIP, HITAG, I2C BUS, ICODE, JCOP, LIFE VIBES, MIFARE, MIFARE CLASSIC, MIFARE DESFire, MIFARE PLUS, MIFARE FLEX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET, TRENCHMOS, UCODE, Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C-Ware, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorlQ, QorlQ Qonverge, Ready Play, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, SMARTMOS, Tower, TurboLink, and UMEMS are trademarks of NXP B.V. All other product or service names are the property of their respective owners. AMBA, Arm, Arm7, Arm7TDMI, Arm9, Arm11, Artisan, big.LITTLE, Cordio, CoreLink, CoreSight, Cortex, DesignStart, DynamlQ, Jazelle, Keil, Mali, Mbed, Mbed Enabled, NEON, POP, RealView, SecurCore, Socrates, Thumb, TrustZone, ULINK, ULINK2, ULINK-ME, ULINK-PLUS, ULINKpro,  $\mu$ Vision, Versatile are trademarks or registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org.

© NXP B.V. 2020.

All rights reserved.

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 01/2020

Document identifier: AN12648