i.MX 6QuadPlus Processor - Quad-Core, High-Performance, Advanced 3D Graphics, HD Video, Advanced Multimedia, Arm® Cortex®-A9 Core

Sign in for a personalized NXP experience.

Click over video to play

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

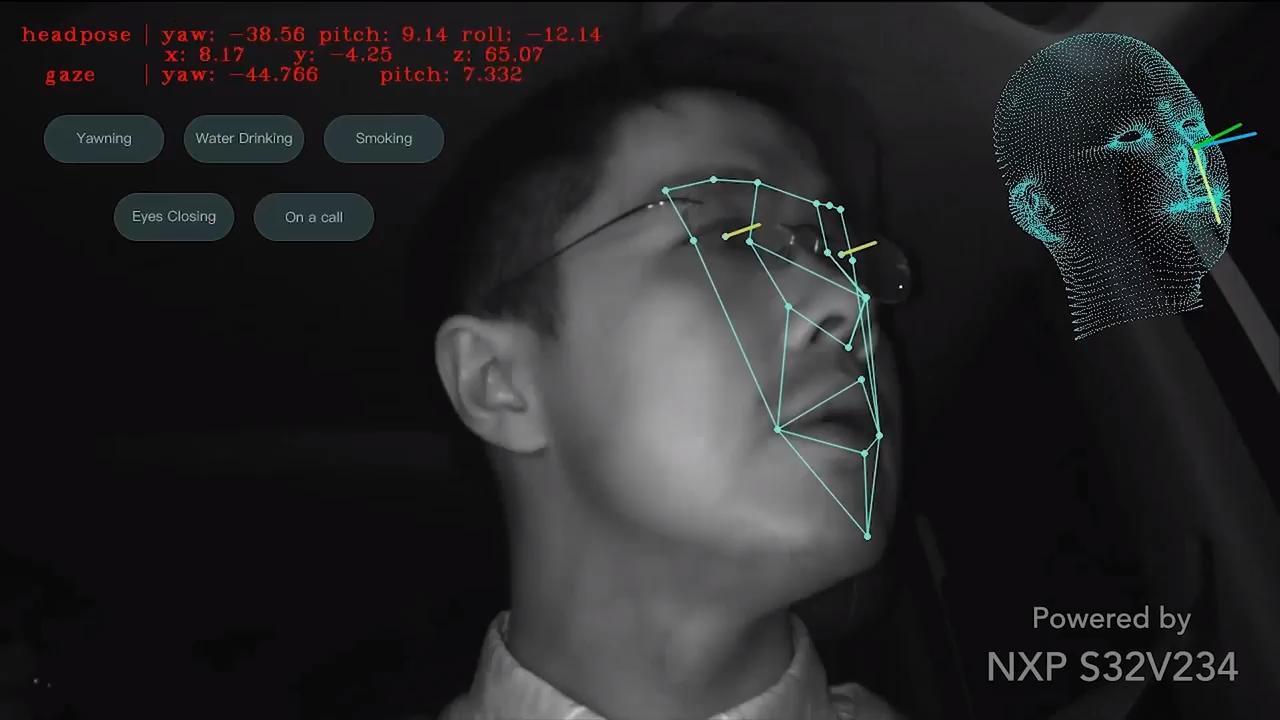

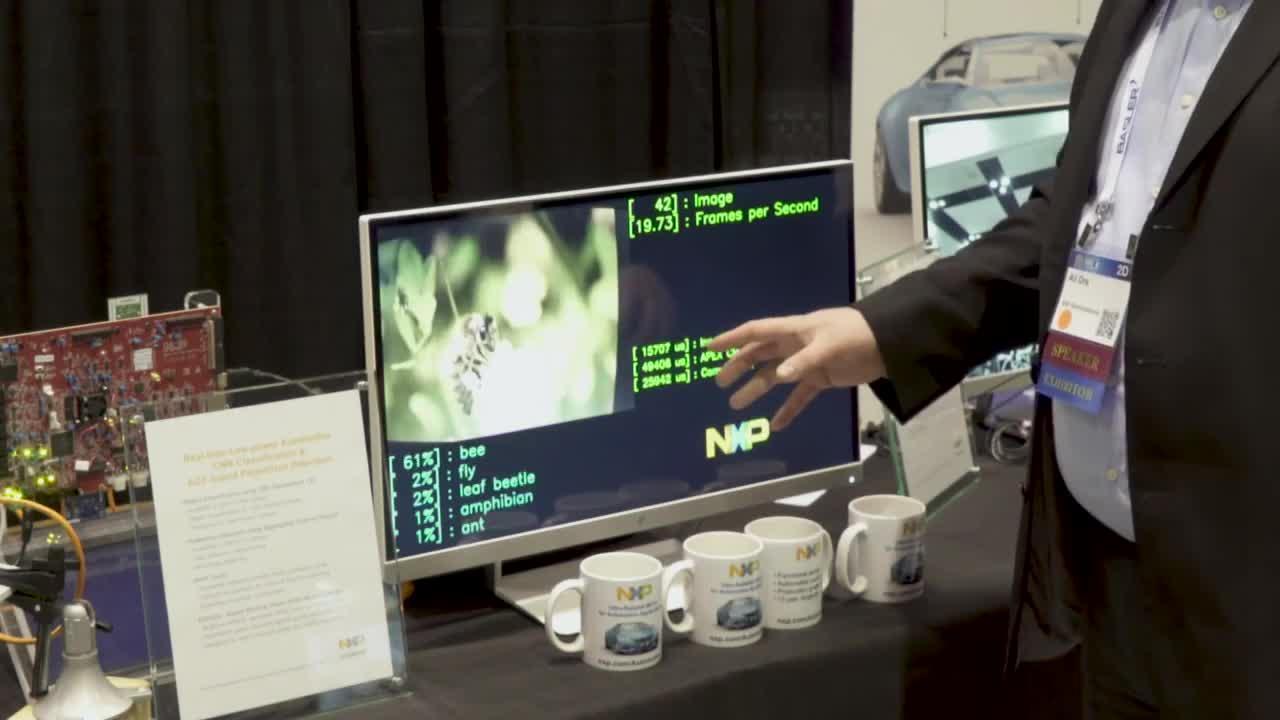

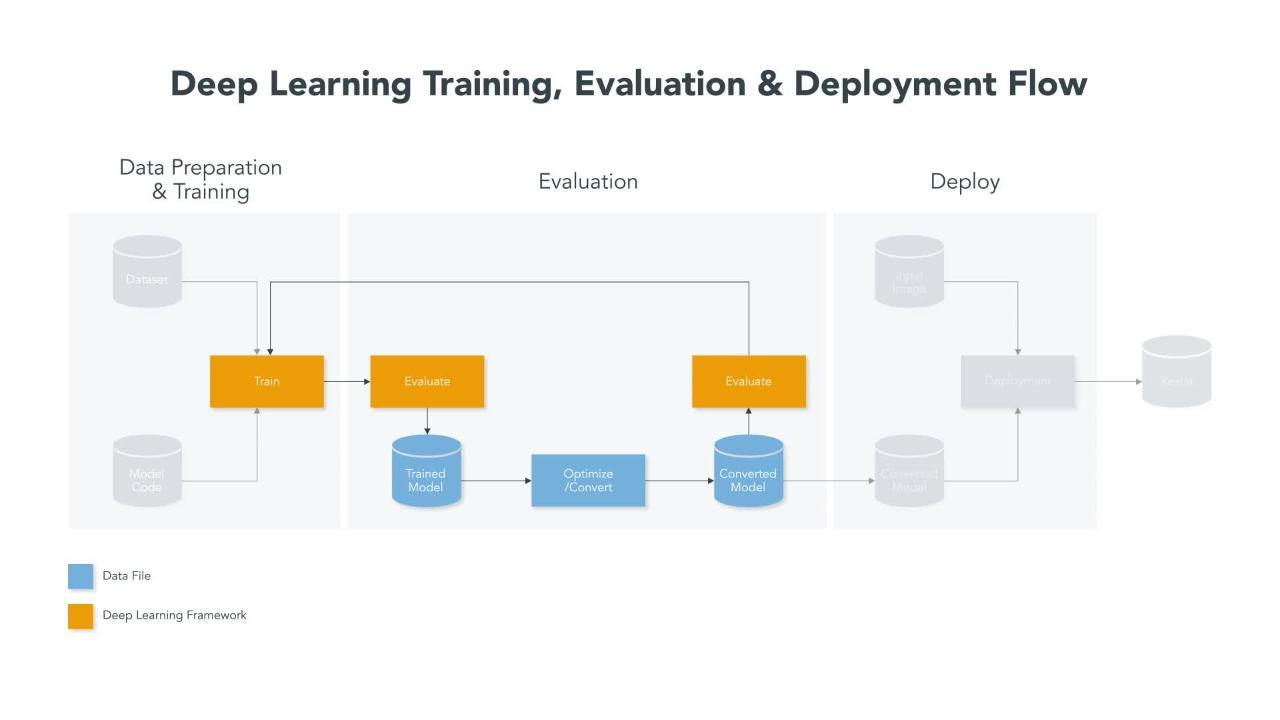

The S32V234 is a second-generation vision processor family and member of the 64-bit Arm® Cortex®-A53 S32V processors. The S32V234 processor offers an image signal processor (ISP), a powerful 3D graphic processor unit (GPU), dual APEX-2 vision accelerators, automotive-grade reliability, functional safety and security capabilities.

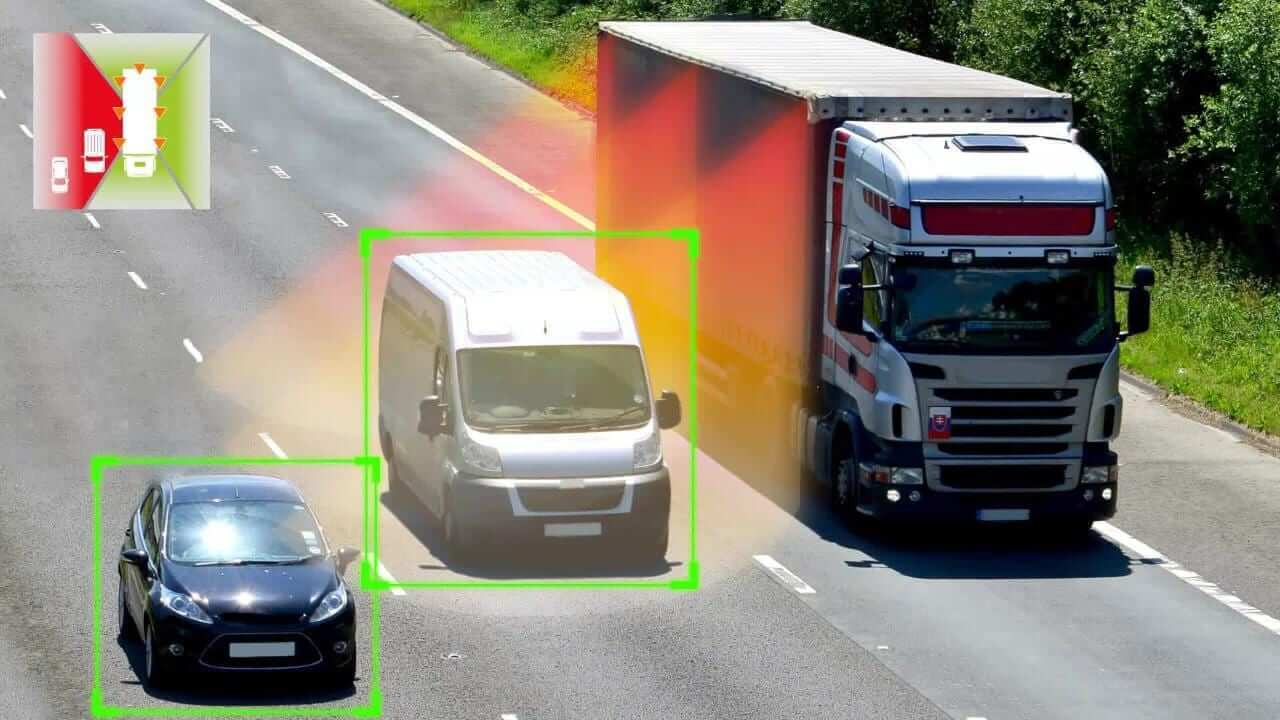

S32V234 processors support computation-intensive ADAS, New Car Assessment Program (NCAP) front camera, object detection and recognition, surround view and automotive and industrial image processing; also, machine learning (ML) and sensor fusion applications.

The S32V234 processor has comprehensive enablement supported by S32 Design Studio IDE for Vision, including a compiler, debugger, Vision SDK, Linux BSP and graph tools.

i.MX 6QuadPlus Processor - Quad-Core, High-Performance, Advanced 3D Graphics, HD Video, Advanced Multimedia, Arm® Cortex®-A9 Core

Multi-Channel (4) PMIC for Automotive Applications – 4 High Power, Fit for ASIL B Safety Level

5 results

Include 11 NRND

Part | Order | CAD Model | Core Type | Operating Frequency [Max] (MHz) | SRAM (kB) | External Memory Interface | Low Leakage | Serial Communication | CAN FD | GPU 2D / GPU 3D | Camera Interfaces | GPIO | Ethernet Type | Human Machine Interface | Security Modules | ADC [Number, bits] | Supply Voltage [Min to Max] (V) | Ambient Operating Temperature (Min to Max) (℃) | Junction Temperature (Min to Max) (℃) | Package Type | Package Pitch (mm) | SafeAssure Functional Safety | ASIL Certification | AEC-Q100 Temperature Range |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

1 x Arm Cortex-M4, 2 x Arm Cortex-A53 | 1000 | 3072 | 1 x uSDHC, 2 x DDR3 SDRAM, 2 x LPDDR2 DRAM, 2 x QSPI | N | 1 x PCIe 2.0, 2 x UART, 3 x SPI | 2 | GC3000 3D | 1 x ISP, 2 x MIPI-CSI-2, 2 x VIU | 162 | 1 Gbps + IEEE 1588 + AVB | system integration unit lite | CSE3 | 8 x 12 | 0.95 to 1.05 | -40 to 105 | -40 to 125 | FBGA621 | 0.65 | ISO 26262 | up to ASIL B | grade 2 | |||

1 x Arm Cortex-M4, 4 x Arm Cortex-A53 | 1000 | 4096 | 1 x uSDHC, 2 x DDR3 SDRAM, 2 x LPDDR2 DRAM, 2 x QSPI | N | 1 x PCIe 2.0, 2 x UART, 3 x SPI | 2 | GC3000 3D | 1 x ISP, 2 x MIPI-CSI-2, 2 x VIU | 162 | 1 Gbps + IEEE 1588 + AVB | system integration unit lite | CSE3 | 8 x 12 | 0.95 to 1.05 | -40 to 105 | -40 to 125 | FBGA621 | 0.65 | ISO 26262 | up to ASIL B | grade 2 | |||

1 x Arm Cortex-M4, 4 x Arm Cortex-A53 | 1000 | 4096 | 1 x uSDHC, 2 x DDR3 SDRAM, 2 x LPDDR2 DRAM, 2 x QSPI | N | 1 x PCIe 2.0, 2 x UART, 3 x SPI | 2 | GC3000 3D | 1 x ISP, 2 x MIPI-CSI-2, 2 x VIU | 162 | 1 Gbps + IEEE 1588 + AVB | system integration unit lite | — | 8 x 12 | 0.95 to 1.05 | -40 to 105 | -40 to 125 | FBGA621 | 0.65 | ISO 26262 | up to ASIL B | grade 2 | |||

1 x Arm Cortex-M4, 4 x Arm Cortex-A53 | 1000 | 4096 | 1 x uSDHC, 2 x DDR3 SDRAM, 2 x LPDDR2 DRAM, 2 x QSPI | N | 1 x PCIe 2.0, 2 x UART, 3 x SPI | 2 | GC3000 3D | 1 x ISP, 2 x MIPI-CSI-2, 2 x VIU | 162 | 1 Gbps + IEEE 1588 + AVB | system integration unit lite | CSE3 | 8 x 12 | 0.95 to 1.05 | -40 to 105 | -40 to 125 | FBGA621 | 0.65 | ISO 26262 | up to ASIL B | grade 2 | |||

1 x Arm Cortex-M4, 4 x Arm Cortex-A53 | 1000 | 4096 | 1 x uSDHC, 2 x DDR3 SDRAM, 2 x LPDDR2 DRAM, 2 x QSPI | N | 1 x PCIe 2.0, 2 x UART, 3 x SPI | 2 | GC3000 3D | 1 x ISP, 2 x MIPI-CSI-2, 2 x VIU | 162 | 1 Gbps + IEEE 1588 + AVB | system integration unit lite | CSE3 | 8 x 12 | 0.95 to 1.05 | -40 to 105 | -40 to 125 | FBGA621 | 0.65 | ISO 26262 | up to ASIL B | grade 2 |

Quick reference to our documentation types.

1-10 of 19 documents

Compact List

There are no results for this selection.

Sign in to access authorized secure files. Learn more about secure access rights.

Please wait while your secure files are loading.

1-10 of 19 documents

Compact List

Receive the full breakdown. See the product footprint and more in the eCad file.

1-5 of 8 hardware offerings

Additional hardware available. View our featured partner solutions.

Sign in to access authorized secure files. Learn more about secure access rights.

2 hardware offerings

.jpg?imwidth=300)

To find additional partner offerings that support this product, visit our Partner Marketplace.

1-5 of 8 hardware offerings

Additional hardware available. View our featured partner solutions.

Quick reference to our software types.

1-5 of 22 software files

Additional software available. View our featured partner solutions.

Note: For better experience, software downloads are recommended on desktop.

Sign in to access authorized secure files. Learn more about secure access rights.

Please wait while your secure files are loading.

1-5 of 21 software offerings

To find additional partner offerings that support this product, visit our Partner Marketplace.

1-5 of 22 software files

Additional software available. View our featured partner solutions.

Note: For better experience, software downloads are recommended on desktop.

1-5 of 6 engineering services

.svg)

There are no results for this selection.

There are no results for this selection.

To find additional partner offerings that support this product, visit our Partner Marketplace.

1-5 of 12 trainings

Additional trainings are available. View our featured partner trainings.

12 trainings

Additional trainings are available. View our featured partner trainings.

9 trainings

To find additional partner offerings that support this product, visit our Partner Marketplace.

There are no recently viewed products to display.

Help us improve your experience on our site. We invite you to take our five-question survey.