# Application Hints Fail-Safe CAN / LIN System Basis Chips

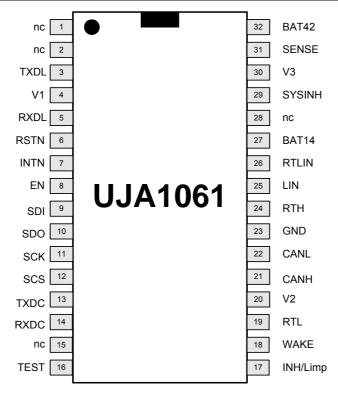

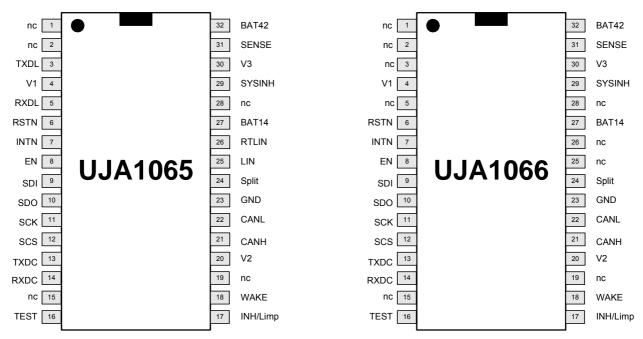

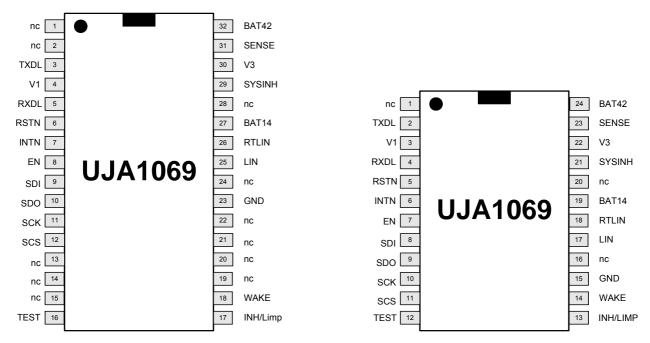

UJA1061, UJA1065, UJA1069

Version 2.9

Authors:

Thorsten Kauder, Matthias Muth, Martin Wagner

Date: 22nd of September 2010

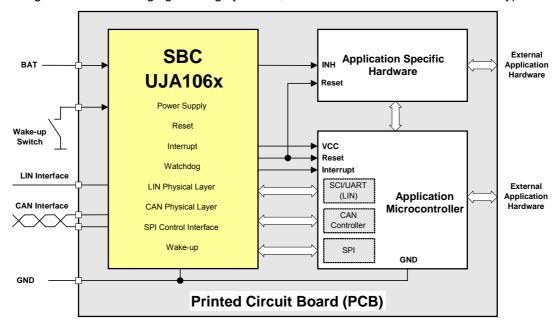

# Fail-safe System Basis Chips UJA106x

#### **Revision History**

| Date                                                                                                                                                                                                                                                                                                                        | Version                                                                                                                             | Remarks                                                                                                                                                                                                                                                                                                                                                                                 |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 14.03.2003                                                                                                                                                                                                                                                                                                                  | V 1.0                                                                                                                               | Initial Version                                                                                                                                                                                                                                                                                                                                                                         |  |

| 18.11.2003                                                                                                                                                                                                                                                                                                                  | V 1.1                                                                                                                               | Jpdated                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 01.01.2006                                                                                                                                                                                                                                                                                                                  | V 2.0                                                                                                                               | Completely revised version according to the final SBC functionality                                                                                                                                                                                                                                                                                                                     |  |

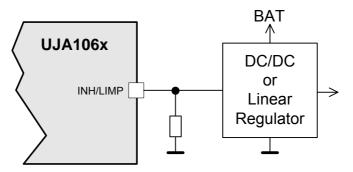

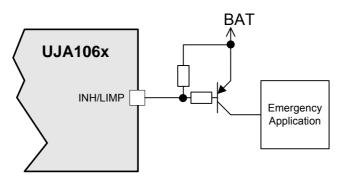

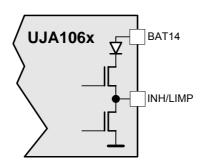

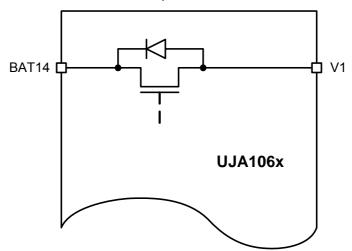

| 10.03.2006                                                                                                                                                                                                                                                                                                                  | V 2.1                                                                                                                               | <ul> <li>UJA1062 deleted from document. This derivative will not be developed</li> <li>Figures 1-2 to 1-5 corrected. INH/LIMP connected to BAT14 instead of BAT42</li> <li>Sections 2.5 and 2.10 updated</li> <li>Information about internal circuitry added in Pictures 2-10, 2-12, 2-13, 2-15, 2-18 and 2-21</li> <li>A.2 Design Checklist – Three new items added H13-H15</li> </ul> |  |

| 08.06.2006                                                                                                                                                                                                                                                                                                                  | V 2.2                                                                                                                               | <ul> <li>Corrected Document Header</li> <li>FAQ 7, 8 and 9 added</li> <li>Figure 1-2 and Section 1.1.1 warning added concerning SENSE in UJA1061.</li> <li>Several references to 1.1.1 concerning SENSE in UJA1061</li> <li>Section 2.2 and 2.3 updated</li> <li>Figure 2-2 updated</li> <li>Design Checklist – Item H02a added</li> </ul>                                              |  |

| 23.06.2006                                                                                                                                                                                                                                                                                                                  | V 2.2.1                                                                                                                             | Document footer added/repaired     Appendix 3 updated for Adobe™ Reader 7.0                                                                                                                                                                                                                                                                                                             |  |

| LIN Ferrite removed     Footnotes Corrected     Appendix B – References Updated     Figure 2.5 Corrected     6.5.4 Revised     Comment on unused bytes in A1     Software Design issue S02 changed     Added information in 4.5                                                                                             |                                                                                                                                     | <ul> <li>Footnotes Corrected</li> <li>Appendix B – References Updated</li> <li>Figure 2.5 Corrected</li> <li>6.5.4 Revised</li> <li>Comment on unused bytes in A1</li> <li>Software Design issue S02 changed</li> </ul>                                                                                                                                                                 |  |

| 11.10.2007                                                                                                                                                                                                                                                                                                                  | V 2.4                                                                                                                               | 4.1.2 Footnote added     A.6 FAQ updated                                                                                                                                                                                                                                                                                                                                                |  |

| 08.02.2008                                                                                                                                                                                                                                                                                                                  | 02.2008 V 2.5 • Table A-2 updated • A.4.1 updated                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 22.05.2008                                                                                                                                                                                                                                                                                                                  | • Figure 2-11: Figure updated • Chapter 4.6 inserted • Chapter 5.4: Remark about UJA1066 inserted • Chapter 6.5.2: Footnote 6 added |                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 13.08.2008                                                                                                                                                                                                                                                                                                                  | V 2.7                                                                                                                               | Section 5.5.3.4 updated (behavior for V1CMC = 0)                                                                                                                                                                                                                                                                                                                                        |  |

| Section 2.7, correction of LIN supply voltage     Section 3; note about NC pins added     Section 5.4.1, equations for minimum and maximum trigger point updated     References on 3.0V version and 3.3V version for UJA1069 removed     Section A.7 inserted to clarify Device Identification Codes     References updated |                                                                                                                                     | <ul> <li>Section 3; note about NC pins added</li> <li>Section 5.4.1, equations for minimum and maximum trigger point updated</li> <li>References on 3.0V version and 3.3V version for UJA1069 removed</li> </ul>                                                                                                                                                                        |  |

| 22.09.2010                                                                                                                                                                                                                                                                                                                  | V 2.9                                                                                                                               | Section 9, bypassing of interrupt limitation feature                                                                                                                                                                                                                                                                                                                                    |  |

### Fail-safe System Basis Chips UJA106x

#### **Preface**

Compared to the previous version 1, these application hints version 2 have been updated according to the final silicon behavior of the fail-safe SBC family UJA106x. During the evolution of the SBC family some important optimizations of the fail-safe system approach were made resulting in some changes in the software and hardware interface of this SBC family.

This new release should help all hardware and software designers building safe and reliable systems based on our fail-safe System Basis Chip family. Especially the checklists within the appendix are very useful to walk through the individual application hardware and software in order to make sure that the main application cases are covered by the system.

In case of any questions or suggestions for improvements of this document, please feel free to contact us.

The authors.

# Fail-safe System Basis Chips UJA106x

#### **Table of Contents:**

| 1. | OVE          | RVIEW                                                                                                                                                                                                                                                                | 9          |

|----|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

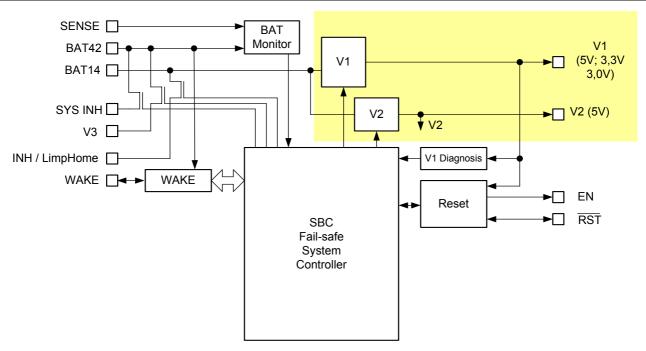

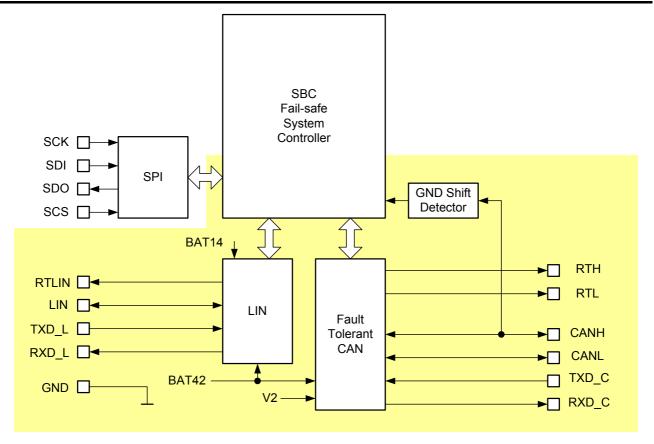

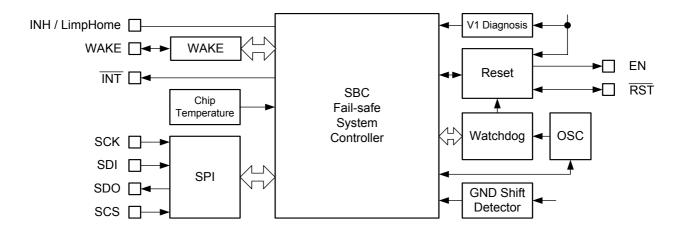

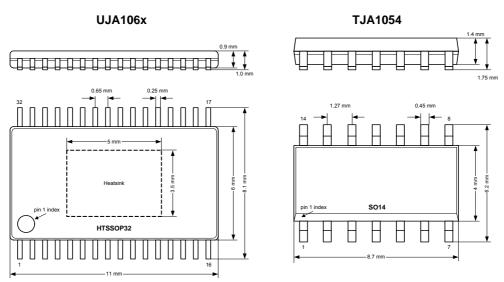

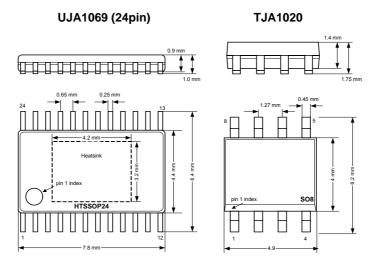

|    | 1.1.         | Highlights of the UJA106x SBC family  1.1.1 Power Supply System  1.1.2 Voltage Regulators  1.1.3 Physical Layers, CAN & LIN.  1.1.4 System Safety Features  1.1.5 Low-power Support  1.1.6 Flash Memory Support  1.1.7 Software Development Support  1.1.8 Packaging | 1315151616 |

| 2. | HAF          | RDWARE DESIGN                                                                                                                                                                                                                                                        | 18         |

|    | 2.2.<br>2.3. | 14V ECU Supply Environment                                                                                                                                                                                                                                           | 18         |

|    |              | 2.4.1. Voltage Regulator V1                                                                                                                                                                                                                                          | 2´<br>2´   |

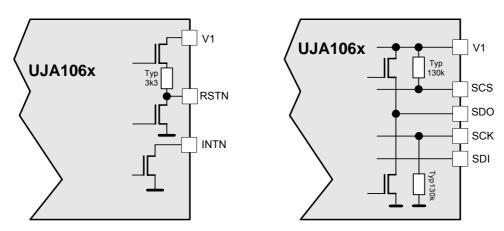

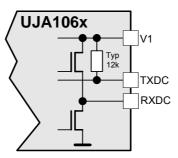

|    |              | Microcontroller Interface                                                                                                                                                                                                                                            | 23         |

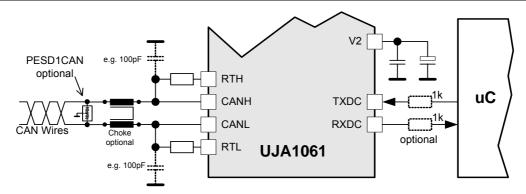

|    | 2.6.         | CAN Transceiver Interface                                                                                                                                                                                                                                            | 25         |

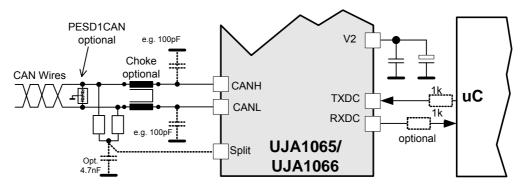

|    | 27           | 2.6.2. UJA1065/66 – High Speed CAN Transceiver                                                                                                                                                                                                                       |            |

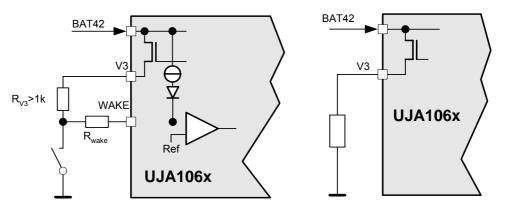

|    | 2.8.<br>2.9. | Local Wake-up Interface, V3 Output                                                                                                                                                                                                                                   | 28         |

| 3. |              | NING / LAYOUT / FMEA                                                                                                                                                                                                                                                 |            |

| ٠. |              | Layout Issues                                                                                                                                                                                                                                                        |            |

|    |              | Pin FMEA                                                                                                                                                                                                                                                             |            |

| 4. | SOF          | TWARE MEETS HARDWARE                                                                                                                                                                                                                                                 | <b>4</b> 1 |

|    | 4.1.         | Supply System                                                                                                                                                                                                                                                        |            |

|    |              | 4.1.1. Battery Monitoring                                                                                                                                                                                                                                            |            |

|    |              | 4.1.3. CAN Transceiver, V2 Supply Monitoring                                                                                                                                                                                                                         | 42         |

|    | 4.2.         | 4.1.4. V3 Monitoring                                                                                                                                                                                                                                                 | 43         |

|    |              | 4.2.1.1. System Behaviour upon a wake-up via WAKE                                                                                                                                                                                                                    |            |

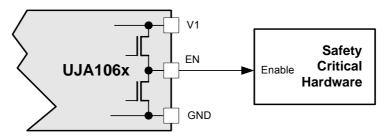

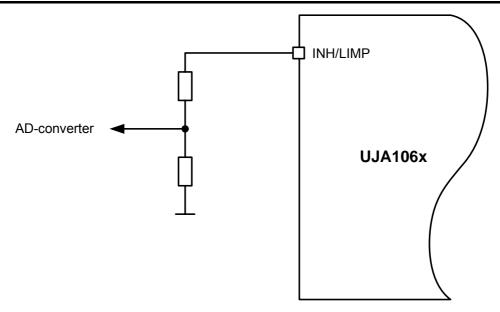

|    | 4.3.         | INH/LIMP Pin                                                                                                                                                                                                                                                         | 44         |

|    | 4.4.         |                                                                                                                                                                                                                                                                      |            |

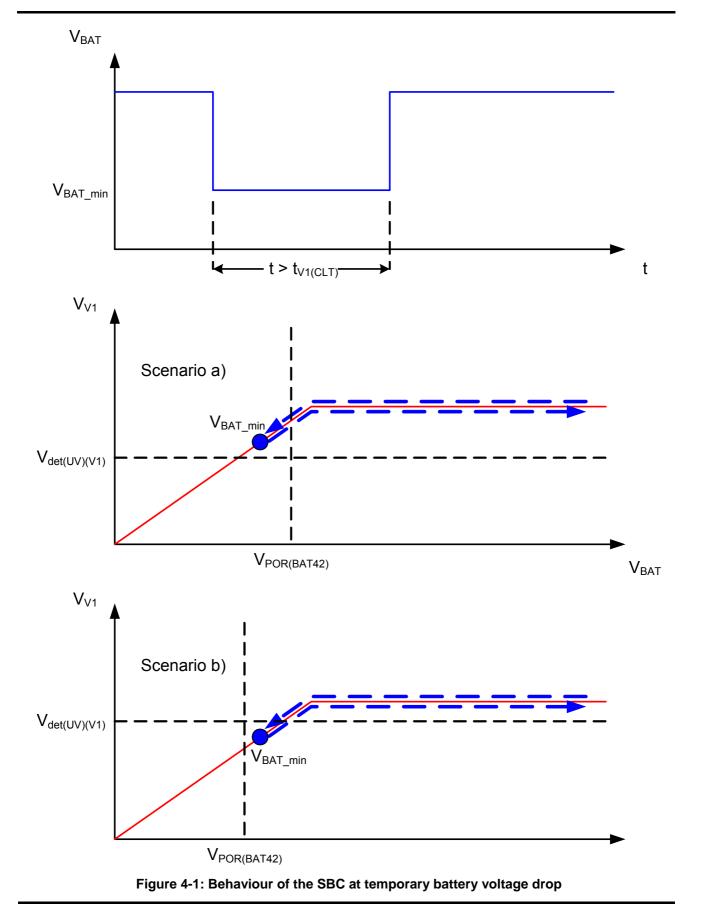

|    |              | Temperature MonitoringBehaviour at battery undervoltage                                                                                                                                                                                                              |            |

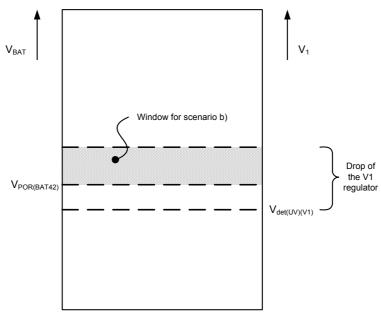

|    | 4.0.         | 4.6.1.1. Example: Calculation of the maximum width of the window for scenario b)                                                                                                                                                                                     |            |

| 5  | GFI          | TING STARTED MODES OF THE SBC                                                                                                                                                                                                                                        | 47         |

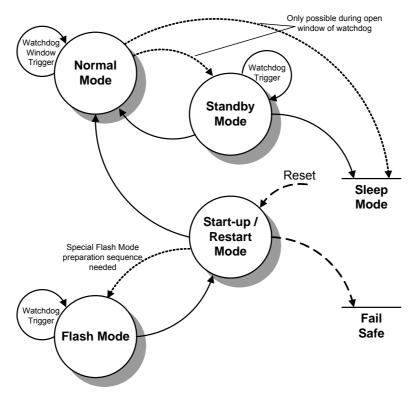

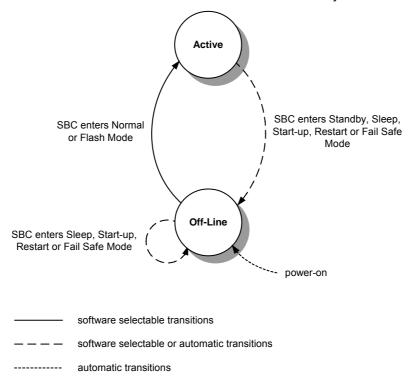

|    | 5.1.       | Software View of SBC Operating Modes                           | 47 |

|----|------------|----------------------------------------------------------------|----|

|    |            | Simplified software state diagram of the UJA106x               |    |

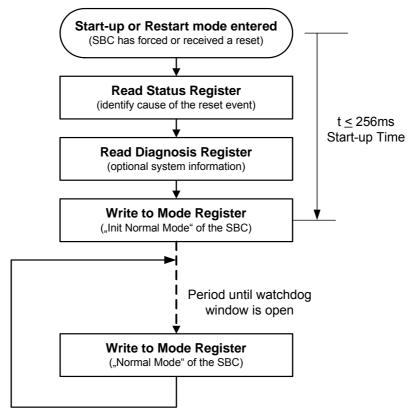

|    |            | Start-up / Restart Mode                                        |    |

|    |            | 5.3.1. Register access during Start-up or Restart Mode         |    |

|    |            | 5.3.2. CAN / LIN Status during Start-up or Restart Mode        |    |

|    |            | 5.3.3. V3 Status during Start-up or Restart Mode               |    |

|    |            | 5.3.4. EN Status during Start-up or Restart Mode               | 50 |

|    |            | 5.3.5. Transition from Start-up to Restart Mode                |    |

|    |            | 5.3.6. Transition from Restart to Fail-safe mMode              |    |

|    |            | 5.3.7. Entering Normal Mode                                    |    |

|    | 5.4.       | Normal Mode                                                    |    |

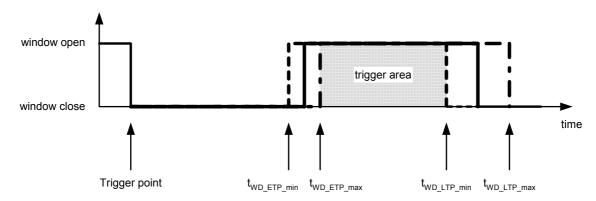

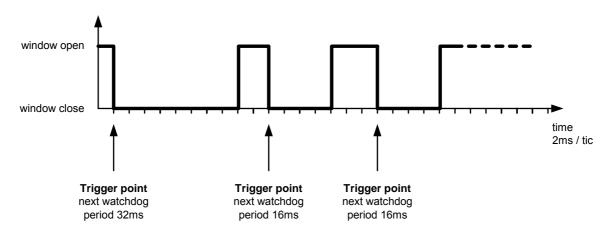

|    |            | 5.4.1. Watchdog triggering                                     |    |

|    |            | 5.4.1.1 Example: Watchdog Triggering, entering Sleep Mode      |    |

|    | 5.5.       | Standby Mode                                                   |    |

|    |            | 5.5.1. V1 Status during Standby Mode                           |    |

|    |            | 5.5.2. V2 and CAN status during Standby Mode                   |    |

|    |            | 5.5.3. Watchdog Behaviour in Standby Mode                      |    |

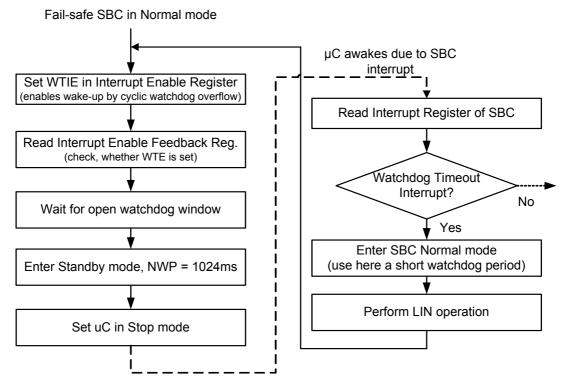

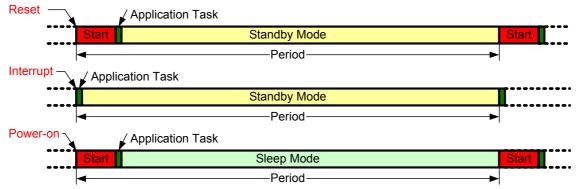

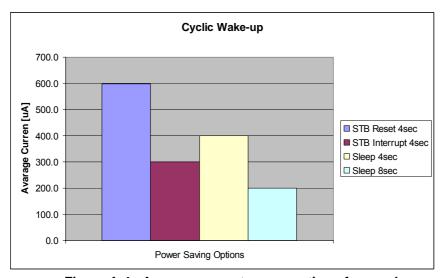

|    |            | 5.5.3.2. Cyclic wake-up out of Standby Mode via hardware reset |    |

|    |            | 5.5.3.3. Cyclic wake-up in Standby Mode via interrupt          |    |

|    |            | 5.5.3.4. Disabling the Watchdog                                |    |

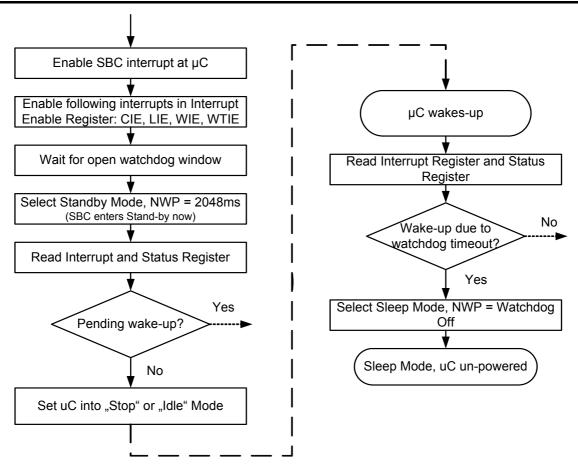

|    |            | 5.5.3.5. Example: Cyclic wake-up via watchdog                  | 56 |

|    | 5.6.       | Sleep Mode                                                     | 57 |

|    |            | 5.6.1. CAN and LIN Status during Sleep Mode                    | 57 |

|    |            | 5.6.2. INH/LIMP during Sleep Mode                              |    |

|    |            | 5.6.3. EN behaviour during Sleep Mode                          |    |

|    |            | 5.6.4. V3 and WAKE pin behaviour during Sleep Mode             |    |

|    |            | 5.6.5. Leaving Sleep Mode                                      |    |

|    |            | 5.6.6. Example : Entering Sleep Mode via Standby Mode          |    |

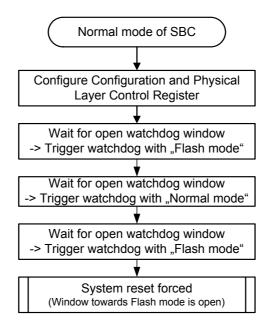

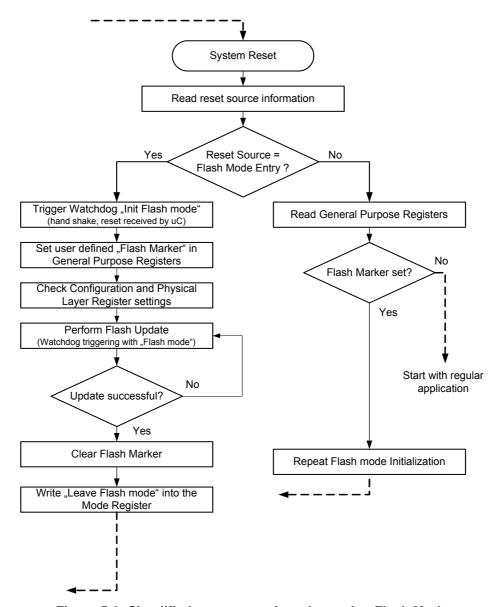

|    | 5.7.       | Flash Mode                                                     |    |

|    |            | 5.7.1. Entering Flash Mode                                     |    |

|    |            | 5.7.2. Leaving Flash Mode                                      |    |

|    | <b>5</b> 0 | 5.7.3. Behaviour during Flash Mode                             |    |

|    | 5.6.       | Special modes for evaluation purposes                          |    |

|    |            | 5.8.1.1. Behaviour during Software Development Mode            |    |

|    |            | 5.8.1.2. Entering Software Development Mode                    |    |

|    |            | 5.8.1.3. Example: Using the Software Development Mode          | 62 |

|    |            | 5.8.2. Forced Normal Mode                                      |    |

| 6. | THE        | CAN TRANSCEIVER                                                | 63 |

|    | 6 1        | Introduction                                                   | 63 |

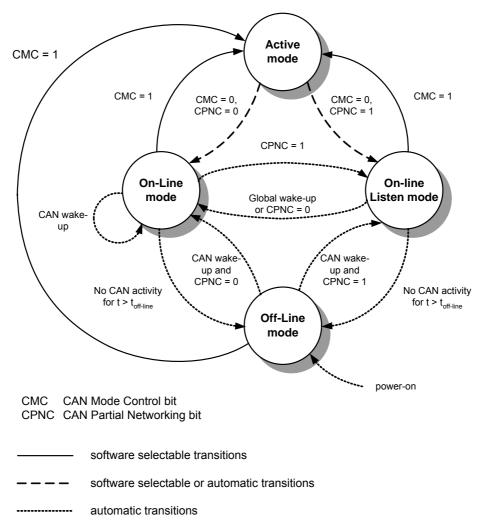

|    |            | CAN Modes                                                      |    |

|    | 0.2.       | 6.2.1. Active Mode of CAN                                      |    |

|    |            | 6.2.1.1 Listen-only Mode of CAN                                |    |

|    |            | 6.2.2. On-line Mode of CAN                                     |    |

|    |            | 6.2.3. On-line Listen Mode of CAN                              |    |

|    |            | 6.2.4. Off-line Mode of CAN                                    |    |

|    | 6.3.       | Power supply for CAN                                           | 66 |

|    |            | 6.3.1. Activating CAN                                          |    |

|    |            | 6.3.2. V2 failure                                              |    |

|    | 6.4.       | CAN wake-up                                                    | 67 |

|    |            | 6.4.1. Reaction upon a CAN wake-up                             | 67 |

|    |            |                                                                |    |

|    | 6.5. | 6.4.2. Definition of the CAN wake-up message                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 68 |

|----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|    |      | 6.5.1. Bus failure diagnosis with fault-tolerant CAN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 68 |

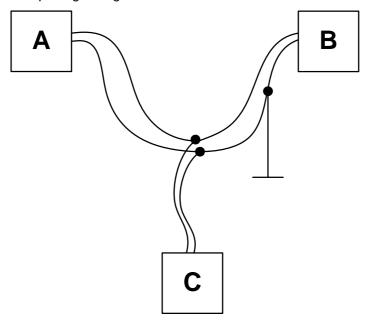

|    |      | 6.5.1.1. Example: Recessive clamped wire detection within a 3-Node Network 6.5.2. Bus failure diagnosis with high-speed CAN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

|    |      | 6.5.3. Diagnosis of TXD-RXD failures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|    |      | 6.5.4. GND shift diagnosis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|    |      | 6.5.5. Emulation of Error Pin functionality (NERR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|    | 6.6. | Partial Networking in a CAN System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|    |      | Differences between high-speed CAN and fault-tolerant CAN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

|    | •    | 6.7.1. General differences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

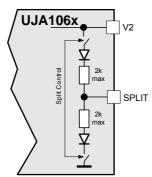

|    |      | 6.7.2. SPLIT Pin of High-Speed CAN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| 7. | THE  | LIN TRANSCEIVER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 72 |

|    | 7.1. | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 72 |

|    |      | LIN modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

|    |      | 7.2.1. Active Mode of LIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

|    |      | 7.2.1.1. Slope control of LIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

|    |      | 7.2.1.2. "Cooling" applications with enhanced driver strength                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

|    |      | 7.2.1.3. Listen-only Mode of LIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|    |      | 7.2.2. Off-line Mode of LIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

|    | 7.3. | LIN wake-up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

|    |      | 7.3.1. Reaction upon a LIN wake-up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|    |      | 7.3.2. Definition of the LIN wake-up message                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

|    | 7 1  | 7.3.3. Deactivation of the LIN wake-up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

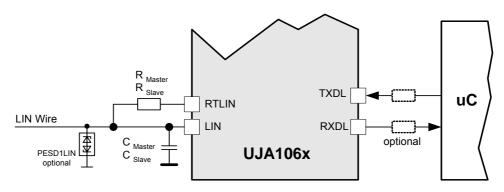

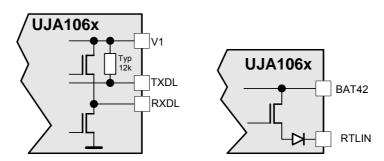

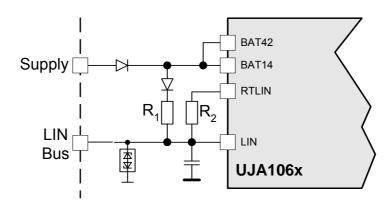

|    |      | LIN termination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|    |      | Failure Diagnosis with the LIN Transceiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |