# **MFS5600AVMABEP – NXP Standard**

## Configuration report for FS5600-QM OTP program ID: AB rev A

### Rev. 1.0 - 9/8/2022

Report

### **1** General description

The FS5600 integrates a battery connected DC-DC controller with external FETs and a battery connected DC-DC converter with internal FETs. In addition, it offers functional safety features such as independent voltage monitors, windowed watchdog timer, I/O monitoring via ERRMON and FCCU and build-in-self-test.

Note: Electrical characteristics are maintained in the FS5600 data sheet

## 2 Features and benefits

- 2 x High-Voltage Buck Converters:

- Buck Controller External FETs 900 mA gate drive current

- Buck Regulator Internal FETs 3 A+ load capability

- ±1.5 % Output Accuracy

- 250 kHz to 3 MHz switching frequency

- High-efficiency PFM mode

- Safety Features:

- Available in Enhanced ASIL B, ASIL B, and QM variations

- 2 internal and up to 4 high-accuracy external voltage monitors

- Windowed Watchdog Timer

- ERRMON and FCCU monitoring

- 2 x PGOOD and 1 x FS0B outputs

- ABIST and LBIST for latest failure check

- GPIOs for seamless operation with PF PMICs

- Rated from -40 °C to 150 °C TJ

- 32-Ld 5 mm x 5 mm QFN

- AEC-Q100 Grade-1 Qualified

R\_MFS5600AVMABEP

All information provided in this document is subjected to legal disclaimers. ©NXP B.V. 2022. All rights reserved.

Report

## **3 Applications**

- Infotainment / Cluster / Driver Awareness

- Telematics

- V2X

- Radar

- Vision

- ADAS

- Sensor fusion

## **4 Ordering information**

#### Table 1. Ordering information

| Type number <sup>[1]</sup> | Package |                                                                                                                         |           |

|----------------------------|---------|-------------------------------------------------------------------------------------------------------------------------|-----------|

|                            | Name    | Description                                                                                                             | Version   |

| MFS5600AVMABEP             | HVQFN32 | HVQFN32 plastic thermally enhanced low profile quad flat package. 32 terminals; 0.5mm pitch; 5 mm x 5 mm x 0.85 mm body | SOT617-24 |

[1] To order parts in tape and reel, add the R2 suffix to the part number.

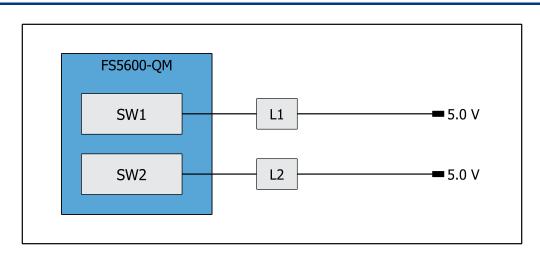

## **5 Hardware configuration diagram**

## **6 OTP configuration**

See FS5600 datasheet for parametric details. The OTP configuration summary for AB sequence ID is provided in Tables below.

#### Table 2. PGOOD and GPIO Control

| Functional block      | Feature                  | OTP selection              |

|-----------------------|--------------------------|----------------------------|

|                       | SW1 Under Voltage PGOOD1 | SW1 asserts PGOOD1         |

| PGOOD1 CTRL           | SW1 Over Voltage PGOOD1  | SW1 asserts PGOOD1         |

|                       | SW2 Under Voltage PGOOD1 | SW2 will not assert PGOOD1 |

|                       | SW2 Over Voltage PGOOD1  | SW2 will not assert PGOOD1 |

|                       | SW1 Under Voltage PGOOD2 | SW1 will not assert PGOOD2 |

| PGOOD2 CTRL           | SW1 Over Voltage PGOOD2  | SW1 will not assert PGOOD2 |

|                       | SW2 Under Voltage PGOOD2 | SW2 asserts PGOOD2         |

|                       | SW2 Over Voltage PGOOD2  | SW2 asserts PGOOD2         |

|                       | Delay Duration Of PGOOD1 | No Delay                   |

|                       | Delay Duration Of PGOOD2 | No Delay                   |

| PGOOD and GPIO Timing | Delay Duration Of GPIO1  | Low                        |

|                       | Delay Duration Of GPIO2  | Low                        |

|                       | Delay Duration Of GPIO3  | Low                        |

|                       | GPIO1 Configuration      | Output is high Z           |

| GPIO Configuration    | GPIO2 Configuration      | GPO (output)               |

|                       | GPIO3 Configuration      | GPO (output)               |

#### Table 3. Regulators

| Functional block    | Feature     | OTP selection |

|---------------------|-------------|---------------|

| SW1 Enable and Mode | SW1 Mode    | PWM           |

|                     | SW1 Voltage | 5.0 V         |

R\_MFS5600AVMABEP

| SW2 Enable and Mode   | SW2 Mode                             | PWM                           |

|-----------------------|--------------------------------------|-------------------------------|

|                       | SW2 Voltage                          | 5.0 V                         |

|                       | SW1 Clock Select                     | CLK2                          |

| SW/4 Loop design      | SW1 Transconductance                 | 28 us                         |

| SW1 Loop design       | SW1 Slope                            | 90 mV/us                      |

|                       | SW1 Resistor Compensation            | 150 KOhm                      |

| SW2 Loop design       | SW2 Clock Select                     | CLK2                          |

|                       | SW2 Slope Compensation               | 82 mV/us                      |

|                       | SW1 Soft Start Ramp Slew Rate        | 675 us                        |

|                       | Peak Current Limit                   | 6.5 A                         |

| SW1 Misc              | SW1 PFM On-time                      | 630 ns                        |

|                       | SW1 Minimum On-time                  | 80 ns                         |

|                       | SW1 Pull Down                        | Pull Down Enabled             |

|                       | SW2 Soft Start Ramp Slew Rate        | 5 mV/us                       |

|                       | SW2 Peak Current Limit Sense Voltage | 150 mV                        |

|                       | SW2 PFM On-time                      | 300 ns                        |

| SW2 Misc              | SW2 Minimum On-time                  | 45 ns                         |

|                       | SW2 Pulldown Resistor                | Pull Down Enabled             |

|                       | SW2 High Slew Rate                   | 2.8 Ohm PullUp/1.7 Ohm PullDn |

|                       | SW2 Low Slew Rate                    | 1 Ohm PullUp/PullDn           |

| SW1 and SW2 OFF Delay | SW1 Turn Off Delay                   | Off after EN1 goes low        |

|                       | SW2 Turn Off Delay                   | Off after EN2 goes low        |

| Clock Management      | Clock1 Divide Ratio                  | CLK1 = CLK_FREQ / 8           |

|                       | Clock2 Divide Ratio                  | CLK1 = CLK_FREQ / 48          |

|                       |                                      |                               |

R\_MFS5600AVMABEP

| Input Frequency Range At SYNCIN Pin | 2000 KHz and 3000 KHz |

|-------------------------------------|-----------------------|

| Clock Frequency (MHz)               | 22 MHz                |

| Frequency Spread Spectrum           | Enabled               |

| Modulation Frequency                | 22 KHz                |

#### Table 5. Miscellaneous

| Functional block      | Feature                 | OTP selection                                |

|-----------------------|-------------------------|----------------------------------------------|

| MODE/SYNCIN Selection | Mode Select For SYNCINB | MODE                                         |

|                       | MODE Debounce           | Falling Edge - 40 us and Rising Edge - 10 us |

| I2C Configuration     | Device Address          | 0x18                                         |

## 8 Legal information

#### 8.1 Definitions

**Draft** - The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Limited warranty and liability - Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory. Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

**Right to make changes** - NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use - NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

Applications - Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification. Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products. NXP Semiconductors does not accept any liability related to any default, damage, costs or problem

which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Limiting values - Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

Terms and conditions of commercial sale - NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at http://www.nxp.com/profile/terms,unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors here by expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**No offer to sell or license** - Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

Suitability for use in automotive applications - This NXP Semiconductors product has been qualified for use in automotive applications. Unless otherwise agreed in writing, the product is not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Export control** - This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Translations** - A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

#### 8.2 Trademarks

**Notice:** All referenced brands, product names, service names and trademarks are the property of their respective owners. **NXP** - is a trademark of NXP B.V.

R\_MFS5600AVMABEP

## Contents

| <ul> <li>2 Features and benefits</li></ul>                  | 1 General description            | 1 |

|-------------------------------------------------------------|----------------------------------|---|

| 4 Ordering information                                      | 2 Features and benefits          | 1 |

| 5 Hardware configuration diagram 2<br>6 OTP configuration 3 | 3 Applications                   | 2 |

| 6 OTP configuration 3                                       | 4 Ordering information           | 2 |

| _                                                           | 5 Hardware configuration diagram | 2 |

| 7 Legal information 6                                       | 6 OTP configuration              | 3 |

|                                                             | 7 Legal information              | 6 |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

© NXP B.V. 2022 .

All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

> Date of release: 9/8/2022 Document identifier: R\_MFS5600AVMABEP