#### **Freescale Semiconductor**

# **CPM Interrupt Controller**

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document. Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

© Freescale Semiconductor, Inc., 2004. All rights reserved.

## What is the CPIC?

Definition

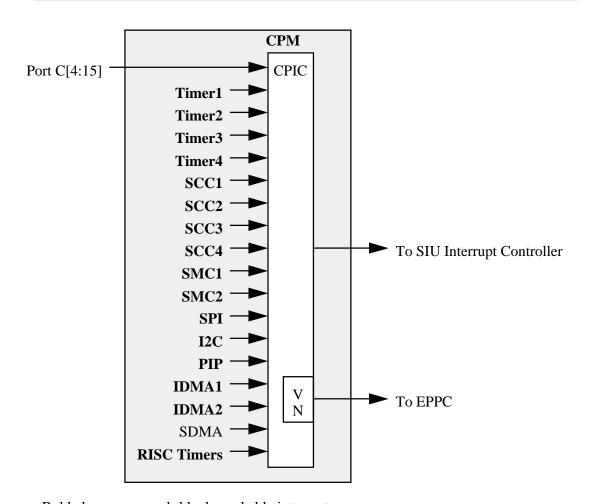

The CPIC is the focal point for all interrupts associated with the CPM. It accepts and prioritizes all the internal and external interrupts from all functional blocks associated with the CPM.

Example

Bolded names are sub-block maskable interrupt sources.

#### **CPIC** Features

Important functions of the CPIC are:

- Asserts an interrupt to the SIU interrupt controller at a user programmable level.

- Generates a unique vector number for each interrupt source.

- Prioritizes the interrupts for which it is responsible.

- Highest priority interrupt source is programmable by the user.

- Programmable priority between SCCs.

- Two priority schemes for the SCCs.

# What is a Sub-Block Maskable Interrupt?

Definition

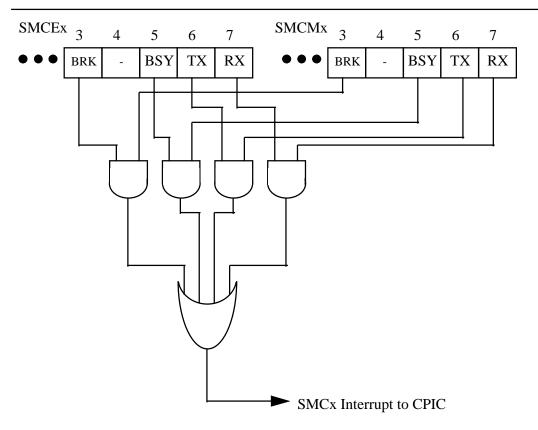

If an interrupt source is maskable within the particular sub-block of which it is a part, it is referred to as sub-block maskable.

Example, SMCx

# **Programming Model**

| CICI                                        | R - CPN             | M Inter        | rupt C  | Configu | ıration | Regis      | ster |            |      |           |           |              |         | P    | . 814       |

|---------------------------------------------|---------------------|----------------|---------|---------|---------|------------|------|------------|------|-----------|-----------|--------------|---------|------|-------------|

| 0                                           | 1                   | 2              | 3       | 4       | 5       | 6          | 7    | 8          | 9    | 10        | 11        | 12           | 13      | 14   | 15          |

|                                             |                     |                |         |         |         |            |      | SC         | CdP  | S         | СсР       | SC           | CbP     | SO   | CaP         |

| 16                                          | 17                  | 18             | 19      | 20      | 21      | 22         | 23   | 24         | 25   | 26        | 27        | 28           | 29      | 30   | 31          |

| IF                                          | RL0_IR              | L2             |         | HP      | 0_HP4   | 4          |      | IEN        |      |           | -         |              |         |      | SPS         |

|                                             |                     |                |         |         |         |            |      |            |      |           |           |              |         |      |             |

| CIPE                                        | R - CPN             | /I Inter       | rupt P  | ending  | Regis   | ster       |      |            |      |           |           |              |         | P    | . 816       |

| 0                                           | 1                   | 2              | 3       | 4       | 5       | 6          | 7    | 8          | 9    | 10        | 11        | 12           | 13      | 14   | 15          |

| PC15                                        | SCC1                | SCC2           | SCC3    | SCC4    | PC14    | Timer 1    | PC13 | PC12       | SDMA | IDMA<br>1 | IDMA<br>2 | -            | Timer 2 | R_TT | I2C         |

| 16                                          | 17                  | 18             | 19      | 20      | 21      | 22         | 23   | 24         | 25   | 26        | 27        | 28           | 29      | 30   | 31          |

|                                             | PC10                |                | Timer   | PC9     | PC8     | PC7        |      | Timer      | PC6  | SPI       | SMC1      | SMC2         | PC5     |      | -           |

| rcm                                         | IIICIO              | _              | 3       | rcs     | rco     | rc/        | _    | 4          | rco  | SFI       | SMC1      | /PIP         | 103     | 104  | -           |

|                                             |                     |                |         |         |         |            |      |            |      |           |           |              |         |      |             |

| CIM                                         | <b>R</b> - CP       | M Inte         | rrupt N | Mask I  | Registe | er         |      |            |      |           |           |              |         | P    | . 816       |

| 0                                           | 1                   | 2              | 3       | 4       | 5       | 6          | 7    | 8          | 9    | 10        | 11        | 12           | 13      | 14   | 15          |

| PC15                                        | SCC1                | SCC2           | SCC3    | SCC4    | PC14    | Timer<br>1 | PC13 | PC12       | SDMA | IDMA<br>1 | IDMA<br>2 | -            | Timer 2 | R_TT | I2C         |

| 16                                          | 17                  | 18             | 19      | 20      | 21      | 22         | 23   | 24         | 25   | 26        | 27        | 28           | 29      | 30   | 31          |

| PC11                                        | PC10                | -              | Timer 3 | PC9     | PC8     | PC7        | -    | Timer<br>4 | PC6  | SPI       | SMC1      | SMC2<br>/PIP | PC5     | PC4  | -           |

|                                             |                     |                | 3       |         |         |            |      | T          |      |           |           | /111         |         |      |             |

| CICD                                        | CD)                 | <b>4.1</b> . C |         | ъ .     |         |            |      |            |      |           |           |              |         | ъ    | 016         |

|                                             | <b>R -</b> CPM<br>1 |                |         | •       |         | 6          | 7    | 8          | 0    | 10        | 11        | 12           | 13      | 14   | . 816<br>15 |

|                                             | SCC1                |                |         |         | PC14    |            |      | PC12       |      |           | IDMA      | 12           | Timer   |      | I2C         |

| PCI                                         | SCCI                | SCC2           | SCC3    | SCC4    | PC14    | 1          | PC13 | PC12       | SDMA | 1         | 2         | -            | 2       | R_TT | 12C         |

| 16                                          | 17                  | 18             | 19      | 20      | 21      | 22         | 23   | 24         | 25   | 26        | 27        | 28           | 29      | 30   | 31          |

| PC11                                        | PC10                | -              | Timer 3 | PC9     | PC8     | PC7        | -    | Timer<br>4 | PC6  | SPI       | SMC1      | SMC2<br>/PIP | PC5     | PC4  | -           |

|                                             |                     |                |         |         |         |            |      |            |      |           |           |              |         |      |             |

| CIVR - CPM Interrupt Vector Register P. 814 |                     |                |         |         |         | . 814      |      |            |      |           |           |              |         |      |             |

| 0                                           | 1                   | 2              | 3       | 4       | 5       | 6          | 7    | 8          | 9    | 10        | 11        | 12           | 13      | 14   | 15          |

|                                             |                     | VN             |         |         |         |            |      |            |      | 0         |           |              |         |      | IACK        |

## How to Prioritize the SCCs (1 of 2)

Introduction

The SCCs must be prioritized relative to each other. The user controls the order of priority in the CICR, fields SCdP, SCcP, SCbP, and SCaP.

Priority Matrix

|      |      | Lowest |      |      | Highest | Priority |

|------|------|--------|------|------|---------|----------|

| SCC  | Code | SCdP   | SCcP | SCbP | SCaP    | CICR     |

| SCC1 | 00   |        |      |      |         |          |

| SCC2 | 01   |        |      |      |         |          |

| SCC3 | 10   |        |      |      |         |          |

| SCC4 | 11   |        |      |      |         |          |

Example

Problem: Set the priority so that SCC1 is highest, SCC3 is second hightest, SCC2 second lowest, and SCC4 the lowest.

|      |      | Lowest |      |      | Highest | Priority |

|------|------|--------|------|------|---------|----------|

| SCC  | Code | SCdP   | SCcP | SCbP | SCaP    | CICR     |

| SCC1 | 00   |        |      |      | 00      |          |

| SCC2 | 01   |        | 01   |      |         |          |

| SCC3 | 10   |        |      | 10   |         |          |

| SCC4 | 11   | 11     |      |      |         |          |

```

pdpr->CICR.SCaP = 0;

pdpr->CICR.SCbP = 2;

pdpr->CICR.SCcP = 1;

pdpr->CICR.SCdP = 3;

```

Exercise

Set the priority so that SCC2 is the highest priority, SCC3 is second highest, SCC4 is the second lowest, and SCC1 is the lowest.

```

pdpr->CICR.SCaP = _;

pdpr->CICR.SCbP = _;

pdpr->CICR.SCcP = _;

pdpr->CICR.SCdP = _;

```

Comment

SCaP, SCbP, SCcP, and SCdP should all have different numbers.

# **How to Prioritize the SCCs (2 of 2)**

Introduction

In addition to being prioritized relative to each other, the SCCs can be grouped together in the priority list or spread out.

Grouped Priority

| Priority | Interrupt Source |

|----------|------------------|

| Highest  | PC15             |

|          | SCCa             |

|          | SCCb             |

|          | SCCc             |

|          | SCCd             |

pdpr->CICR.SPS = 0;

•

Spread Priority

| Priority | Interrupt Source |

|----------|------------------|

| Highest  | PC15             |

|          | SCCa             |

pdpr->CICR.SPS = 1;

•

SCCb

•

SCCc

•

SCCd

•

# **How to Specify the Highest Priority Interrupt Source**

| Introduction | The user must specify which interrupt source is to be given top priority. This is done by writing the 5-bit interrupt vector number to CICR.HP0_HP4. A priority list is on p. 810. |  |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Example      | Problem: make the SDMA interrupt the highest priority.                                                                                                                             |  |  |  |

|              | pdpr->CICR.HP0_HP4 = 0x16;                                                                                                                                                         |  |  |  |

| Exercise     | Make PC15 the highest priority interrupt                                                                                                                                           |  |  |  |

pdpr->CICR.HP0\_HP4 = \_\_\_\_;

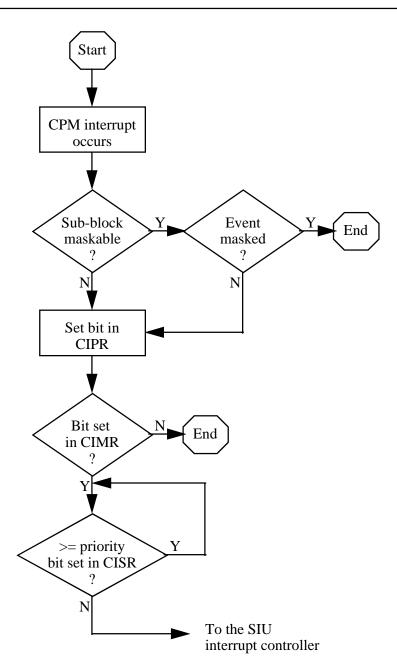

# **How the CPIC Processes an Interrupt Input**

Introduction

The CPIC receives an interrupt from one of its 29 sources, processes it, and, assuming no masking, asserts its programmed interrupt level to the SIU interrupt controller.

Flow Diagram of How the CPIC Processes an Interrupt

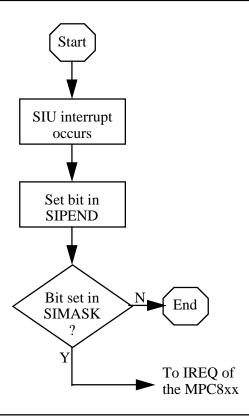

## **How the SIU Processes an Interrupt Input**

Introduction

The SIU receives an interrupt from one of 8 external sources or 1 of 8 internal sources and, assuming no masking, assertes the IREQ input to the MPC8xx.

Flow Diagram of How the SIU Processes an Interrupt

MPC8xx Action Following the assertion of IREQ, the MPC8xx completes the present instruction and program control goes to offset 0x500 in the exception vector table.

## How to Initialize a CPM for Interrupts

Introduction Here we describe the steps in initializing the CPM on the MPC860 for interrupts.

Assumptions - IMMR has been initialized previously. If not, the user must initialize it.

- Except for the above, reset conditions exist.

Action Here are the steps in initialization:

| Step | Action                                                                                                                                                                                                                                                  | Example                                                                |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| 1    | Initialize CPM Intrpt Config Reg, CICR SCdP: lowest priority SCC SCcP: 2nd lowest priority SCC SCbP: 2nd highest priority SCC SCaP: highest priority SCC IRLO_IRL2: CPM intrpt level HP0_HP4: highest priority intrpt source SPS: spread priority (814) | pdpr->CICR.HP0_HP4 = 0x16;<br>/* SDMA HIGHEST PRIORITY<br>INTERRUPT */ |

| 2    | Initialize Interrupt Mask Reg, CIMR  SCC1-4 PC4-15 TIMER1-4 IDMA1-2 SMC1-2 SDMA R-TT SPI I2C (817)                                                                                                                                                      | pdpr->CIMR.SCC2 = 1;<br>/* ENABLE SCC2 INTRPTS */                      |

| 3    | Initialize SI Edge/Level Reg, SIEL EDx:edge or level interrupt input WMx:exit low power mode where x is 0 to 7 (191)                                                                                                                                    | pdpr->SIEL.WM5 = 1;<br>/*WAKEUP 860 FOR LEVEL<br>5 INTERRUPT*/         |

| 4    | Initialize SI Mask Reg, SIMASK IRMx:enable external interrupt input LVMx:enable internal interrupt input where x is 0 to 7 (191)                                                                                                                        | pdpr->SIMASK.ASTRUCT.IRM6 = 1;<br>/*ENABLE IRQ6 INTERRUPTS */          |

| 5    | Enable CPM Interrupts (814)                                                                                                                                                                                                                             | pdpr->CICR.IEN = 1;<br>/* ENABLE CPM INTERRUPTS */                     |

| 6    | Initialize Enable Interrupts, EIE                                                                                                                                                                                                                       | asm (" mtspr 80,0");;<br>/* ENABLE INTERRUPTS */                       |

# **How to Handle a CPIC Interrupt (1 of 2)**

First Steps in Servicing CPM Interrupts • The first steps in servicing a CPM interrupt:

| 1 | Read the interrupt code in the SI vector register, SIVEC, and go to service routine for that code. (192)                                                              | if (pdpr->SIVEC.IC == 0x38)<br>irq7esr();<br>/* IF IRQ7, GO TO IRQ7ESR */                                                    |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| 2 | Clear the service bit in the SI Pending<br>Register, SIPEND (191)                                                                                                     | pdpr->SIPEND = 1<<(31-6);<br>/* CLEAR IRQ3 PENDING BIT*/                                                                     |

| 3 | Required only if service routine is to be recoverable and lower priority interrupts are to be masked.  Save the SI mask reg, SIMASK Mask lower interrupt levels (191) | sptr++ = pdpr->SIMASK.ASINT;<br>/* STACK SIMASK REG */<br>pdpr->SIMASK.ASINT &=<br>0xF0000000;<br>/* MASK INTRPTS 2-7 */     |

| 4 | Required only if service routine is to be recoverable.  Save SRR0 & SRR1 on the stack Enable interrupts                                                               | asm (" mfspr r9,26");<br>asm (" stwu r9,-8(r1)");<br>asm (" mfspr r9,27");<br>asm (" stw r9,4(r1)");<br>asm (" mtspr 80,0"); |

| 5 | Request the vector number via the CPM<br>Interrupt Vector Reg, CIVR (819)                                                                                             | pdpr->CIVR.IACK = 1;<br>/* REQUEST VECTOR NUMBER*/                                                                           |

| 6 | Read the interrupt vector in the CPM interrupt vector reg, CIVR, and go to service routine for that vector number.  (819)                                             | if (pdpr->CIVR.VN == 0x10<br>i2cesr();<br>/* I2C VEC NUM, GO TO I2CESR*/                                                     |

| 7 | If this is a submodule maskable event source, read the event register.                                                                                                | er = pdpr->SCCE2;<br>/* GET EVENT REGISTER */                                                                                |

| 8 | If this is a submodule maskable event source, clear the known events.                                                                                                 | pdpr->SCCE2 = er;<br>/* CLEAR EVENT REGISTER */                                                                              |

# **How to Handle a CPIC Interrupt (2 of 2)**

Last Steps in Servicing CPM Interrupts • The last steps in servicing a CPM interrupt:

| 1 | Clear the bit in the in-service reg, CISR (818)                                                                                   | pdpr->CISR = 1<<(31-6);<br>/* CLEAR TIMER 1 BIT */                                                                                                   |

|---|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | Required only if service routine was made recoverable.  Disable interrupts Restore SRR0 & SRR1 on the stack                       | asm (" mtspr 82,0");<br>asm (" lwz r9,4(r1)");<br>asm (" mtspr 27,r9");<br>asm (" lwz r9,0(r1)");<br>asm (" addi r1,r1,8;")<br>asm (" mtspr 26,r9"); |

| 3 | Required only if service routine was made recoverable and lower priority interrupts were masked.  Restore the SI mask reg, SIMASK | pdpr->SIMASK.ASINT =sptr;<br>/* RESTORE SIMASK REG */                                                                                                |

FREESCALE

Freescale Technical Training - MPC860 Course Phoenix, Arizona

Title: pc8.c

Handling an 860 CPM Interrupt

<u>Creation Date:</u> Jan. 10, 1996 <u>From:</u> MC68360 Course

<u>Author:</u> Bob Bratt

#### Description:

The results of this routine are:

- 1. Initializes the exception vector area with a service routine.

- 2. The service routine jumps to a function based on the interrupt code.

- 3. The function increments a counter each time an external interrupt level 1 occurs.

#### Assumptions:

- 1. IMMR has been previously initialized.

- 2. Except for 1, reset conditions exist.

#### Objective:

If the program executes properly, the LED counter is equal to the number of times that the black button on the UDLP1 has been pressed.

#### Equipment:

MPC860ADS board and UDLP1

<u>UDLP1 Switch Settings:</u> N/A

Connections: MPC860ADS board and a UDLP1 are connected through P13.

<u> Updates:</u>

#### pc8.c (1 of 2)

```

/* Equipment : 860ADS Evaluation Board and

* /

UDLP1 Universal Development Lab Board

/*

Pins 2 and 3 of JP2 must be jumpered

* /

/* Connected: P10-C15 of ADS to J4-11 of UDLP1

* /

/* (PC8.C)

/* DUAL PORT RAM EQUATES */

#include "mpc860.h"

main()

/* EXCEPTION SERVICE RTN */

void intbrn();

/* SOURCE & DEST POINTERS*/

/* INTERRUPT LEVEL */

int *ptrs,*ptrd;

char intlvl = 4;

pdpr = (struct dprbase *) (getimmr() & 0xFFFF0000);

/* INIT PNTR TO DPRBASE */

ptrs = (int *) intbrn;

/* INIT SOURCE POINTER */

ptrd = (int *)(getevt() + 0x500); /* INIT DEST POINTER

* /

* /

/* MOVE ESR TO EVT

*ptrd++ = *ptrs;

/* MOVE UNTIL

"ptra++ = "ptrs, /* MOVE UNITE

while (*ptrs++ != 0x4c000064); /* RFI INTRUCTION

pdpr->CICR.IRL0_IRL2 = (unsigned) (intlvl);

/* CPM INTERRUPTS LEVEL 4*/

pdpr->CICR.HP0_HP4 = 0x1F; /* NO INT PRIORITY CHANGE*/

pdpr->PDDAT = 0; /* CLEAR PORT D DATA REG */

pdpr->PDDIR = 0xff; /* MAKE PORT D8-15 OUTPUT*/

pdpr->PDDIR = 0x80; /* CONFIG PC8 INTRPT EDGE*/

pdpr->CIMR.PC8 = 1; /* ENABLE PORT C,8 INTRPT*/

pdpr->SIMASK.ASTRUCT.LVM4 = 1; /* ENABLE IRQ4 INTERRUPTS*/

pdpr->CICR.IEN = 1; /* ENABLE CPM INTERRUPTS */

asm(" mtspr 80,0"); /* ENABLE INTERRUPTS */

while (1--1):

while (1==1);

}

#pragma interrupt intbrn

void intbrn()

void cpmesr();

case 0x24: asm (" mfspr r9,8"); /* PUSH LR ONTO STACK */

asm (" stwu r9,-4(r1)");

asm (" bla cpmesr"); /* PROCESS IRQ1 CODE

asm (" lwz r9,0(r1)"); /* PULL LR FROM STACK */

asm (" addi r1,r1,4"); /* RESTORE STACK POINTR*/

asm (" mtspr 8,r9");

break;

default:;

CPM Interrupt Controller

```

#### pc8.c (2 of 2)

```

asm (" lwz r9,0(r1)"); /* PULL GPR9 FROM STACK */ asm (" addi r1,r1,4"); /* RESTORE STACK POINTER */

void cpmesr()

asm (" mfspr r9,26"); /* PUSH SRRO ONTO STACK */

asm (" stwu r9,-8(r1)");

asm (" mfspr r9,27"); /* PUSH SRR1 ONTO STACK */

asm (" stw r9,4(r1)");

asm (" mtspr 80,0");

/* ENABLE INTERRUPTS */

/* PROCESS VECTOR NUMBER */

switch (v1)

/* PC8 VECTOR NUMBER

case 0xA:

* /

pdpr->PDDAT += 1; /* INCREMENT DISPLAY */

pdpr->CISR = 1<<(31-21); /* CLEAR IN-SRVCE BIT*/

break;

default:;

asm (" mtspr 82,0");

asm (" lwz r9,4(r1)");

/* MAKE NON-RECOVERABLE

* /

/* PULL SRR1 FROM STACK */

asm (" mtspr 27,r9");

asm (" lwz r9,0(r1)"); /* PULL SRRO FROM STACK */

asm (" addi r1,r1,8");

asm (" mtspr 26,r9");

pdpr->SIMASK.ASINT = buffer[--sp]; /* RESTORE SIU MASK REG */

getimmr()

asm(" mfspr 3,638");

/* GET EVT LOCATION

getevt()

if ((getmsr() \& 0x40) == 0) /* IF MSR.IP IS 0

/* THEN EVT IS IN LOW MEM*/

return (0);

/* ELSE

else

/* EVT IS IN HIGH MEM

return (0xFFF00000);

* /

/* GET MACHINE STATE REG VALUE */

getmsr()

asm(" mfmsr 3"); /* LOAD MACHINE STATE REG TO r3 */

```