## AN11564

# PN7120 Antenna Design and Matching Guide Rev. 1.1 — 18 April 2016

**Application note COMPANY PUBLIC**

#### **Document information**

| Info                                                                                               | Content                                                                                                                                                                                    |  |  |

|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Keywords                                                                                           | PN7120, NFC, Antenna Design, Antenna matching/tuning                                                                                                                                       |  |  |

| Abstract                                                                                           | This application note is intended to provide some guidelines regarding the way to design an NFC antenna for the PN7120 chip.                                                               |  |  |

| It also explains how to determine the tuning/matching network between this antenna and the PN7120. |                                                                                                                                                                                            |  |  |

|                                                                                                    | Standalone antenna performances evaluation and final RF system validation (PN7120 + tuning/matching network + NFC antenna within its final environment) are also covered by this document. |  |  |

#### **PN7120** Antenna Design and Matching Guide

#### **Revision history**

| Rev | Date     | Description                                                                                           |  |  |

|-----|----------|-------------------------------------------------------------------------------------------------------|--|--|

| 1.1 | 20160418 | Added description of CLIF_ANA_TX_SHAPE_CONTROL_REG register  Continue 0.3 Licenses statement undeted. |  |  |

|     |          | Section: 9.3: License statement updated                                                               |  |  |

| 1.0 | 20150408 | First official release                                                                                |  |  |

#### **Contact information**

For additional information, please visit: <a href="http://www.nxp.com">http://www.nxp.com</a>

For sales office addresses, please send an email to: <a href="mailto:salesaddresses@nxp.com">salesaddresses@nxp.com</a>

#### **PN7120 Antenna Design and Matching Guide**

#### 1. Introduction

The PN7120 is a highly integrated NFC transceiver IC for contactless communication at 13.56 MHz. This transceiver IC utilizes an outstanding modulation and demodulation concept completely integrated for different kinds of contactless communication methods and protocols at 13.56 MHz.

It can operate both in reader/poller mode and in card/listener mode.

The PN7120 is intended to be connected to an external coil antenna through a specific matching/tuning network.

The purpose of this document is first to provide some guidelines regarding the design of an NFC antenna intended to be connected to the PN7120.

It then depicts a measurement method in order to evaluate the performances of the antenna prior to connecting it to the NXP NFC chip.

The next chapter explains how to determine the tuning/matching network to be placed between a given antenna and the PN7120 (based on the antenna electrical equivalent circuit)

Then, an RF performance validation procedure is proposed.

Finally an example of PN7120 antenna and tuning design is given as reference.

#### **PN7120 Antenna Design and Matching Guide**

#### 2. Antenna Design

Some of the design rules are very common for NXP NFC designs, i.e. they do neither specifically depend on the used standard (ISO, NFC or EMVCo) nor depend on the NXP Reader IC but rather on physical or technical basics.

#### 2.1 Standard antenna design

The PN7120 can be connected to a standard antenna commonly used on the market today. Those antennas are typically constituted by a spiral loop (*single loop antenna*). The outline dimensions, the number of turns, the copper track thickness, width and spacing define the antenna characteristics.

#### 2.2 Shielding and environment impact

The PN7120 and the associated NFC antenna are intended to be integrated into an embedded device.

Those devices are composed of metallic parts such as the battery, the PCB, the electronic components and even sometimes the chassis.

If metal is placed close to the NFC antenna the alternating magnetic field generates some eddy currents in the metal. These eddy currents create a magnetic field in opposite direction; it absorbs power, and leads to detuning of the antenna due to a decreased inductance and quality factor. Therefore, it is necessary to shield the antenna with ferrite for proper operation in close metallic environment.

Adding a ferrite sheet allows to shield the antenna against the influence of metal.

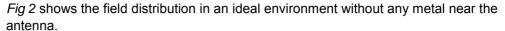

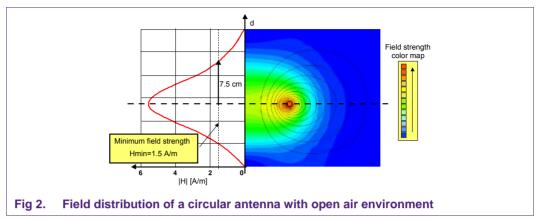

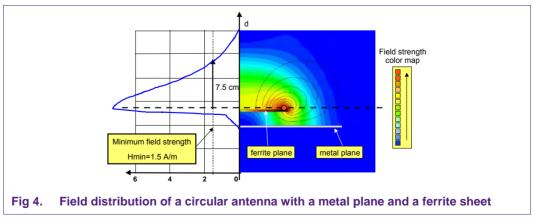

The following figures are intended to highlight this phenomenon based on antenna field distribution simulation results. In order to simplify the simulation, the below results are based on a circular antenna with a radius of 7.5 cm with 1 turn and a copper wire of 1mm thickness. The right part shows the field distribution and the left part shows the magnitude of the field strength H over the distance d. The minimal field strength of  $H_{MIN} = 1.5 \text{ A/m}$  defined by ISO/IEC 14443 is marked with doted vertical line.

#### PN7120 Antenna Design and Matching Guide

Fig 3 shows the field distribution of the same antenna but with a metal plane near to it. The magnitude of the field strength has significantly decreased compared to the open air case which leads to a decreased operating distance.

Fig 4 shows the effect of adding a ferrite plane ( $\mu_R$ =40) between the metal plane and the antenna coil itself. The field distribution is still modified but the operating distance recovers its original open air level.

#### PN7120 Antenna Design and Matching Guide

The simulation shows that the use of a ferrite reduces the generated eddy currents in a metal plane. The ferrite sheet changes the antenna environment characteristics, which results in a fixed detuning of the antenna itself. This shielding will significantly impact the antenna electrical equivalent model so it is key that when doing PN7120 tuning/matching network calculation, the antenna model is measured with the ferrite already in place (when applicable).

#### 2.2.1 Ferrite shielding recommendation

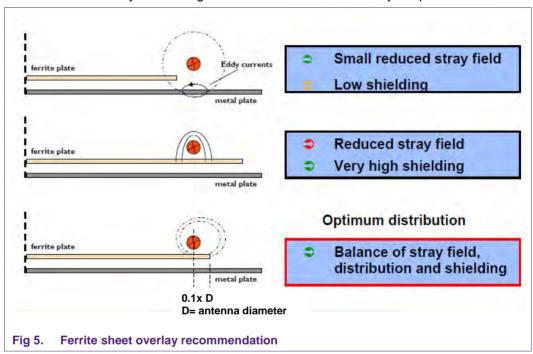

In order to reach a proper shielding, the ferrite sheet must at least fully cover the antenna surface. It is even needed to have an overlay but not too high because otherwise it will tend to reduce the stray field strength. This trade-off is illustrated by the picture below:

The Ferrite quality is also a key parameter which needs to be taken into account to assess the effectiveness of the shielding. A high relative permeability is recommended because it allows achieving a good shielding with a lower thickness. The material has to be specified for a high magnetic permeability in the frequency range that is involved in NFC operation, i.e. 13.56MHz. The relative magnetic permeability of a material is made of two parts:  $\mu$ r' is the real part of relative permeability and  $\mu$ r'' is the imaginary part.  $\mu$ r'' is reflecting the magnetic losses in the material.

Recommended values are:

$\mu$ r' > 40 at 13.56MHz and  $\mu$ r'' as low as possible: ratio  $\mu$ r''/ $\mu$ r' < 0.1 at 13.56MHz.

Please note that the level of shielding not only depends on the material used but also on the thickness of the ferrite sheet. For a given permeability, the thickest sheet provides the strongest shielding.

#### **PN7120 Antenna Design and Matching Guide**

### 3. PN7120 Antenna matching

#### 3.1 Antenna matching circuit

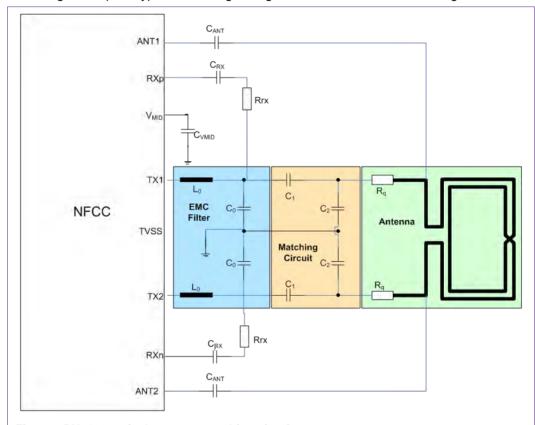

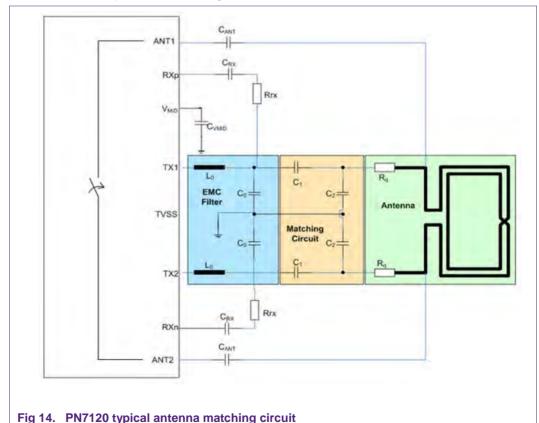

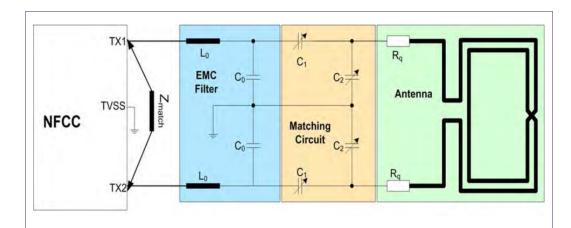

On this chapter we will show the different blocks in order to do the antenna matching. Below diagram depicts typical matching/tuning circuit related to PN7120 design.

Fig 6. PN7120 typical antenna matching circuit

The process to matching the Antenna to the NFCC is composed of a matching for reader mode and a matching for card mode. The NFCC will select the reader mode matching when it is on reader mode and the card mode matching when the device is on card mode.

The matching procedure can be summarized in 5 steps. :

- 1) Determine antenna coil characteristics

- 2) Determine EMC filter cutoff frequency

- Determine the matching circuit between the antenna and the EMC filter for Reader Mode.

- 4) Adapt the matching for Card Mode.

- 5) Determine the Reception block

#### PN7120 Antenna Design and Matching Guide

#### 3.2 Step 1: Antenna model measurement

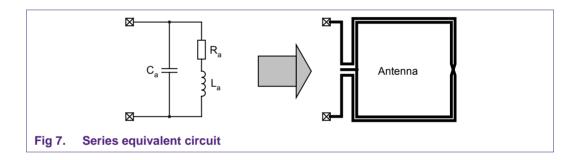

Based on the antenna physical characteristics, its electrical equivalent model can be measured and computed.

For this, the antenna has to be connected to an impedance analyzer or a network analyzer to measure the series equivalent components.

Please note that the antenna equivalent circuit must be determined under the final environmental conditions especially when the antenna will be operated in metal environment or when a ferrite sheet shall be used for shielding.

The target of this modeling step is to get the L, R, C equivalent of the antenna.

Recommended values:

$L_a = 0.3...3\mu H$

$C_a = 3...30pF$

$R_a = 0.1...2\Omega$

fra (self-resonance frequency of the antenna) = 25MHz or above

The antenna parasitic capacitance Ca should be kept low to achieve a self-resonance frequency > 25 MHz as the relation linking those 2 parameters is:

$$C_a = \frac{1}{\left(2 \cdot \pi \cdot f_{ra}\right)^2 L_a}$$

In order to get these antenna electrical equivalent parameters, 2 methods are proposed below depending on the available equipment:

#### PN7120 Antenna Design and Matching Guide

#### 3.2.1 Measurement method with impedance analyzer:

Some impedance analyzers like Agilent 4294A or 4395A can determine directly the series or parallel equivalent circuit by measuring the magnitude and the phase of the impedance of the connected antenna.

The antenna has to be at the final mounting position to consider all parasitic effects like metal influence on quality factor, inductance and additional capacitance.

The antenna needs to be connected to the analyzer by using an appropriate test fixture that does not influence any antenna parameters.

The analyzer has to be calibrated (open, short and load compensation at the calibration plane) and the test fixture needs to be compensated (open, short compensation at the connection points) before each measurement.

Settings: |Z|,  $\Theta$

Start frequency: 1 MHz

Stop frequency: above self-resonance frequency of the antenna (point where antenna impedance is real: pure resistance)

#### Advantages:

· Fast and simple method

#### Disadvantages:

- High-end equipment required

- Low accuracy of the measurement which especially results from the loss resistance for high quality factor coils (Q > 60).

#### 3.2.2 Measurement method with any network analyzer

Alternatively, a network analyzer without any equivalent circuit functionality can be used in combination with some calculation to determine the antenna electrical equivalent.

The antenna needs to be connected to the analyzer by using an appropriate test fixture that does not influence the antenna parameters.

The analyzer has to be calibrated (open, short and load compensation at the calibration plane) and the test fixture needs to be compensated (open, short compensation at the connection points) before each measurement.

Settings: S11

Chart: Smith Z

Start frequency: 1 MHz

Stop frequency: above self-resonance frequency of the antenna

#### PN7120 Antenna Design and Matching Guide

4 parameters must be extracted from the above measurement in order to get the serial equivalent circuit of the antenna:

All 4 parameters are due to the geometry of the antenna, Rs is mainly defined by the thickness of the copper wire, Rp is mainly defined by the skin effect and can be changed by thickness and distance between the turns, and La of the antenna is a geometrical value.

Basically, increasing the number of turns increases the Q factor but decreases the effective antenna area and reduces its field strength.

R<sub>s</sub> Equivalent resistance at f = 1MHz

La Equivalent inductance at f = 1MHz

Rp Equivalent resistance at the self-resonance frequency

fra Self-resonance frequency of the antenna

First the antenna capacitance Ca can be calculated with:

$$C_a = \frac{1}{\left(2 \cdot \pi \cdot f_{ra}\right)^2 L_a}$$

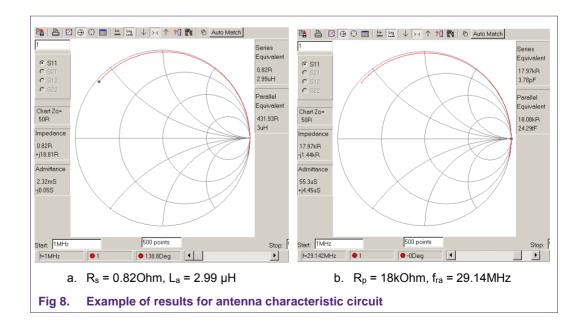

Fig 8 illustrates the antenna characteristic circuit determination based on the Smith chart:

#### PN7120 Antenna Design and Matching Guide

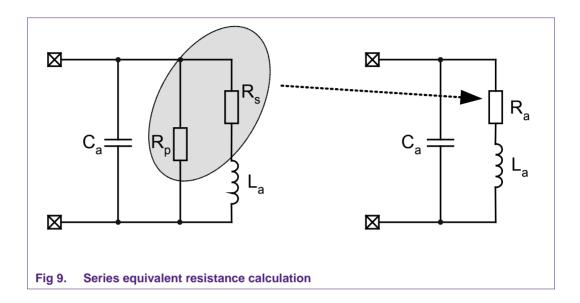

The series equivalent resistance Ra of the antenna at the operating frequency  $f_{op} = 13.56MHz$  can be calculated out of the characteristic circuit.

$$R_{p}(13.56MHz) = \frac{R_{p}(fra)}{\sqrt{\frac{13.56}{fra}}}$$

$$R_{a} = R_{s} + \frac{(2 \cdot \pi \cdot f_{op} \cdot L_{a})^{2}}{R_{p}(13.56MHz)}$$

The parallel resistance  $R_p(fra)$  obtained by measurements has to be calculated to the parallel equivalent value at 13.56MHz. This is accomplished in first equation.

R<sub>a</sub> in second equation is then calculated by using R<sub>p</sub>(13.56Mhz).

Please note that this equivalent resistor value is then only valid at 13.56MHz.

#### 3.2.3 Optional Quality factor adjustment

The Q factor of the antenna depends on its inductance value and serie impedance (see equation below). It measures the selectivity of the antenna. If the Q factor is too high the antenna can be too selective which can result in too narrow bandwidth of the resonance and can also impact the shaping of the NFC signal. This is why we recommend the Q factor of the antenna not to exceed 35.

In case the measured antenna quality factor is above this value,  $R_{\rm Q}$  resistors in series can be used to damp it.

The following calculation method can then be used to determine the damping resistor value.

#### PN7120 Antenna Design and Matching Guide

The quality factor of the antenna is calculated with

$$Q_a = \frac{\omega \cdot L_a}{R_a}$$

The value of  $R_Q$  needed to reach 35 (resistors in series at each side of the antenna) is calculated by

$$R_{Q} = 0.5 \cdot \left( \frac{\omega \cdot L_{a}}{35} - R_{a} \right)$$

#### Practical consideration:

In an embedded environment where ferrite shielding is required, a quality factor above 35 is very unlikely. In this case, when Q is lower than 35, damping resistor can be skipped.

A correct range for the Q-factor is 20-35.

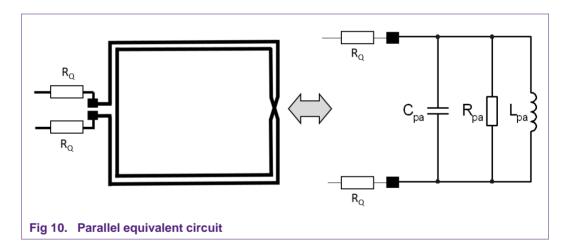

#### 3.2.4 Determination of the parallel equivalent circuit:

The parallel equivalent circuit of the antenna together with the optionally added external damping resistors  $R_Q$  has to be calculated as explained below:

The following formula applies

$$\begin{split} L_{pa} &\triangleq L_a \\ C_{pa} &\triangleq C_a \\ R_{pa} &\triangleq \frac{(\omega \cdot L_a)^2}{R_a + 2 \cdot R_O} \end{split}$$

#### PN7120 Antenna Design and Matching Guide

#### 3.3 Step 2: EMC filter design (L<sub>0</sub> and C<sub>0</sub> definition)

The EMC filter circuit for the PN7120 fulfills two functions: the filtering of the signal and impedance transformation block.

The main properties of the impedance transformation are:

- Decreasing rise time after a modulation phase (poll mode)

- Increasing the receiving bandwidth

L<sub>0</sub> and C<sub>0</sub> value definition:

$$L_0 = 270 nH - 1 \mu H$$

Filter resonance frequency f<sub>r0</sub> = 15.5MHz ...17MHz, => C<sub>0</sub>

$$C_0 = \frac{1}{(2 \cdot \pi \cdot f_{r0})^2 L_0}$$

The EMC filter resonance frequency  $f_{r0}$  has to be higher than the upper sideband frequency determined by the highest data rate (848 kHz sub carrier) in the system.

#### Example:

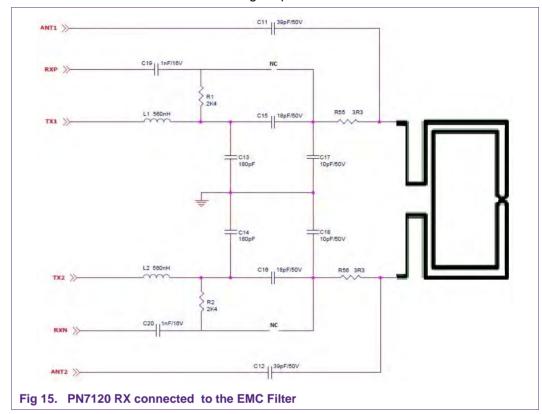

A recommended value of 560nH for L<sub>0</sub> is chosen to calculate the capacitance C<sub>0</sub>.

$L_0 = 560 nH$

$f_{r0} = 15.5MHz$

$C_0 = 188.3pF \rightarrow chosen: 180pF$

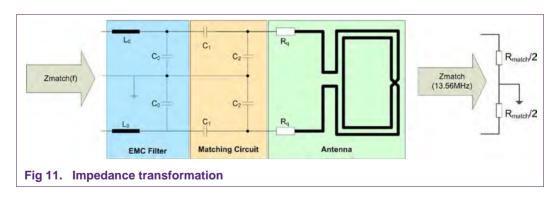

The EMC filter and the matching network must transform the antenna impedance  $Z_{\text{match}}(f)$  to the required TX matching resistance  $R_{\text{match}}$  at the operating frequency of f =13.56 MHz.

The measured  $Z_{\text{match}}(f)$  can be modeled in an equivalent circuit loading each TX pin with  $R_{\text{match}}/2$  at 13.56MHz.

AN11564 **NXP Semiconductors**

#### PN7120 Antenna Design and Matching Guide

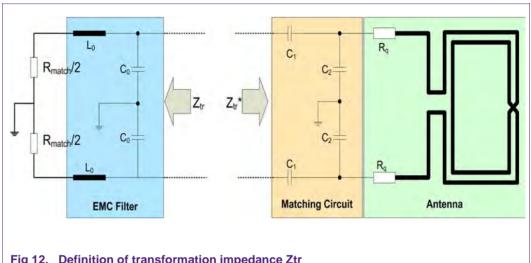

By cutting the circuitry after the EMC filter and by using the precondition R<sub>match</sub>/2, the remaining components C<sub>1</sub> and C<sub>2</sub> can be calculated.

Please note that R<sub>match</sub>/2 does not correspond to the driver output impedance

Fig 12. Definition of transformation impedance Ztr

$$Z_{tr} = R_{tr} + jX_{tr}$$

$$Z_{tr}^{*} = R_{tr} - jX_{tr}$$

$$R_{tr} = \frac{R_{match}}{\left(1 - \omega^2 \cdot L_0 \cdot C_0\right)^2 + \left(\omega \cdot \frac{R_{match}}{2} \cdot C_0\right)^2}$$

$$X_{tr} = 2 \cdot \omega \cdot \frac{L_0 \cdot \left(1 - \omega^2 \cdot L_0 \cdot C_0\right) - \frac{R_{match}^2}{4} \cdot C_0}{\left(1 - \omega^2 \cdot L_0 \cdot C_0\right)^2 + \left(\omega \cdot \frac{R_{match}}{2} \cdot C_0\right)^2}$$

14 of 63

#### PN7120 Antenna Design and Matching Guide

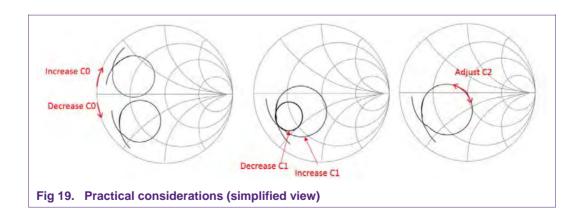

#### 3.4 Step 3: Reader mode matching (C<sub>1</sub> and C<sub>2</sub> definition)

The capacitors  $C_1$  and  $C_2$  are used in combination with the EMC filter to match the antenna to 13.56MHz and at the impedance value  $R_{\text{match}}$ .

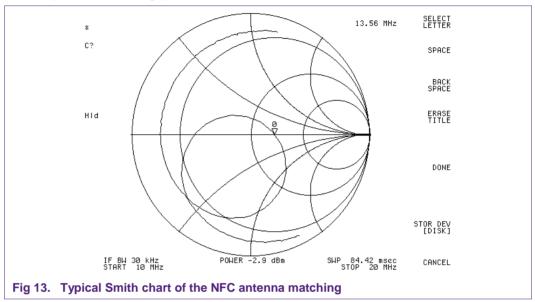

Typical Smith card (S11 measured between TX1/TX2 pins) is shown on *Fig 13* (usually called "capacitive matching").

For the PN7120 the recommendations are given in Table 1.

Table 1. EMC Filter (typical values) and matching impedance target

| Component      | Value | Remarks                                              |

|----------------|-------|------------------------------------------------------|

| L <sub>0</sub> | 560nH | Can be adjusted according to antenna characteristics |

| C <sub>0</sub> | 180pF | Can be adjusted according to antenna characteristics |

| Zmatch         | 70Ω   | Impedance target READER mode adjusted with C1 and C2 |

The reason for the higher cut-off frequency of the EMC filter is a higher stability with close coupling devices in poll mode: less impact of detuning effect on power consumption increase.

The following formulas are then used to calculate the series (C<sub>1</sub>) and parallel (C<sub>2</sub>) matching capacitances:

$$C_{1} \approx \frac{1}{\omega \cdot \left(\sqrt{\frac{R_{tr} \cdot R_{pa}}{4} + \frac{X_{tr}}{2}}\right)} \qquad C_{2} \approx \frac{1}{\omega^{2} \cdot \frac{L_{pa}}{2}} - \frac{1}{\omega \cdot \sqrt{\frac{R_{tr} \cdot R_{pa}}{4}}} - 2 \cdot C_{pa}$$

#### PN7120 Antenna Design and Matching Guide

Where  $L_{pa}$ ,  $C_{pa}$  and  $R_{pa}$  come from the measured antenna parallel electrical equivalent (see step 1) and  $R_{tr}$  and  $X_{tr}$  are coming from the EMC filter components value definition (see step 2).

The matching circuit elements  $C_1$  and  $C_2$  must be chosen to get the required match resistance  $R_{match}$  (typically  $70\Omega$  in READER mode) at 13.56MHz at the PN7120 TX pins.

#### 3.5 Step 4: Card mode tuning (C<sub>2</sub>/C<sub>ANT</sub> ratio definition)

In the PN7120 implementation the TX configurations for the READER mode and for the CARD mode are slightly different. In the previous step the capacitor  $C_2$  was correct set to achieve the 13.56MHz resonance frequency for reader mode, let's call this value  $C_2$  reader mode. On Card mode our target is a higher frequency such as 16 MHz resonance frequency. To achieve this value the capacitor  $C_2$  card mode will have a lower value compared to  $C_2$  reader mode from the previous step.

The difference between C<sub>2</sub> reader mode - C<sub>2</sub> card mode = C<sub>shift</sub> = C<sub>ANT</sub>/2

But, if we need 2 different values of  $C_2$  to work on reader mode and card mode, which value should we chose? Basically, both! In READER mode  $C_{ANT}$  capacitors (see Fig 15) are shorted internally (with a  $10\Omega$  resistive switch) while in CARD mode the  $C_{ANT}$  are not shorted. The  $C_{ANT}$  capacitors when shorted come in parallel to  $C_2$  capacitors and then contribute to the impedance matching in READER mode.

1 19 14. FIA7 120 typical antenna matching circuit

The way to reach the correct C<sub>2 card mode</sub> is given in the next paragraph.

#### **PN7120 Antenna Design and Matching Guide**

The resonance formula ( $f_{\text{res}}$ ,  $C_{\text{res}}$  below) are used to calculate the capacitor value to reach the 13.56MHz resonance frequency in Reader mode and the targeted frequency range (16MHz) in CARD mode. The inductance of the antenna has already been measured in step 1.

$$f_{res} = \frac{1}{2 \cdot \pi \sqrt{L \cdot C}} \qquad C_{fres} = \frac{1}{\frac{(2 \cdot \pi \cdot f_{res})^2}{L}}$$

Based on this parameter and on the targeted listen mode frequency, the ratio between  $C_2$  reader mode and  $C_{ANT}$  can be defined.

#### Example:

Let's take an antenna with inductance value L=3.09uH and a chosen CARD mode frequency at 16MHz:

C<sub>13.56MHz</sub>=44.5pF (reader mode)

C<sub>16MHz</sub>=32pF (card mode)

$C_{13.56MHz} - C_{16MHz} = 12.5pF$

$C_{\text{shift}} = 12.5 pF$

This means that the total parallel capacitance for the READER mode needs to be 12.5pF higher than in CARD mode.

With this information and with the  $C_2$  ( $C_2$  reader mode) value calculated during step 3,  $C_2$  and  $C_{ANT}$  can be calculated.

C<sub>2</sub> reader mode = C<sub>2</sub>card mode + C<sub>ANT</sub>

$C_{ANT}$  = 2.  $C_{shift}$ , because two  $C_{2ANT}$  capacitors in series are used in the matching network.

$C_{\text{shift}} = 12.5 pF$

C<sub>ANT</sub>=25pF → 27pF normalized value

$C_2$  card mode =  $C_2$  reader mode -  $C_{ANT}$  = 47pF - 27pF = 20pF

Once C<sub>2</sub>/C<sub>ANT</sub> split is defined it must be implemented on a real device and some fine tuning must be done with network analyzer.

Based on the value calculated, the matching impedance  $Z_{match} = R_{match} + jX_{match}$  must be measured with an impedance or network analyzer. The TX1 and TX2 pins of the PN7120 are the probing points for the network/impedance analyzer to measure  $Z_{match}$ .

#### PN7120 Antenna Design and Matching Guide

#### 3.6 Step 5: Rx path tuning (R<sub>rx</sub> & C<sub>Rx</sub> definition)

Two configurations are possible for the Rx path:

- 1- The first one consists in connecting Rx path on the EMC filter

- 2- The second one consists in connecting Rx path on the antenna.

The purpose of the  $C_{rx}$  capacitors is to provide an AC coupling of the Rx signal. A value of 1nF can generally be used.

The purpose of the  $R_{rx}$  resistor is to provide a voltage drop so that the Rx input is not saturated.

The first step of the Rx path tuning process is to define which Rx path connection is the best. For small antenna or antenna setup in a stringent environment (e.g. metal surrounding, bad isolating ferrite ...) a direct connection to antenna is preferred. For large antenna or optimized setup (e.g. antenna in back cover) the connection can be preferably done on the EMC filter.

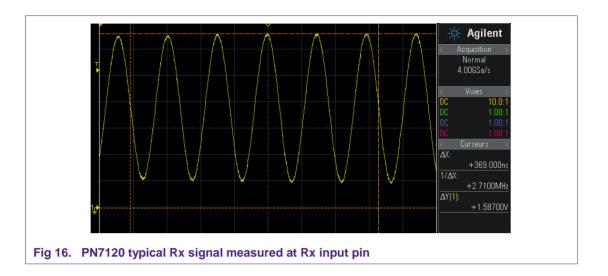

Once the RX connection point has been chosen according to the setup,  $R_{rx}$  value must be carefully adjusted. The resistor value on the Rx path must be chosen to guarantee that the <u>peak voltage</u> at Rxn and Rxp stays below 1.65Vpk. As illustrated below the 13.56MHz can be observed on top of a DC offset of 900mV.

#### **PN7120 Antenna Design and Matching Guide**

*Note:* The peak value depends on the AGC Vref [Bit (1:0)] setting forced by the register CLIF\_ANA\_AGC\_REG. This value was defined to reach the best performances of the Rx sensitivity. Changing the default value is not recommended.

Table 2. CLIF\_ANA\_AGC\_REG and expected maximum Rx voltage

| setting | Peak Value |

|---------|------------|

| 0       | 1.15Vpk    |

| 1       | 1.45Vpk    |

| 2       | 1.55Vpk    |

| 3       | 1.65Vpk    |

#### PN7120 Antenna Design and Matching Guide

#### 4. Matching verification

The antenna has first to be matched to the PN7120 as described in the previous chapter §3 PN7120 Antenna matching.

Then the steps described below can be followed to verify the antenna matching.

Due to the fact that the PN7120 IC must NOT be powered ON during this verification, the IC pins are not configured properly. Therefore a 10 ohms resistor must be connected between ANT 1 and ANT2 pin when checking the antenna matching for the READER mode.

#### 4.1 Step 1: verification of the Reader/Poller mode matching.

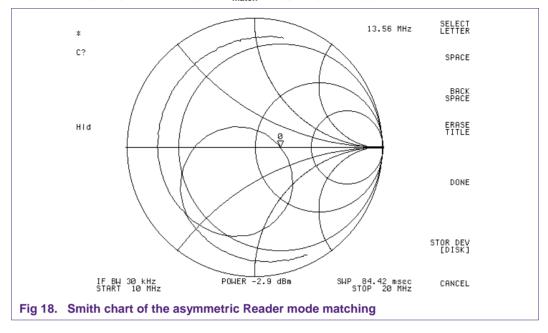

The load impedance is measured with a network analyzer by contacting a test fixture across the TX1 and TX2 pins of the PN7120.

Both matching and measurement of the NFC antenna have to be performed at the final mounting position to consider all parasitic effects like metal which influences the quality factor, the inductance and parasitic capacitance.

This circuit only covers the Tx part (Rx part must be left connected for the measurement)

Fig 17. Measurement of the matching impedance

In order to simulate the Reader/Writer behavior of the PN7120, the CANT capacitors need to be shortcut with a 10 Ohm resistor. By shortening both  $C_{\text{ANT}}$  with a 10Ohm resistance, they came in parallel to C2 capacitors which causes a frequency down shift.

Connecting a 10 ohms resistor across PN7120 ANT1 and ANT2 pins is mandatory before performing this measurement.

#### **PN7120 Antenna Design and Matching Guide**

An asymmetric impedance curve shall be seen on the network analyzer:

#### - Reader/Writer mode → R<sub>match</sub>= 700hms at 13.56Mhz

If the measurement is not the matching expected by the theoretical matching some adjustments can be necessary.

#### **Practical considerations:**

The value of C1 changes the magnitude of the matching impedance. After changing C1 the imaginary part of  $Z_{\text{match}}$  must be compensated by adjusting C2 as well.

C2 changes mainly the imaginary part of Z<sub>match</sub>.

Remark: Do not forget to remove the 10 ohms resistor after this measurement.

#### PN7120 Antenna Design and Matching Guide

#### 4.2 Step 2: verification of the CARD/listen mode frequency

Similarly to the READER mode verification, measure the load impedance by connecting the probe tips of the network analyzer on the Tx output pins of the IC.

Remark: Do not forget to remove the 10 ohms resistor for this measurement.

The matched frequency should be in the following range:

Card mode frequency → 14.5 – 16 MHz

If it is not, the balance between CANT and C2 capacitors must be fine-tuned as described in the previous paragraphs.

#### 4.3 Components characteristics

Table 3. Components characteristics

| Component       | Maximum tolerance | Maximum rating             |

|-----------------|-------------------|----------------------------|

| L <sub>0</sub>  | 5%                | 100mA at least at 13.56MHz |

| C <sub>0</sub>  | 5%                | 16V at least               |

| C <sub>1</sub>  | 2%                | 50V or 25V(*)              |

| C <sub>2a</sub> | 2%                | 50V or 25V(*)              |

| C <sub>2b</sub> | 2%                | 50V or 25V(*)              |

| Rq              | 5%                | N/A                        |

| R <sub>1</sub>  | 5%                | N/A                        |

| C <sub>RX</sub> | 5%                | 50V or 25V(*)              |

| Сумір           | 10%               | 4V at least                |

<sup>(\*)</sup> the choice of the voltage 50V or 25V is depending on the antenna characteristics and the operating conditions: the voltage at antenna terminals should be measured in the worst case conditions.

#### PN7120 Antenna Design and Matching Guide

#### 5. Performance verification and fine tuning

This section will show you on how to verify the performance of your device after the matching done. This verification gives only an overview of the performance of the system once a register tuning is also request to achieve the optimal performance.

There is two possibilities to check the performance of your antenna. The first method is to compare the interoperability with other devices. For example on card mode you can measure the communication distance with a reader from the market, on reader mode you can check the communication distance with well-known cards.

A second option is to check the performance of your device against a contactless standard. Currently 3 standards are the most common in the contactless world. There is not a rule to know which standard you must follow, but for payments purpose the EMV Co standard will be most commonly used. To check the interoperability with mobiles the NFC Forum can be a good option. For other kinds of applications the "ISO" specification is the most common used.

#### 5.1 Main specifications

#### 5.1.1 ISO/IEC 14443 specifics

The ISO/IEC 14443 (called "ISO" in the following, details see <u>ISO/IEC14443 [2]</u>) specifies the contactless interface as widely being used with contactless smartcards like e.g. MIFARE cards.

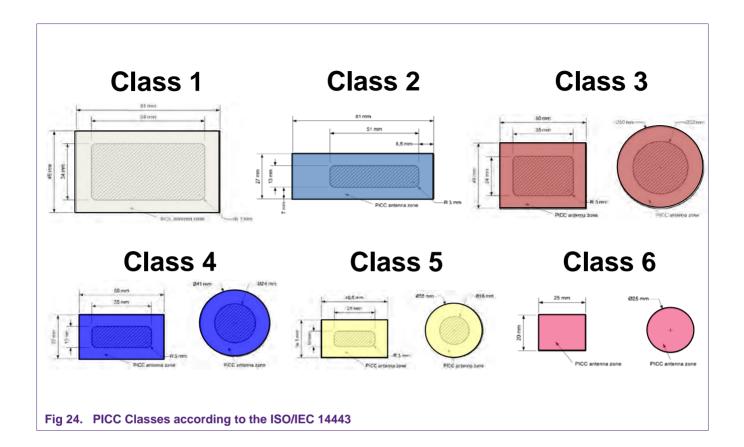

The ISO/IEC 14443 defines the communication between a reader ("proximity coupling device" = PCD) and a contactless smartcard ("proximity chip card" = PICC). In four parts it describes the physical characteristics (i.e. the size of the PICC antennas), the analog parameters like e.g. modulation and coding schemes, the card activation sequences ("Anticollision") and the digital protocol.

The ISO/IEC 10373-6 [1] describes the test setup and all the related tests for cards and the reader to test the ISO14443 requirements.

This specification covers only Type A and Type B communications.

#### 5.1.2 EMVCo specifics

<u>EMVCo standard [3]</u> it is the most used standard used for contactless payments purpose. It specifies a contactless interface for point of sales (POS) terminals (= PCD) and the corresponding contactless payment cards or mobiles (= PICC). This interface is very similar to the one defined ISO/IEC 14443, but it uses its own set of requirements and specification details. The EMVCo test equipment and way of testing is quite different from the test specification as defined in ISO/IEC 10373-6 [1].

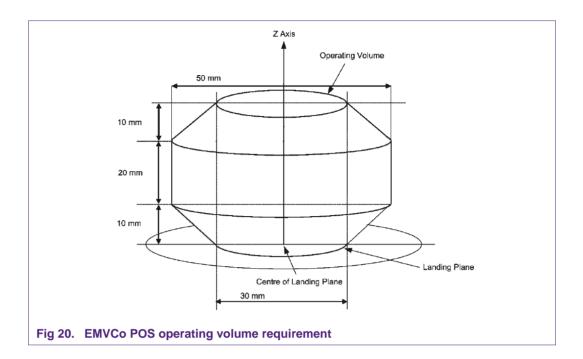

One main difference for the tests is the definition of an operating volume, as shown in *Fig* 20.

#### **PN7120 Antenna Design and Matching Guide**

Within this volume the given parameters need to be fulfilled.

This specification covers only Type A and Type B communications.

#### 5.1.3 NFC Forum specifics

The NFC Forum is a standard created to promote the use of NFC technology in consumer electronics, mobile devices, PCs, and more.

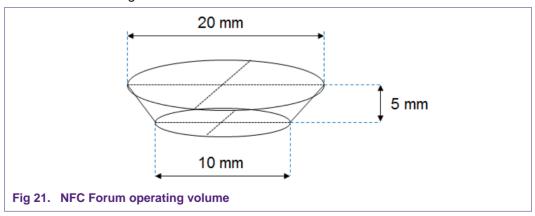

The standard NFC Forum device needs to fulfill the reader mode (Poller), and card mode (listener). One of the differences between this standard and the others is the use of 3 different protocols during test, the NFC-A, NFC-B and NFC-F and 6 different antennas for testing (3 for Poller tests and 3 for listener tests). Once again the NFC Forum test equipment and way of testing is quite different from the test specification as defined in ISO/IEC 10373-6 and EMV Co. Additionally the NFC Forum specifies an operating volume as shown in *Fig* 21.

#### **PN7120 Antenna Design and Matching Guide**

#### 5.2 Performance check against standards

During this section we will show the basics measurements that can be done to check the performance of your device.

We will show the measurements for reader mode and card mode using an EMV Co test bench. For every measurement we will give you the equivalent measurement on other standards.

#### 5.2.1 Reader Mode measurements

The reader mode measurements will be divided in two parts: The transmission part and the reception part.

For the transmission this part the most relevant tests will be:

- 1. Field strength measurement

- Waveform measurement

We will show how to perform this measurements using an EMV Test PICC, "ISO" Reference PICC and the NFC Forum Reference Listeners. These hardware can be bought from one of the accredited laboratories.

For the reception part, some specific test are described on these specifications. However we will not cover these tests on this document. To the test the reception part we will perform some functional tests.

#### 5.2.1.1 Field strength measurement

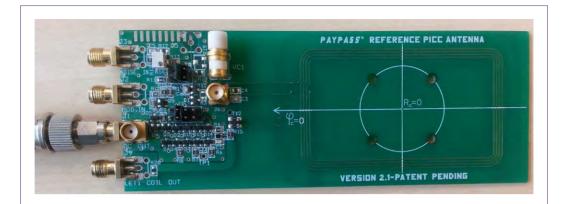

When the PN7120 is configured in READER mode, the strength of the emitted RF field can be measured by using a Reference PICC that is placed at a short distance from the PN7120 antenna. The reference PICC is calibrated on the relevant test bench: its output voltage corresponds to well-defined field strength.

The output voltage of the Reference PICC can be measured with an oscilloscope or directly measured with a voltmeter if the PN7120 is configured to emit a continuous RF field.

Based on the targeted standard compliance, the Reference PICC to be used can be different.

#### a. EMVCo example

The <u>EMVCo standard [3]</u> for payment applications defines a specific Reference PICC and a large operating volume is required: up to 4cm distance.

This operating volume specified can usually not be met by an embedded equipment application.

#### PN7120 Antenna Design and Matching Guide

Fig 22. EMV -TEST PICC connected on DC OUT port

#### Steps:

- 1) Connect the output J1 to an oscilloscope (1Mohms)

- 2) Set the jumper J8 in position 1-4, jumper on the "antenna side"

- 3) Place the EMV Test PICC in one position of the operating volume

- 4) Set your device to send continuous RF carrier.

- 5) Measure the mean value using an oscilloscope.

- 6) Check the min and max values against EMV Co specification.

#### b. ISO example

The Reference PICC to be used to check compliance with the <u>ISO/IEC14443 [2]</u> standard is described in the <u>ISO/IEC10373-6 [1]</u> standard.

Here is the specification of the field strength required by the ISO/IEC14443 [2] standard:

- No operating volume (i.e. area providing a field strength greater than 1.5A/m) is required

- > a minimum field strength of 1.5A/m must be achieved

- the maximum field strength must not exceed 7,5A/m

This requirement is usually met at short distance (<2cm) in case of an embedded equipment application.

This test was divided in two different tests H max and H min.

#### For Hmax test:

- 1) Tune the ISO Reference PICC to 19 MHz

- 2) Adjust the R2 load to obtain 3V measured on the connector CON3 when the TEST PCD assembly produce the H max

**PN7120 Antenna Design and Matching Guide**

- 3) Place the ISO Reference PICC in a test position on the device under test

- 4) Set your device to send continuous RF carrier.

- 5) Measure the DC output of the DC output CON3

- 6) The DC voltage at CON3 shall not exceed 3V

#### For Hmin test:

- 1) Tune the ISO Reference PICC to 13.56 MHz

- 2) Adjust the R2 load to obtain "Vload" (6V for class 1 ref PICC) measured on the connector CON3 when the TEST PCD assembly produce the H min

- 3) Place the ISO Reference PICC in a test position on the device under test

- 4) Set your device to send continuous RF carrier.

- 5) Measure the DC output of the DC output CON3

- 6) The DC voltage at CON3 shall exceed "Vload"

Some ReferencePICCs, which are commercially available (see *Fig 23*), are precalibrated and equipped with several jumper options to address the most relevant tests with a single ReferencePICC.

Fig 23. ISO/IEC 10373-6 Reference PICC Class 1

Still for each PICC Class a separated Reference PICC is required.

For example purpose the measurement was show using a Reference PICC Class 1, however PCD must support classes 1, 2, and 3.

The support of the classes 4, 5, and 6 is optional.

#### c. NFC Forum example

The <u>NFC Forum standard [4]</u> defines 3 different Reference PICCs so-called reference listeners: reference Listener 1, reference Listener 3 and reference Listener 6.

The required operating volume is much smaller than EMVCo: the distance is up to 0.5cm only. A test center can be defined for each Listener if the distance between the 3 tests centers can be inside a circle of 20 mm diameter.

The power emission test is divided in two different tests, one for minimum requirements and a second for maximum requirements.

For Minimum Power Emission Measurement:

- 1) Set the load of the reference Listener to 820 ohms

- 2) Place the Reference Listener in a test position on the device under test

- 3) Set your device to send continuous RF carrier.

- 4) Measure the DC output on the connector J1

- 5) Repeat this measurement for all test positions and all reference listeners

- 6) The DC voltage must be inside minimum and maximum limits

#### PN7120 Antenna Design and Matching Guide

For Maximum Power Emission Measurement:

- 1) Set the load of the reference Listener to 82 ohms

- 2) Place the Reference Listener in a test position on the device under test

- 3) Set your device to send continuous RF carrier.

- 4) Measure the DC output on the connector J1

- 5) Repeat this measurement for all test positions and all reference listeners

- 6) The DC voltage must be inside minimum and maximum limits

#### 5.2.1.2 NFC Signal shaping verification

The following verifications provide a quick way to check the shaping of the generated RF signal when the PN7120 is configured in READER mode.

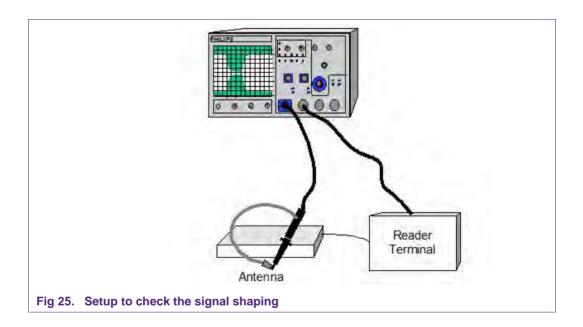

An oscilloscope with a bandwidth of at least 100MHz has to be used to carry out the shaping measurements (see *Fig 25*).

CH1: Use a loop with the ground line shortcut at the probe to enable inductive signal coupling. Hold the probe loop on top of the antenna. When the shaping compliance to a given standard is verified, the corresponding reference PICC must be connected to CH1.

Optional: CH2 used as trigger if possible

The absolute measured voltage in CH1 depends on the coupling (= distance) between the probe loop and the reader antenna.

The influence of the coupling on the shape can be neglected.

Once this quick verification has been done, the proper pick up coil must be used to check the compliancy to the different standards.

#### PN7120 Antenna Design and Matching Guide

#### a. Waveform measurement using an "ISO" reference PICC

We will show here how to measure the waveform of your device using an "ISO" reference PICC. This procedure is not the official procedure, once some analysis tools described on this specification will not be used. However this procedure it is a good overview of the waveform measurement defined on "ISO".

#### Procedure:

- 1) Tune the ISO Reference PICC to 16.5 MHz

- 2) Place the ISO Reference PICC in a test position on the device under test

- Adjust the R2 load to obtain "Vload" (6V for class 1 ref PICC) measured on the connector CON3

- 4) Set your device to send a Type A or Type B command.

- 5) Using an oscilloscope trigger your acquisition to correct acquire a Type A or Type B pause.

- Using the cursors of the oscilloscope measure the timings described on the figure below

- 7) The Timings measured must be inside minimum and maximum limits

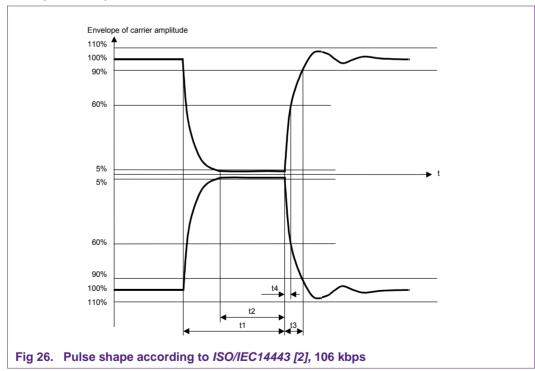

It is recommended to check the pulse shape with the Reference PICC according to the values given in Fig 26 and Table 4.

The times t1-t2 describe the time span, in which the signal falls from 90% down to below 5% of the signal amplitude.

#### PN7120 Antenna Design and Matching Guide

The rising time of the carrier envelope is t4. It must be checked that the carrier envelope at the end of the pause reaches 60% of the continuous wave amplitude within  $0.4\mu s$ .

Table 4. Pulse shapes definition according to ISO/IEC14443[2], 106 kbps

| Parameter | Condition | Min      | Max     |

|-----------|-----------|----------|---------|

| t1        |           | 28/fc    | 40.5/fc |

| t2        | t1>34/fc  | 7/fc     | t1      |

| t3        | t1<=34/fc | 1.5 x t4 | t1      |

| t4        |           | 0        | 6/fc    |

<sup>\*</sup>fc = carrier frequency

Please note that the standards can evolved. Final value must be directly retrieved from the latest official publication of the corresponding standard.

The type B modulation index m (see Fig 27) has also to be measured; the criteria are given in Table 5.

It must be noted that the PN7120 integrates an automatic adjustment of the modulation index to keep it constant whatever the antenna environment.

Tig 27: Modulation index (iii) calculation in Readen/Writer inode

Table 5. Type B 106kbps criteria according to ISO/IEC14443

| Parameter        | Min               | Max                 | Unit |

|------------------|-------------------|---------------------|------|

| Modulation index | 8                 | 14                  | %    |

| t <sub>f</sub>   | 0                 | 16/fc               |      |

| tr               | > 0 and tf – 8/fc | < tf+8/fc and 16/fc |      |

#### b. Waveform measurement using an EMV Test PICC

#### PN7120 Antenna Design and Matching Guide

The procedure to check the Waveform on EMV Co specification is very similar to the "ISO". The procedure below is not exactly the official procedure for the EMV Co testing, but it can gives you a good overview of the performance.

- Connect the output J9 to an oscilloscope (50ohms). Additionally EMVCo uses a 20 MHz filter between the oscilloscope and the EMV Test PICC.

- 2) Set the jumper J8 in position 1-2, jumper on the "connector side".

- 3) Place the EMV Test PICC in one position of the operating volume (only the center positions will be checked from 0 cm to 4 cm).

- 4) Set your device to send a Type A or Type B command.

- 5) Using an oscilloscope trigger your acquisition to correct acquire a Type A or Type B pause.

- 6) Using the cursors of the oscilloscope measure the timings described in Fig 27.

- 7) The Timings measured must be inside minimum and maximum limits

#### c. Waveform measurement using a NFC Forum reference Listener

The procedure for the NFC Forum is very similar to the two other specifications. However the particularity is the use of different sizes of antennas and loads during the tests. The test procedure should be done using the reference Listener 1, 2 and 3, and the loads 330 ohms and 820 ohms. This procedure is not exactly the official procedure for NFC Forum testing, but it can gives you a good overview of the performance.

- 1) Connect the output J4 (sense coil) to an oscilloscope (50ohms).

- 2) Set the jumper for the desired load (330 ohms or 820 ohms)

- 3) Place the reference Listener in one position of the operating volume.

- 4) Set your device to send a NFC A or NFC B or NFC F command.

- Using an oscilloscope trigger your acquisition to correct acquire NFC A or NFC B or NFC F command

- 6) Using the cursors of the oscilloscope measure the timings described in Fig 27.

- 7) The Timings measured must be inside minimum and maximum limits

#### 5.2.1.3 Reception check

For simplification purposes we will test the reception of our device on reader mode using some functional checks. Even if the 3 different standards presented until now, have their own tests to check the reception of the reader mode. We suggest to check the reception, checking the communication distance in READER mode with some typical cards:

- MIFARE Ultralight

- MIFARE DESFire

- FeliCa card

- ISO/IEC14443-B card

#### PN7120 Antenna Design and Matching Guide

Additionally using an oscilloscope and a spy coil between the card and the reader it is possible to check if the communication did not occurred because of the reader reception or card reception.

How to check if the problem is from the card or from the reader:

- If you can see the command from the reader but there is no response from the card. This is probably a card reception problem.

- After a response from the card the reader does not send the next expected command. This is probably a reader reception problem.

If you identify one of this situations, the RX path must be measured on the FAIL situation. If the signal is correct, the problem can come from other layers, digital and so on. Additionally you can use a RF spy from a test tool provider, to be able to check this point.

#### 5.2.2 Card mode measurements

The card mode measurements will be divided in two parts: the transmission and the reception part.

Fort the transmission part, basically we will check load modulation amplitude for the 3 different standards.

On the reception part, we will check the communication distance with some readers.

#### 5.2.2.1 Load modulation amplitude measurement

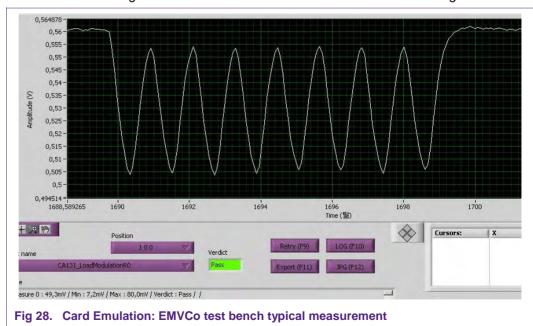

When the PN7120 is configured in CARD mode, the data are transmitted by modulating the amplitude of the external RF field. This is done simply by changing the load impedance presented to the antenna; it is called load modulation.

An illustration of the signal observed on an EMVCo test bench is shown in Fig 28.

#### PN7120 Antenna Design and Matching Guide

The different standards define the amplitude of the load modulation in listen mode at different distances and positions on the antenna.

The load modulation amplitude or sideband level amplitudes have to be measured by using a specific test bench which is different for each standard (ISO, EMVCo, NFC Forum).

#### a. How to check the LMA on different test benches using an oscilloscope

If you do not have a certified test bench to test the load modulation, you can use an oscilloscope + the reference antennas for the standard connected to a NFC reader emulator. The procedure will be the following:

- 1) Connect the output of the reference PCD to the oscilloscope.

- 2) Send a request using the requested power level.

- 3) Capture at least 7 cycles of the subcarrier load modulation response

- 4) Using cursors, measure the amplitude peak to peak of the response ("subcarrier")

- 5) The LMA measured must be inside minimum and maximum limits

Table 6. Load modulation HW for LMA test

| Table 6. Load modulation invitor Limit tool |          |              |                   |  |

|---------------------------------------------|----------|--------------|-------------------|--|

| Parameter                                   | EMV Co   | NFC Forum    | "ISO"             |  |

| Antenna                                     | Test PCD | Poller 0,3,6 | Test PCD assembly |  |

| Output                                      | J2       | J2           | Bridge*           |  |

| Input                                       | J1       | J1           | RF IN             |  |

<sup>\*</sup> Bridge corresponds to the output of the load modulation test circuit

#### 5.2.2.2 Reception test

The performance verification of the PN7120 application can be finalized by some functional checks in CARD mode.

We suggest to check the communication distance with some reader, such as:

- Pegoda

- Omnikey 5321

- ACR122

Additionally using an oscilloscope and a spy coil between the card and the reader it is possible to check if the communication did not occurred because of the reader reception or card reception.

How to check if the problem is from the card or the reader:

- If you can see the command from the reader but there is no response from the card. This is probably a card reception problem.

- After a response from the card the reader does not send the next expected command. This is probably a reader reception problem.

#### PN7120 Antenna Design and Matching Guide

If you identify one of this situations, the RX path must be measured on the FAIL situation. If the signal is correct, the problem can come from other layers, digital and so on.

Additionally you can use a RF spy from a test tool provider, to be able to check this point.

#### 5.3 Fine tuning through registers

In addition to the matching methodology, the RF performance can eventually be finetuned by the mean of registers which are accessible from the PN7120 host interface.

#### 5.3.1 Register setting command

Please refer to the <u>PN7120 User Manual [5]</u> contactless configuration chapter to get more insight on the values and addresses of the registers, especially about the related NCI command TLV structure.

The RF\_TRANSITION\_CFG parameter which allows to configure the CLIF registers is different from the above structure since there must be transitions to take into account, as soon as a parameter is valid for different modes (e.g. poller mode and listen mode) while its value can be different.

The extension of the TLV structure is given as below:

- The Tag Address is always 0xA0 0D

- The Length can be L=3, 4 or 6

- The Value is actually a secondary data area with a transition ID, the CLIF register offset (equivalent to an address), and the actual value.

| Tag<br>(2<br>Bytes) | Length<br>(1<br>Byte) | Value<br>(3, 4 or 5 Bytes, depending on the transition ID) |                                     |                      |

|---------------------|-----------------------|------------------------------------------------------------|-------------------------------------|----------------------|

|                     | 0x03                  | Transition<br>ID<br>(1 Byte)                               | CLIF register<br>offset<br>(1 Byte) | 1-Byte reg.<br>value |

| 0xA0 0D             | 0x04                  |                                                            |                                     | 2-Byte reg.<br>value |

|                     | 0x05                  |                                                            |                                     | 4-Byte reg.<br>value |

Fig 29. CLIF NCI Structure

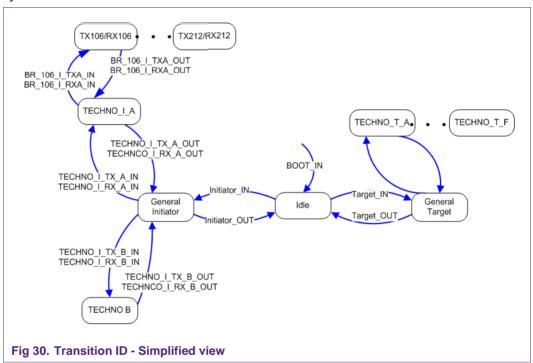

Basically, depending on the polling loop events, the transition ID corresponds to a set of transitions applied in the registers.

#### PN7120 Antenna Design and Matching Guide

The transition ID depends on

- IN vs. OUT

- In each IN transition a set of CLIF registers is loaded out of the EEPROM

- In each OUT transition the settings are reverted

- Initiator vs. Target

- TX vs. RX

- Technology (A, B, F, etc.)

- Baud rate (106kb/s etc.)

A simplified view of the different transition IDs is depicted in *Fig 30*. It does not include asymmetric data rates for instance.

Basically, PN7120 goes to one state or another, but cannot jump to a state where no link is defined, which makes the solution more robust. The transitions are defined as below:

- BOOT

- Called at boot time

- Basic initialization of CLIF (e.g. SMU\_ANA\_TX\_STANDBY\_REG)

- INITIATOR

- Called at the beginning of the poller phase

# **PN7120 Antenna Design and Matching Guide**

o Initialization common Reader/Initiator mode settings

#### - TARGET

- Called when external field is detected and CE/P2P Target is active

- Initialization of common CE/Target mode settings

- TECHNO\_I\_RX\_X, TECHNO\_I\_TX\_X, TECHNO\_T\_RX\_X, TECHNO\_T\_TX\_X

- Initialization of common technology dependent settings for transmitter and receiver

#### - BR XXX

Initialization of bit rate specific settings for transmitter and receiver for all different technologies / modes

The exhaustive list of transitions IDs is given as below.

Table 7. Transition ID values

| Transition ID                | IN | OUT |

|------------------------------|----|-----|

| RF CLIF BOOT                 | 0  | 1   |

| RF_CLIF_CFG_IDLE             | 2  | 3   |

| RF CLIF CFG INITIATOR        | 4  | 5   |

| RF CLIF CFG TARGET           | 6  | 7   |

| RF CLIF CFG I PASSIVE        | 8  | 9   |

| RF CLIF CFG I ACTIVE         | Α  | В   |

| RF CLIF CFG T PASSIVE        | С  | D   |

| RF CLIF CFG T PREACTIVE      | E  | F   |

| RF_CLIF_CFG_T_ACTIVE         | 10 | 11  |

| RF CLIF CFG TECHNO I TXA     | 12 | 13  |

| RF CLIF CFG TECHNO I RXA P   | 14 | 15  |

| RF CLIF CFG TECHNO I TXB     | 16 | 17  |

| RF CLIF CFG TECHNO I RXB     | 18 | 19  |

| RF CLIF CFG TECHNO I TXF     | 1A | 1B  |

| RF CLIF CFG TECHNO I RXF P   | 1C | 1D  |

| RF_CLIF_CFG_TECHNO_I_RXF_A   | 1E | 1F  |

| RF CLIF CFG TECHNO I TX15693 | 20 | 21  |

| RF CLIF CFG TECHNO I RX15693 | 22 | 23  |

| RF CLIF CFG TECHNO T TXA P   | 24 | 25  |

| RF CLIF CFG TECHNO T RXA     | 26 | 27  |

| RF CLIF CFG TECHNO T TXB     | 28 | 29  |

| RF CLIF CFG TECHNO T RXB     | 2A | 2B  |

| RF_CLIF_CFG_TECHNO_T_TXF_P   | 2C | 2D  |

| RF CLIF CFG TECHNO T TXF A   | 2E | 2F  |

# PN7120 Antenna Design and Matching Guide

| Transition ID              | IN | OUT |

|----------------------------|----|-----|

| RF CLIF CFG TECHNO T RXF   | 30 | 31  |

| RF_CLIF_CFG_BR_106_I_TXA   | 32 | 33  |

| RF CLIF CFG BR 106 I RXA P | 34 | 35  |

| RF CLIF CFG BR 106 I RXA A | 36 | 37  |

| RF CLIF CFG BR 212 I TXA   | 38 | 39  |

| RF CLIF CFG BR 212 I RXA   | 3A | 3B  |

| RF_CLIF_CFG_BR_424_I_TXA   | 3C | 3D  |

| RF CLIF CFG BR 424 I RXA   | 3E | 3F  |

| RF CLIF CFG BR 848 I TXA   | 40 | 41  |

| RF CLIF CFG BR 848 I RXA   | 42 | 43  |

| RF CLIF CFG BR 106 I TXB   | 44 | 45  |

| RF CLIF CFG BR 106 I RXB   | 46 | 47  |

| RF CLIF CFG BR 212 I TXB   | 48 | 49  |

| RF CLIF CFG BR 212 I RXB   | 4A | 4B  |

| RF CLIF CFG BR 424 I TXB   | 4C | 4D  |

| RF CLIF CFG BR 424 I RXB   | 4E | 4F  |

| RF_CLIF_CFG_BR_848_I_TXB   | 50 | 51  |

| RF CLIF CFG BR 848 I RXB   | 52 | 53  |

| RF CLIF CFG BR 212 I TXF   | 54 | 55  |

| RF CLIF CFG BR 212 I RXF P | 56 | 57  |

| RF CLIF CFG BR 212 I RXF A | 58 | 59  |

| RF CLIF CFG BR 424 I TXF   | 5A | 5B  |

| RF CLIF CFG BR 424 I RXF P | 5C | 5D  |

| RF CLIF CFG BR 424 I RXF A | 5E | 5F  |

| RF CLIF CFG BR 26 I TX     | 60 | 61  |

| RF CLIF CFG BR 26 I RX     | 62 | 63  |

| RF CLIF CFG BR 53 I TX     | 64 | 65  |

| RF CLIF CFG BR 53 I RX     | 66 | 67  |

| RF CLIF CFG BR 106 T TXA P | 68 | 69  |

| RF CLIF CFG BR 106 T TXA A | 6A | 6B  |

| RF_CLIF_CFG_BR_106_T_RXA   | 6C | 6D  |

| RF CLIF CFG BR 212 T TXA   | 6E | 6F  |

| RF CLIF CFG BR 212 T RXA   | 70 | 71  |

| RF CLIF CFG BR 424 T TXA   | 72 | 73  |

| RF CLIF CFG BR 424 T RXA   | 74 | 75  |

| RF CLIF CFG BR 848 T TXA   | 76 | 77  |

# **PN7120 Antenna Design and Matching Guide**

| Transition ID              | IN | OUT |

|----------------------------|----|-----|

| RF CLIF CFG BR 848 T RXA   | 78 | 79  |

| RF_CLIF_CFG_BR_106_T_TXB   | 7A | 7B  |

| RF CLIF CFG BR 106 T RXB   | 7C | 7D  |

| RF CLIF CFG BR 212 T TXB   | 7E | 7F  |

| RF CLIF CFG BR 212 T RXB   | 80 | 81  |

| RF CLIF CFG BR 424 T TXB   | 82 | 83  |

| RF_CLIF_CFG_BR_424_T_RXB   | 84 | 85  |

| RF CLIF CFG BR 848 T TXB   | 86 | 87  |

| RF CLIF CFG BR 848 T RXB   | 88 | 89  |

| RF CLIF CFG BR 212 T TXF P | 8A | 8B  |

| RF CLIF CFG BR 212 T TXF A | 8C | 8D  |

| RF CLIF CFG BR 212 T RXF   | 8E | 8F  |

| RF CLIF CFG BR 424 T TXF P | 90 | 91  |

| RF CLIF CFG BR 424 T TXF A | 92 | 93  |

| RF CLIF CFG BR 424 T RXF   | 94 | 95  |

| RF CLIF GTM A              | 96 | 97  |

| RF_CLIF_GTM_B              | 98 | 99  |

| RF CLIF GTM FELICA         | 9A | 9B  |

| RF CLIF CMA                | 9C | 9D  |

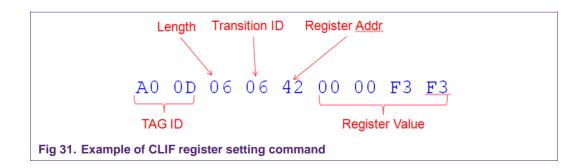

The registers can be one to 4 Bytes long. As an example, *Fig 31* shows the CLIF ANA TX AMPLITUDE REG register in transition TARGET IN to 0xF3F30000.

Note that the byte order for the register value is defined as Little Endian, meaning LSByte written first (LSB to MSB).

The order of the different bytes is given as follows (32 bits):

[7:4] [3:0] [15:12] [11:8] [23:20] [19:16] [31:28] [27:26]

## **PN7120 Antenna Design and Matching Guide**

## 5.3.2 Configuring load modulation in CARD mode

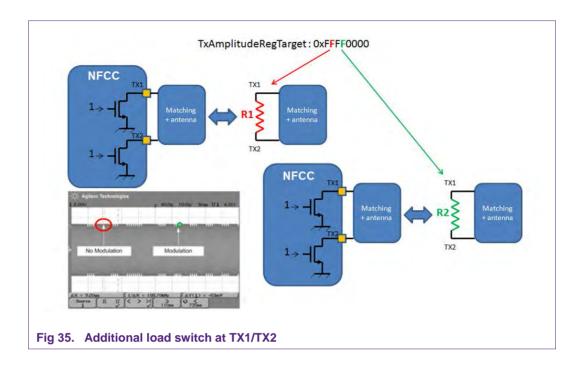

In CARD mode, load modulation is performed by switching the ANT1/ANT2 pins between high impedance to low impedance, which switches the CANT capacitors in parallel to the antenna ON and OFF.

#### 5.3.2.1 CLIF ANA TX AMPLITUDE REG

It is also possible to have an extra load switch between TX1 & TX2 in addition to CANT capacitors, which increases the LMA effect further.

This is based on the CLIF\_ANA\_TX\_AMPLITUDE\_REG register using TX\_GSN\_CW\_CM and TX\_GSN\_MOD\_CM parameters.

| Register name             | Transition ID | Register Address | Default Value |

|---------------------------|---------------|------------------|---------------|

| CLIF_ANA_TX_AMPLITUDE_REG | 0x06          | 0x42             | 0xFFF10000    |

| CLIF_ANA_TX_AMPLITUDE_REG | 0x9A          | 0x42             | 0xF1F10001    |

Fig 32. Fine tuning of CLIF\_ANA\_TX\_AMPLITUDE\_REG register in CARD mode

This tuning must ensure a correct operation and interoperability between PCD and PICC products.

Performance for high distance communication (Low field strength) must be checked against readers like Pegoda and payment readers.

In addition to the readers, the following test benches shall be used to get the best performance:

- 1- EMVCo test bench to define minimum functionality for PICC and PCD usage vs. RF powering, frames, timings, Type A, Type B commands.

- 2- ISO test bench to verify the operation of a PICC vs. ISO/IEC 14443-2, and ensures independency vs. coupling effect.

This chapter covers the EMVCo test bench methodology. Please refer to  $\underline{Book\ D-EMVco}$  [3] chapter 3.4 and 4, to get more insight on Load Modulation definition, mechanism and timing constraints.

#### **Register definition**

Bits [27:24] & [19.16] adjust the N-MOS transistor conductance value applied during non-modulated phases (CW- Continuous Wave) and modulated phase (MOD- Modulation phase) respectively (see *Fig 33*).

[0001] means minimum conductance (maximum impedance), and vice versa.

Note that [0000] shall not be used.

## **PN7120 Antenna Design and Matching Guide**

Based on these adjustments, the load modulation shape can be improved to comply with the targeted standards, including interoperability.

| CLIF_ANA_TX_AMPLITUDE_REG |                     |                     |                                                                 |

|---------------------------|---------------------|---------------------|-----------------------------------------------------------------|

| Bit                       | Name                | Value<br>0xFFF10000 | Description                                                     |

| [31:28]                   | TX_GSN_CW_RM        | 1111                | gsn setting @ continuous wave in poll mode                      |

| [27:24]                   | TX_GSN_CW_CM        | 1111                | gsn setting @ continuous wave in listen mode                    |

| [23:20]                   | TX_GSN_MOD_RM       | 1111                | gsn setting @ modulation in poll mode                           |

| [19:16]                   | TX_GSN_MOD_CM       | 0001                | gsn setting @ modulation in listen mode                         |

| [15:14]                   | RFU                 | 00                  |                                                                 |

| [13:12]                   | TX_CW_AMPLITUDE_RM  | 00                  | Set amplitude of unmodulated carrier @ poll mode                |

| [11:10]                   | RFU                 | 00                  |                                                                 |

| [9:8]                     | RFU                 | 00                  |                                                                 |

| [7:3]                     | TX_RESIDUAL_CARRIER | 00000               | Set amplitude of unmodulated carrier                            |

| [2]                       | TX_CW_TO_MAX_RM     | 0                   | TX HI output is the maximum voltage obtainable from charge pump |

| [1]                       | RFU                 | 0                   |                                                                 |

| [0]                       | TX_PD               | 0                   | Charge pumps clamped to tvdd                                    |

Fig 33. CLIF\_ANA\_TX\_AMPLITUDE\_REG register definition in listen mode

## Register setting procedure

a) Adjusting CW GSN to get optimal field strength from the reader (best sensitivity on RX)

#### Parameter

- 1- CLIF ANA TX AMPLITUDE REG [19:16]= [6] (e.g. of fix value)

- 2- CLIF ANA TX AMPLITUDE REG [27:24]= From 1 to F

## Measurement

- 1- Run EMVCo CA121 @ 4cm (or 5cm if no proven results)

- 2- Read distance on Pegoda

## **Target**

- 1- Select the range of CW for which CA121 passes (OK)

- 2- Get the best CW value which provides the highest distance

- b) Adjusting MOD GSN to get optimal Pegoda distance (optimal LMA on TX)

### Parameter

- 1- CLIF\_ANA\_TX\_AMPLITUDE\_REG [27:24]= [best value from previous test]

- 2- CLIF\_ANA\_TX\_AMPLITUDE\_REG [19:16]= Adjust to 1, 3, 9, F

## **PN7120 Antenna Design and Matching Guide**

## Measurement

- 1- Read distance on Pegoda

- 3- Perform EMVCo test CA131 @ 2 (LMA) and get value.

## Target

- 1- Get MOD for highest distance, and confirm

- 2- Confirm LMA passes for selected MOD value and with 3cm and 4cm.

#### **Measurement examples**

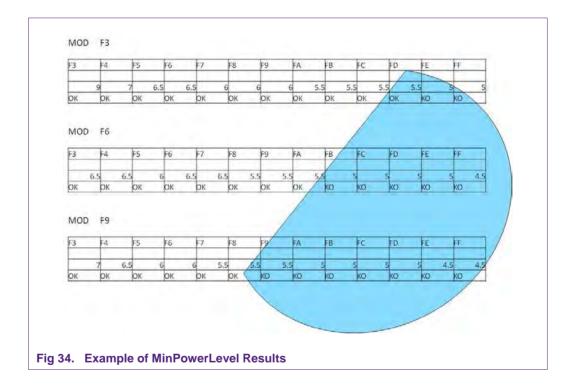

The graphs below show a selection of measurements regarding distance, MinPowerLevel and LMA. The best [CW, MOD] can be selected accordingly:

[CW, MOD] = (1,6), but a range within (1,6)(1,6) can be considered in case of interoperability issues.

#### **Schematics principle**

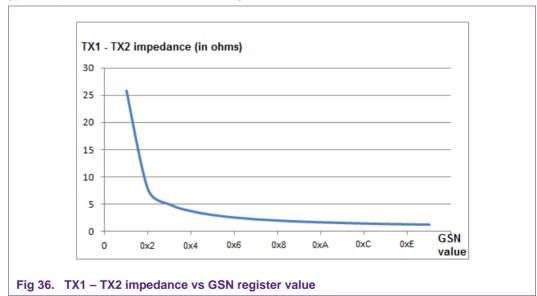

Typical TX impedance versus GSN register value is depicted on **Error! Reference** source not found.

When TX\_GSN\_MOD\_CM is different from TX\_GSN\_CW\_CM a load switch between TX1 & TX2 is applied on top of the C2b capacitor switch.

# **PN7120** Antenna Design and Matching Guide

Typical impedance on TX1 or TX2 for a given GSN value is shown on the curve below:

# **Transition to update**

The update of the CLIF\_ANA\_TX\_AMPLITUDE\_REG must be done for 2 different transitions:

- Transition 0x06 for type A and B

- Transition 0x9A for type F

## PN7120 Antenna Design and Matching Guide

## 5.3.3 Configuring pulse shape in poll mode

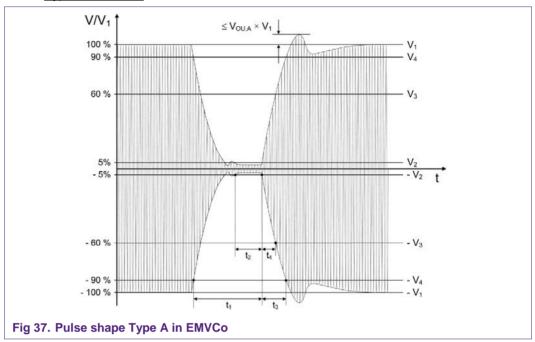

## a. Type A definition

The time t1-t2 describes the time span in which the signal falls from 90% down below 5% of the signal amplitude. The most critical time concerning rising carrier envelope is t4. It must be checked that the carrier envelope at the end of the pause reaches 60% of the continuous wave amplitude within  $0.4\mu s$ .

Ringing following the falling edge shall remain below Vou,A\*V1.

Overshoots immediately following the rising edge shall remain within (1+/- Vou,A)\*V1.

Please refer to Book D – EMVco [3] to get t1, t2, t3, t4 and Vou, A values.

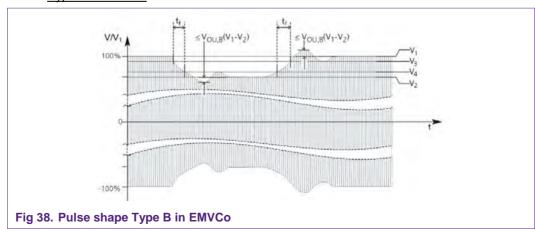

## b. Type B definition

## PN7120 Antenna Design and Matching Guide

V1 is the initial value measured immediately before any modulation is applied by the reader.

V2 is the lower value.

The modulation index (mi), V3 and V4 are defined as follows:

mi = (V1-V2)/(V1+V2)

V3 = V1 - 0.1\*(V1-V2)

V4 = V2 + 0.1\*(V1-V2)

Please refer to <u>Book D – EMVCo [3]</u> to get the values of modi, tf, tr and Vou,B.

The following register can be fine-tuned to improve the shaping of the pulse in Type A and Modulation index in Type B.

### 5.3.3.1 CLIF\_ANA\_TX\_AMPLITUDE\_REG

CLIF\_ANA\_TX\_AMPLITUDE\_REG with the transition ID #44 is the register to configure.

| Register name             | Transition<br>ID | Register Address | Default<br>Value |

|---------------------------|------------------|------------------|------------------|

| CLIF_ANA_TX_AMPLITUDE_REG | 0x44             | 0x42             | 0xFFFF1090       |

Fig 39. Fine tuning of CLIF\_ANA\_TX\_AMPLITUDE\_REG register

## **Register definition**

Bits [31:28] & [23.20] adjust the N-MOS transistor conductance value applied during non-modulated phases (CW- Continuous Wave) and modulated phase (MOD- Modulation phase) respectively.

- [31:28]: It is recommended to keep it at its maximum value (F), to get maximum envelop of the carrier amplitude of type B modulation

- [23:20]: It plays on the modulation index in Type B.

Bits [13:12] & [7:3] adjust the load modulation amplitude by choosing the amplitude of the output signal generated at PN7120 TX pin.

- [13:12] plays on modulation index Type B by degrading CW amplitude. When set to '3', type A amplitude appears larger than Type B

- [7:3] plays on the modulation index Type B. The higher the value, the higher the modulation index

Bit [2]: It is recommended to fix this value to '0' which improves the modulation index Type B.

## PN7120 Antenna Design and Matching Guide

|         | CLIF_ANA_TX_AMPLITUDE_REG |                     |                                                                 |  |  |

|---------|---------------------------|---------------------|-----------------------------------------------------------------|--|--|

| Bit     | Name                      | Value<br>0xFFFF1090 | Description                                                     |  |  |

| [31:28] | TX_GSN_CW_RM              | 1111                | gsn setting @ continuous wave in poll mode                      |  |  |

| [27:24] | TX_GSN_CW_CM              | 1111                | gsn setting @ continuous wave in listen mode                    |  |  |

| [23:20] | TX_GSN_MOD_RM             | 1111                | gsn setting @ modulation in poll mode                           |  |  |

| [19:16] | TX_GSN_MOD_CM             | 0001                | gsn setting @ modulation in listen mode                         |  |  |

| [15:14] | RFU                       | 00                  |                                                                 |  |  |

| [13:12] | TX_CW_AMPLITUDE_RM        | 00                  | Set amplitude of unmodulated carrier @ poll mode                |  |  |

| [11:10] | RFU                       | 00                  |                                                                 |  |  |

| [9:8]   | RFU                       | 00                  |                                                                 |  |  |

| [7:3]   | TX_RESIDUAL_CARRIER       | 00000               | Set amplitude of unmodulated carrier                            |  |  |

| [2]     | TX_CW_TO_MAX_RM           | 0                   | TX HI output is the maximum voltage obtainable from charge pump |  |  |

| [1]     | RFU                       | 0                   |                                                                 |  |  |

| [0]     | TX_PD                     | 0                   | Charge pumps clamped to tvdd                                    |  |  |

Fig 40. CLIF\_ANA\_TX\_AMPLITUDE\_REG register definition in poll mode

#### Register setting procedure

a) Adjusting TX\_RESIDUAL\_CARRIER

## **Parameter**

- 1- Start with CLIF\_ANA\_TX\_AMPLITUDE\_REG [7:0]= [90] (default value)

- 2- CLIF ANA TX AMPLITUDE REG [7:0] = A0 then B0, C0, C8 to increase index

- 3- CLIF\_ANA\_TX\_AMPLITUDE\_REG [7:0] = 80 then 70, 60 to decrease index

#### Measurement

1- Utilize a PICC card and an oscilloscope to observe the LMA and modulation index Type B @ 0cm, then 1cm. Both must meet the standard

## **Target**

1- Select CLIF\_ANA\_TX\_AMPLITUDE\_REG [7:0] for which modulation index is OK

If TX\_RESIDUAL\_CARRIER adjustment is not enough, try TX\_CW\_AMPLITUDE\_RM tuning.

b) Adjusting TX\_CW\_AMPLITUDE\_RM

### Parameter

## PN7120 Antenna Design and Matching Guide

- 1- Select the best CLIF ANA TX AMPLITUDE REG [7:3] value

- 2- CLIF\_ANA\_TX\_AMPLITUDE\_REG [13:12] = 0, 1, 2 or 3

#### Measurement

1- Utilize a PICC card and an oscilloscope to observe the LMA @ 0cm, then 1cm

#### Target

1- Select CLIF\_ANA\_TX\_AMPLITUDE\_REG [13:12] for which modulation index OK

If TX\_CW\_AMPLITUDE\_RM adjustment is not enough, try TX\_GSN\_CW\_RM & TX\_GSN\_MOD\_RM tuning.

c) Adjusting TX\_GSN\_CW\_RM & TX\_GSN\_MOD\_RM

#### Parameter

- 1- Keep CLIF ANA TX AMPLITUDE REG [31:28] = F

- 2- CLIF\_ANA\_TX\_AMPLITUDE\_REG [23:20] = 5

#### **Measurement**

1- Utilize a PICC card and an oscilloscope to observe the LMA @ 0cm, then 1cm

#### Target

1- Select CLIF ANA TX AMPLITUDE REG [23:20] for which modulation index OK

## 5.3.4 Optimizing Rx path in poll mode

## 5.3.4.1 CLIF\_ANA\_RX\_REG

*CLIF\_ANA\_RX\_REG* can be fine-tuned to improve the analog down-sampling and baseband amplification of the card response before it is processed by the digital block.

| Register name   | Transition<br>ID | Register Address | Default<br>Value |

|-----------------|------------------|------------------|------------------|

| CLIF_ANA_RX_REG | 0x22             | 0x44             | 0x00020029       |

| CLIF_ANA_RX_REG | 0x34             | 0x44             | 0x00020021       |

| CLIF_ANA_RX_REG | 0x35             | 0x44             | 0x00020021       |

| CLIF_ANA_RX_REG | 0x46             | 0x44             | 0x00020021       |

| CLIF_ANA_RX_REG | 0x4A             | 0x44             | 0x00020021       |

| CLIF_ANA_RX_REG | 0x4E             | 0x44             | 0x00020021       |

| CLIF_ANA_RX_REG | 0x52             | 0x44             | 0x00020021       |

| CLIF_ANA_RX_REG | 0x5C             | 0x44             | 0x00020021       |

| CLIF_ANA_RX_REG | 0x56             | 0x44             | 0x00020021       |

Fig 41. Fine tuning of CLIF\_ANA\_RX\_REG register

## **PN7120 Antenna Design and Matching Guide**

## **Register definition**

Bits [3:2] set the lower corner frequency of the BBA internal band-pass filter to reduce analog demodulation interferences.

#### Care:

- If the corner frequency is set too close or above the actual baseband signal frequency, the signal strength of the « useful » signal is dampened, leading to a loss of reading range, but at the same time it can also stabilize the reader performance

- => Tradeoff might be necessary.

- Furthermore the RX\_HPCF parameter influences the BBA amplification level (gain). The higher the HPCF, the lower the gain (1-2dB / per setting).

- For a reliable setting of the HPCF the observation of the frequency spectrum of the BBA input should be available for the given design

- => Since not available, each setting has to be evaluated by functional testing

#### Value range:

For 106kbps baseband signals: 0b00 ... 0b10

For 212kbps baseband signals: 0b00 ... 0b11

For 424kbps baseband signals: 0b00 ... 0b11

For 848kbps baseband signals: 0b00 ... 0b11

Bits [1:0] set the amplification level of the BaseBandAmplifier

#### Care:

- The gain must be set in combination with the HPCF parameter taking into account the optimization of the disturbances in the down-mixed RX signal.

#### Value range:

High performance & sensitivity for max. reading range: 0b10 ... 0b11

Strongly depends on the SNR in the system

- Typical: 0x01 ... 0x10

High robustness & stability but low reading range: 0x00

|        | CLIF_ANA_RX_REG |                     |                                                                      |  |

|--------|-----------------|---------------------|----------------------------------------------------------------------|--|

| Bit    | Name            | Value<br>0x00020021 | Description                                                          |  |

| [31:4] | RFU             | х                   |                                                                      |  |

| [3:2]  | RX_HPCF         | 00                  | Lower Corner Frequency: 00->45kHz, 01->85kHz, 10->150kHz, 11->250kHz |  |

| [1:0]  | RX_GAIN         | 01                  | Gain Adjustment BBA: 00->33dB, 01->40dB, 10->50dB, 11->57dB          |  |

Fig 42. CLIF\_ANA\_RX\_REG register definition

# **PN7120 Antenna Design and Matching Guide**

## Register setting procedure

#### Parameter

- 1- CLIF\_ANA\_RX\_REG [3:2]= from 00 to 11

- 2- CLIF\_ANA\_RX\_REG [1:0]= from 00 to 11

#### Measurement

1- Use DESFire EV1, MIFARE UL, TOPAZ and measure distance

## <u>Target</u>

1- Select settings for which distance is improved

**Remark:** For each communication type and baud rate, you must choose the right transition. In *Table 8* you will find the transition which corresponds to each tag type.

Table 8. CLIF\_ANA\_RX\_REG transitions

|               | Baud rate | Transition ID |

|---------------|-----------|---------------|

| Type A        | 106       | 34            |

|               | 212       |               |

| Type A        | 424       | 35            |

|               | 848       |               |

| _             | 106       | 46            |

|               | 212       | 4A            |

| Type B        | 424       | 4E            |

|               | 848       | 52            |

| Type F        | 212       | 56            |

|               | 424       | 5C            |

| Type ISO15693 | -         | 22            |

## **PN7120 Antenna Design and Matching Guide**

#### 5.3.4.2 CLIF SIGPRO RM CONFIG1 REG

*CLIF\_SIGPRO\_RM\_CONFIG1\_REG* can be used to tune the digital signal processing regarding the bit and subcarrier detection for the down-sampled and amplified listen mode response.

| Register name              | Transition<br>ID | Register<br>Address | Default<br>Value |

|----------------------------|------------------|---------------------|------------------|

| CLIF_SIGPRO_RM_CONFIG1_REG | 0x22             | 0x2D                | 0x000C4450       |

| CLIF_SIGPRO_RM_CONFIG1_REG | 0x34             | 0x2D                | 0x000C50DC       |

| CLIF_SIGPRO_RM_CONFIG1_REG | 0x3A             | 0x2D                | 0x001F5715       |

| CLIF_SIGPRO_RM_CONFIG1_REG | 0x3E             | 0x2D                | 0x001F5715       |

| CLIF_SIGPRO_RM_CONFIG1_REG | 0x42             | 0x2D                | 0x000F33DD       |

| CLIF_SIGPRO_RM_CONFIG1_REG | 0x46             | 0x2D                | 0x000C4805       |

| CLIF_SIGPRO_RM_CONFIG1_REG | 0x4A             | 0x2D                | 0x000C4805       |

| CLIF_SIGPRO_RM_CONFIG1_REG | 0x4E             | 0x2D                | 0x000C4805       |

| CLIF_SIGPRO_RM_CONFIG1_REG | 0x52             | 0x2D                | 0x000C4805       |

| CLIF_SIGPRO_RM_CONFIG1_REG | 0x56             | 0x2D                | 0x000CCC05       |

| CLIF_SIGPRO_RM_CONFIG1_REG | 0x5C             | 0x2D                | 0x000CCC05       |

Fig 43. Fine tuning of CLIF\_SIGPRO\_RM\_CONFIG1\_REG register

#### Register definition

Bits [15:12] define the threshold for the bit and subcarrier detection based on the amplitude of the correlated I & Q channel signal. It is used for all listen mode response types.

Bits [11:8] define the threshold for the phase shift detection based on the amplitude of the correlated I & Q channel. It is used for Type B (all baud rates) and Type A higher baud rates in addition to the Min Level

For Min\_Level and Min\_Level\_P:

- High value: receiver will be less sensitive but more robust against noise

- Low value: receiver will become sensitive to small card response but also to noise in the system

- Strong dependency on ANA\_RX\_REG

#### Care:

- Direct result of a register change is visible after a functional with Target activated

- Since the amplitude of the correlated I&Q channels is evaluated, the whole receiver path configuration has a major impact on the final register value (from the RXN/ RXP-pins to the BBA output)

#### Value range:

High performance & sensitivity for max. reading range: 0x2 ... 0x5

Typical: 0x5 ... 0x9

High robustness & stability but low reading range: 0x9 ... 0xF

## PN7120 Antenna Design and Matching Guide