# Freescale Semiconductor

# **Application Note**

Document Number: AN3513 Rev. 0, 09/2007

# **ColdFire ATA Host Controller**

by: Juan Mendoza

Freescale 32-bit Consumer and Industrial Operations

# 1 Introduction

This application note describes the ColdFire® ATA host controller. It covers signal description, functional description, programming model, and initialization.

The ATA host controller is used to connect:

- Hard disks

- CD-ROMs

- DVDs

- Flash storage devices

#### Features include:

- Programmable timing on the ATA bus. Works with wide range of bus frequencies

- 128-byte FIFO

- FIFO receive, transmit, and end of transmission alarms to DMA unit

- Zero wait-state transfers between DMA bus and FIFO

#### **Contents**

| 1 | Intro          | duction                            |  |

|---|----------------|------------------------------------|--|

| 2 | ATA            | Host Controller                    |  |

|   | 2.1            | External Signal Description        |  |

| 3 | ATA            | Functional Description             |  |

|   | 3.1            | Endianess                          |  |

|   | 3.2            | Sector Addressing                  |  |

|   | 3.3            | Programming Model                  |  |

| 4 | Initialization |                                    |  |

|   | 4.1            | ATA Host Controller Initialization |  |

|   | 4.2            | Data Access 11                     |  |

**ATA Host Controller**

# 2 ATA Host Controller

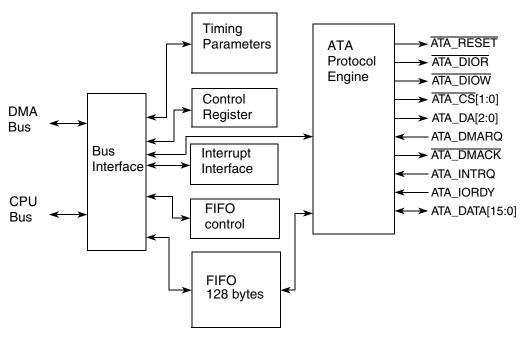

The figure below illustrates the block diagram of the ATA host controller:

Figure 1. Block Diagram

The ColdFire ATA host controller is fully compatible with: ATA/ATAPI-6 specification (*AT Attachment with Packet Interface Extension*). The ColdFire ATA host controller can control up to two ATA devices as defined in ATA/ATAPI-6 specification and supports all three modes:

- PIO mode 0, 1, 2, 3 and 4 for up to 16.7 MBytes/sec

- Multiword DMA mode 0, 1 and 2 for up to up to 16.7 MBytes/sec

- Ultra DMA modes

- Modes 0, 1, 2, 3 and 4 with bus clock of 50 MHz or higher for up to 66.7 MBytes/sec

- Mode 5 with system bus clock of 80 MHz or higher for 100 MBytes/sec

The ColdFire ATA controller is accessible by both the CPU and DMA. Before accessing the ATA bus, the host must program the timing parameters on the ATA bus. A set of timing registers for each transfer mode control the timing on the ATA bus. Most timing parameters are programmable as a number of clock cycles (1 to 255).

# 2.1 External Signal Description

**Table 1. External Signals**

| Name           | Function                            | Reset State | I/O             |

|----------------|-------------------------------------|-------------|-----------------|

| ATA_RESET      | ATA bus reset signal                | 0           | 0               |

| ATA_DIOR       | ATA bus read strobe                 | 1           | 0               |

| ATA_DIOW       | ATA bus write strobe                | 1           | 0               |

| ATA_CS[1:0]    | ATA bus chip selects                | 1           | 0               |

| ATA_DA[2:0]    | ATA bus address lines               | 0           | 0               |

| ATA_DMARQ      | ATA bus DMA request                 | _           | I/O             |

| ATA_DMACK      | ATA DMA acknowledge                 | 1           | 0               |

| ATA_INTRQ      | ATA bus interrupt request           | _           | I/O             |

| ATA_IORDY      | ATA bus I/O channel ready           | _           | 0               |

| ATA_DATA[15:0] | ATA data bus (little endian)        | Hi-Z        | Three-state I/O |

| ATA_BUFFER_EN  | ATA buffer direction control signal | 0           | 0               |

- ATA\_RESET When asserted, the ATA bus is in reset. After power-on, the ATA bus is in reset.

- ATA\_DIOR During PIO and Multiword DMA transfer, this signal functions as a read strobe. During Ultra DMA in burst, this signal functions as HDMARDY. During Ultra DMA out burst, this signal functions as host strobe.

- ATA\_DIOW During PIO and Multiword DMA transfer, this signal functions as a write strobe. During Ultra DMA burst, this signal functions as STOP and is asserted when the host wants to terminate a running UDMA transfer.

- ATA\_CS[1:0] The chip selects for the ATA bus.

- ATA\_DA[2:0] The address lines of the ATA bus.

- ATA\_DMARQ Device asserts to transfer data using Multiword DMA or Ultra DMA mode.

- ATA\_DMACK The host negates this signal when it grants the DMA request.

- ATA\_INTRQ The device asserts this signal to interrupt the host CPU.

- ATA\_IORDY This signal has three functions:

- IORDY Active low wait during PIO cycles

- DDMARDY Active low device ready during Ultra DMA out transfers

- DSTROBE Device strobe during Ultra DMA in transfers

- ATA\_DATA[15:0]) This is the bidirectional, three-state ATA data bus.

- ATA\_BUFFER\_EN ATA buffer directional control signal.

# 3 ATA Functional Description

The ATA interface provides two ways to communicate with the ATA peripherals connected to the ATA bus. After programming the appropriate timing parameters, two protocols can be active at the same time on the ATA bus.

- PIO Mode Can be performed at any time by the host CPU or the host DMA to the ATA bus. During a PIO transfer the incoming bus cycle is translated to an ATA PIO bus cycle by the ATA protocol engine. During PIO mode, the FIFO is not active, so no buffering of data occurs and the host CPU/DMA cycle is stalled until the ATA bus read data is available, or the bus data can be put on the ATA bus during a write. PIO mode is a slow protocol, mainly intended to program the ATA disk drive, but can be used to transfer data to/from the disk drive.

- DMA Mode Two different DMA protocols are supported on the ATA bus: Ultra DMA mode (UDMA) and Multiword DMA mode (MDMA). Selection is made using the ATA host control register (ATA\_CR). Data is transferred between the ATA bus and the FIFO, no direct interface exists between the ATA bus and the CPU/DMA. The ColdFire ATA host controller initiates DMA transfers by:

- 1. Writing the appropriate command sequence to the device registers for DMA transfer request.

- 2. After the command register is written, command execution begins.

- 3. The device will then request either a transfer or receive request to the DMA.

- The ColdFire ATA host controller must be programmed to accept the DMA request from the device. Once started, data transfer is organized between the ATA bus and the FIFO. The FIFO informs the ColdFire DMA unit when it needs to be refilled or emptied. In either case, it sends an alarm flag to the ColdFire DMA unit. When the ColdFire DMA unit receives the FIFO transmit alarm, it must write some data to the FIFO (typically 32bytes). When the ColdFire DMA unit receives the FIFO receive alarm, it should read some data from the FIFO (typically 32 bytes). The FIFO level at which the alarms are produced is programmable. For completeness, a third alarm to the ColdFire DMA unit is provided. This alarm signals the end of the transfer. The end of transfer has two possible outcomes.

- If the microprocessor is reading data from the device and there are less than FIFO\_ALARM bytes remaining in the FIFO, the host must transfer the bytes remaining in the FIFO to memory. The number of halfwords remaining in the FIFO are reported in the FIFO\_FILL register.

- If the microprocessor is writing data to the device, no FIFO manipulation is required after transfer completion.

All transfers between the FIFO and CPU or DMA are zero wait-state transfers. When a PIO access is performed during a running DMA transfer, the DMA transfer pauses, the PIO access finishes, and the DMA transfer resumes again.

The ColdFire ATA controller offers a buffer directional control signal, ATA\_BUFFER\_EN, which is used to control the direction of any bidirectional buffer requiring direction control. TIME\_ON and TIME\_OFF are timing registers that control data flow to avoid bus contention when switching the buffer on or off.

5

### 3.1 Endianess

The ATA interface operates in big endian mode. When the DRIVE\_DATA register is accessed, the bytes to/from the ATA bus are swapped. The byte order in 16-bit or 32-bit registers is:

- bits [7:0] : byte 0

- bits [15:8] : byte 1

- bits [23:8] : byte 2

- bits [31:24] : byte 3

This requires that when reading device information via the DRIVE\_DATA register, a byte swapping mechanism be implemented in software. For example:

```

uint16 readDriveRegisterData(void)

{

uint16 temp, returnValue;

return Value = DRIVE_DATA; returnValue = (*(vuint16*)(0x900000A0));

temp = (returnValue & 0xff00) >> 8;

returnValue = returnValue << 8;

return (returnValue | temp);

}</pre>

```

For data written by the CPU/DMA, no byte swap is necessary.

# 3.2 Sector Addressing

The addressing of data sectors recorded on the device's media is performed by logical sector address. In accordance with ATA/ATAPI-6 specification the ColdFire ATA controller supports 27-bit and 48-bit logical block addressing (LBA). In standards ATA/ATAPI-5 and earlier, a cylinder/head/sector addressing (CHS) translation was defined. This translation is obsolete, but may be implemented as defined in ATA/ATAPI-5.

# 3.3 Programming Model

The ColdFire ATA host controller has four groups of registers:

- ATA host controller registers This set of registers contains the:

- ATA\_CR The ATA control register allows access to ATA reset/enable, FIFO control, DMA request control, and handshake enabling/disabling.

- ATA\_ISR The ATA interrupt status register reports status of DMA requests, controller, FIFO, and interrupts.

- ATA\_IER The ATA interrupt enable register allows for the enabling/disabling of various FIFO and controller interrupts.

- ATA\_ICR The ATA interrupt clear register allows for the clearing of select FIFO error interrupts.

- FIFO\_ALARM The ATA FIFO alarm register holds the value at which the FIFO requests the DMA.

- ATA timing registers This set contains the registers that hold the timing values for PIO, MDMA, and UDMA modes. The timings for each particular mode are defined by the ATA/ATAPI-6

ColdFire ATA Host Controller, Rev. 0

#### **ATA Functional Description**

specification. Each register contains a number of clock cycles as calculated by dividing the timing constraint from the specification by the period of the system bus.

- TIME\_ON t<sub>ON</sub> parameter for buffer control to prevent bus contention

- TIME\_OFF t<sub>OFF</sub> parameter for buffer control to prevent bus contention

- PIO timing registers

- TIME\_1 t<sub>1</sub>

- TIME\_2W t<sub>2</sub> write

- TIME\_2R t<sub>2</sub> read

- TIME\_AX t<sub>A</sub>

- TIME\_PIORDX t<sub>RD</sub>

- TIME\_4 t<sub>4</sub>

- TIME\_9  $t_9$

- MDMA timing registers

- TIME\_M t<sub>M</sub>

- TIME\_JN t<sub>N</sub> and t<sub>J</sub>

- TIME\_D t<sub>D</sub>

- TIME\_K  $t_k$

- UDMA timing registers

- TIME\_ACK t<sub>ACK</sub>

- TIME\_ENV t<sub>ENV</sub>

- TIME\_RPX t<sub>RP</sub>

- TIME\_ZAH t<sub>ZAH</sub>

- TIME\_MLIX t<sub>MLI</sub>

- TIME\_DVH t<sub>DVH</sub>

- TIME\_DZFS t<sub>DZFS</sub>

- TIME\_DVS t<sub>DVS</sub>

- TIME\_CVH t<sub>CVH</sub>

- TIME\_SS t<sub>SS</sub>

- TIME\_CYC t<sub>CYC</sub> and t<sub>2CYC</sub>

ColdFire offers a buffer signal, ATA\_BUFFER\_EN, for direction control of any buffer requiring such control. To avoid bus contention when switching direction on the buffer, the ATA controller has two timing registers that control the timing of the data bus with respect to the ATA\_BUFFER\_EN signal.

- TIME\_ON Time after ATA\_BUFFER\_EN signal has asserted to start driving the ATA bus.

- TIME\_OFF Time before ATA\_BUFFER\_EN signal is deasserted to stop driving the ATA bus.

- ATA FIFO registers FIFO 16-bit and 32-bit data access registers.

- FIFO\_DATA32 32-bit wide data port to/from FIFO

#### ColdFire ATA Host Controller, Rev. 0

- FIFO\_DATA16 16-bit wide data port to/from FIFO

- FIFO\_FILL Reports number of halfwords present in FIFO

- ATA drive registers Access to the registers physically located on the ATA drive

- DRIVE\_DATA Drive data register read/write used for host PIO data transfer

- DRIVE\_FEATURES If read, error register is read. If written, features register is written

- DRIVE\_SECTOR\_COUNT Read/write drive sector count register

- DRIVE\_LBA\_LOW Read/write drive LBA\_LOW register

- DRIVE\_LBA\_MID Read/write drive LBA\_MID register

- DRIVE\_LBA\_HIGH Read/write drive LBA\_HIGH register

- DRIVE\_DEV\_HEAD Read/write register for selecting device 0 or device 1

- DRIVE\_COMMAND\_STATUS Read returns status, will write command register.

- DRIVE\_ALT\_STATUS/CONTROL If read, register contains same information as DRIVE\_STATUS. If written, register programs DRIVE\_CONTROL register.

ColdFire ATA host controller and device initialization covers three different groups of steps:

- 1. ATA module initialization

- Enable functionality of the ATA pins

- Reset the ATA module for interface programming

- Query device for status and capabilities

- 2. PIO initialization

- Set PIO timing registers

- Enable IORDY in ATA host configuration register (for PIO–3 and above)

- 3. MDMA/UDMA initialization

- Set either MDMA or UDMA timing registers

### 4.1 ATA Host Controller Initialization

1. Enable ATA functionality on the external pins. This involves modifying the pin assignment registers (PAR) on various ports on the ColdFire device. Initialization varies amongst specific ColdFire parts. The MCF5445x is used in the example that follows.

ColdFire ATA Host Controller, Rev. 0

Execute power-on/hardware reset protocol. Executed immediately after power-on reset (POR) or after a hardware reset. The host interrupt controller setup varies amongst specific ColdFire microprocessors.

```

uint32 i;

/*****

* Enable ATA interrupt at interrupt controller

*****************

MCF_INTC1_IMRH &= (~MCF_INTC_IMRH_INT_MASK54);

//allow interrupts from ATA

MCF_INTC1_ICR54 = 0x7; //Set level 7

// Set status register IPL to allow all interrupts

asm_set_ipl(0);

MCF_ATA_CR = 0x0;

//assertATAReset

wait_uS(25);

//wait 25uS as specified by ATA/ATAPI-6

MCF_ATA_CR = 0x40;

//deassertATAReset

wait_uS(20000);

//wait 2ms as specified by ATA/ATAPI-6

MCF_ATA_IER = 0x08;

//Enable ATA interrupt from device

```

3. Query device for capabilities. After power-on/hardware reset the host should issue an IDENTIFY DEVICE and/or IDENTIFY PACKET DEVICE command to determine the current status and features implemented by the device(s). Because the ATA host controller operates in big endian mode, it is necessary to byte swap the device information.

```

uint16 deviceIdInfo[256];

//512 byte sector/buffer

setTimingRegistersForPIOMode(0);

// Set PIO mode 0

// Enable IORDY at Host, needed for PIO-3 and above

MCF_ATA_CR = 0x41;

while((DRIVE_ALT_STATUS_CONTROL & 0x80) == 0x80);

//wait for BSY bit clear

DRIVE_DEV_HEAD = 0xE0; //Select Drive 0;

//wait for BSY bit clear

while((DRIVE_ALT_STATUS_CONTROL & 0x80) == 0x80);

while((DRIVE_ALT_STATUS_CONTROL & 0x40) != 0x40);

//wait for DRDY bit set

DRIVE_COMMAND_STATUS = 0xEC; //Write IDENTIFY_DEVICE command

/*wait for interrupt to signal completion of command device ready for buffer read*/

/****************

* ATA interrupt handler

*****************

__interrupt__

void ata_interrupt(void)

{

uint8 DevStatus;

uint16 temp;

DevStatus = DRIVE_COMMAND_STATUS;

/************************

```

ColdFire ATA Host Controller, Rev. 0

#### 4.1.1 PIO Initialization

Enabling PIO mode protocol requires the execution of the SET FEATURES command. The DRIVE\_SECTOR\_COUNT and DRIVE\_FEATURES registers are written with subcommand information used by the SET FEATURES command. The ATA interrupt is enabled, allowing the device to signal acceptance of command. The following example initializes device and host for PIO Mode 4.

```

//wait for BSY bit clear

while((DRIVE_ALT_STATUS_CONTROL & 0x80) == 0x80);

writeDriveRegister(DRIVE_DEV_HEAD, 0xE0);

//Select Drive 0

while((DRIVE_ALT_STATUS_CONTROL & 0x80) == 0x80);

//wait for BSY bit clear

while((DRIVE_ALT_STATUS_CONTROL & 0x40) != 0x40);

//wait for DRDY bit set

ATA\_IER = 0x08;

DRIVE_SECTOR_COUNT = 0x08 \mid 0x04;

// IORDY, PIO Mode 4 enabled

DRIVE_FEATURES = 0x03;

// Set transfer mode according

to DRIVE_SECTOR_COUNT register

DRIVE_COMMAND_STATUS = 0xEF;

//Execute SET_FEATURES command

/*wait for interrupt to signal command was executed and accepted*/

setTimingTimingRegistersForPIOMode(4); //

```

### 4.1.2 UDMA/MDMA Initialization

Enabling UDMA/MDMA Mode protocol requires the execution of the SET FEATURES command as well. The DRIVE\_SECTOR\_COUNT and DRIVE\_FEATURES registers are written with subcommand information used by the SET FEATURES command. The ATA interrupt is enabled, allowing the device to signal acceptance of command. The following example initializes device and host for MDMA mode 2.

```

#define MDMA 0x20

#define UDMA 0x40

#define MODE0 0x0

#define MODE1 0x1

#define MODE2 0x2

#define MODE3 0x3

#define MODE4 0x4

#define MODE5 0x5

//wait for BSY bit clear

while((DRIVE_ALT_STATUS_CONTROL & 0x80) == 0x80);

//Select Drive 0;

DRIVE DEV HEAD = 0 \times E0;

while((DRIVE_ALT_STATUS_CONTROL & 0x80) == 0x80);

//wait for BSY bit clear

while((DRIVE_ALT_STATUS_CONTROL & 0x40) != 0x40);

//wait for DRDY bit set

ATA IER = 0 \times 08;

/********************

* Set subcommand in Features register

* Set transfer mode based on value in Sector Count Register

```

ColdFire ATA Host Controller, Rev. 0

### 4.2 Data Access

The following examples demonstrate simple read or write transfers using all three transfer protocols. The examples transfer one sector using LBA.

#### 4.2.1 PIO Data Out Protocol

After programming the PIO timing registers and having selected the desired device (device 0 or device 1), the ColdFire ATA controller programs the device to execute the WRITE SECTOR(S) command to write data to the device using the selected PIO mode. The device sets the DRQ bit to signal to the ATA host controller that it is ready for data. The ATA IRQ line is asserted to signal that all data has been transferred.

```

while((DRIVE_ALT_STATUS_CONTROL & 0x80) == 0x80);

//wait for BSY bit clear

writeDriveRegister(DRIVE_DEV_HEAD, 0xE0);

//Select Drive 0;

while((DRIVE_ALT_STATUS_CONTROL & 0x80) == 0x80);

//wait for BSY bit clear

while((DRIVE_ALT_STATUS_CONTROL & 0x40) != 0x40);

//wait for DRDY bit set

DRIVE_SECTOR_COUNT = 0 \times 01;

//number of sectors to write

DRIVE LBA LOW = 0 \times 01;

DRIVE LBA MID = 0 \times 00;

DRIVE_LBA_HIGH = 0 \times 00;

// WRITE SECTOR(S) command

DRIVE_COMMAND_STATUS = 0x30;

while((DRIVE_ALT_STATUS_CONTROL & 0x08) != 0x08);

//wait for DRO bit set

for(i=0;i<256;i++)

DRIVE DATA = i;

/****wait for interrupt to signal completion of data transfer******/

```

### 4.2.2 PIO Data In Protocol

The PIO data read protocol is analogous to the PIO data out protocol. The microprocessor programs the device to launch READ SECTOR(S) command to read data from the device using the selected PIO mode. The device asserts its IRQ line to signal that it is ready to transfer data to the host.

ColdFire ATA Host Controller, Rev. 0

11

### 4.2.3 MDMA/UDMA Data Read

After programming the respective MDMA or UDMA timing registers, programming the DMA module to accept DMA requests from the device, and having selected the desired device (device 0 or device 1), the ColdFire ATA controller sends the READ DMA command using PIO mode to the device. This causes the device to request a DMA transfer. The device asserts its IRQ line to signal end of transfer. At the end of transfer the CPU or DMA must read any remaining bytes left in the FIFO.

#### NOTE

There may be less than FIFO\_ALARM bytes remaining so transfer is not automatic by the DMA. The FIFO\_FILL register reports the number of halfwords remaining in the FIFO.

```

uint16 sectorInfo[256]; //512 byte sector

FIFO_ALARM = 0x20; //Set FIFO alarm to half the size of the 128 byte-buffer

ATA_CR = 0x40; //Reset FIFO

/****************************

* FIFO normal operation, FIFO empty by DMA, DMA burst, IORDY, MDMA

* if you want UDMA write 0xDD

*************************

ATA_CR = 0xD9;

ATA_IER = 0x88;// allow DMA request and interrupt from device

/************************

* Setup the eDMA for ATA RX, channel 14 \,

MCF_EDMA_CR = MCF_EDMA_CR_ERCA;

//Round Robin priority

MCF_EDMA_ERQ = MCF_EDMA_ERQ_ERQ14;

//Allow ATA RX - 14

MCF_EDMA_EEI = MCF_EDMA_EEI_EEI14;

//Error interrupt enable for ATA RX

MCF_EDMA_TCD14_SADDR = MCF_EDMA_TCD_SADDR_SADDR(0x90000018); //Set the source Address

MCF_EDMA_TCD14_ATTR = MCF_EDMA_TCD_ATTR_SSIZE_32BIT | MCF_EDMA_TCD_ATTR_DSIZE_32BIT;

MCF_EDMA_TCD14_SOFF = MCF_EDMA_TCD_SOFF_SOFF(0x0);

MCF_EDMA_TCD14_NBYTES = MCF_EDMA_TCD_NBYTES_NBYTES(0x20);

//32 byte

MCF\_EDMA\_TCD14\_SLAST = 0x0;

//No adjustment

MCF_EDMA_TCD14_DADDR = MCF_EDMA_TCD_DADDR((uint32)&sectorInfo);

MCF\_EDMA\_TCD14\_CITER\_ELINK = 0x0;

MCF\_EDMA\_TCD14\_CITER = 0x10;

MCF\_EDMA\_TCD14\_DOFF = 0x4;

MCF\_EDMA\_TCD14\_DLAST\_SGA = 0x0;

```

Freescale Semiconductor

ColdFire ATA Host Controller, Rev. 0

```

MCF\_EDMA\_TCD14\_BITER = 0x10;

MCF\_EDMA\_TCD14\_BITER\_ELINK = 0x0;

MCF\_EDMA\_TCD14\_CSR = 0x0;

while((DRIVE ALT STATUS CONTROL & 0x80) == 0x80); //wait for BSY bit clear

writeDriveRegister(DRIVE_DEV_HEAD, 0xE0);

//Select Drive 0;

while((DRIVE_ALT_STATUS_CONTROL & 0x80) == 0x80);

//wait for BSY bit clear

while((DRIVE_ALT_STATUS_CONTROL & 0x40) != 0x40);

//wait for DRDY bit set

DRIVE_SECTOR_COUNT = 0 \times 01;

//sectors to be read

DRIVE_LBA_LOW = 0x1;

DRIVE_LBA_MID = 0 \times 00;

DRIVE_LBA_HIGH = 0 \times 00;

DRIVE_COMMAND_STATUS = 0xC8;

/****wait for interrupt to signal end of dma transfer****/

```

### 4.2.4 MDMA/UDMA Data Write

The DMA write protocol is analogous to the DMA read protocol. The ColdFire ATA controller sends the WRITE DMA command using PIO mode to the device causing the device to request a DMA transfer. The DMA request and interrupt request must be enabled. The device asserts its IRQ line to signal end of transfer.

#### NOTE

No FIFO manipulation is necessary at the end of transfer.

```

uint16 sectorInfo[256]; //512 byte sector

FIFO ALARM = 0x20; //Set FIFO alarm to half the size of the 128 byte-buffer

ATA CR = 0x40; //Reset FIFOuint16 sectorInfo[256]; //512 byte sector

/***********************************

* FIFO normal operation, FIFO empty by DMA, DMA burst, IORDY, MDMA

* if you want UDMA write 0xEE

*****************************

ATA_CR = 0xEA;

ATA IER = 0x88;

/***********************

* Setup the eDMA for ATA TX, channel 15

MCF_EDMA_CR = MCF_EDMA_CR_ERCA;

//Round Robin priority

MCF_EDMA_ERQ = MCF_EDMA_ERQ_ERQ15;

//Allow ATA TX

MCF EDMA EEI = MCF EDMA EEI EEI15;

//Error interrupt enable for ATA TX

MCF_EDMA_TCD15_SADDR = MCF_EDMA_TCD_SADDR_SADDR((uint32)&sectorInfo);

MCF_EDMA_TCD15_ATTR = MCF_EDMA_TCD_ATTR_SSIZE_32BIT | MCF_EDMA_TCD_ATTR_DSIZE_32BIT;

MCF_EDMA_TCD15_SOFF = MCF_EDMA_TCD_SOFF_SOFF(0x4);

//Size offset 4 bytes

MCF_EDMA_TCD15_NBYTES = MCF_EDMA_TCD_NBYTES_NBYTES(0x20);//32 byte or 8 longwords

MCF\_EDMA\_TCD15\_SLAST = 0x0;

MCF_EDMA_TCD15_DADDR = MCF_EDMA_TCD_DADDR_DADDR(0x90000018);

MCF\_EDMA\_TCD15\_CITER\_ELINK = 0x0;

MCF\_EDMA\_TCD15\_CITER = 0x10;

MCF\_EDMA\_TCD15\_DOFF = 0x0;

MCF\_EDMA\_TCD15\_DLAST\_SGA = 0x0;

MCF_EDMA_TCD15_BITER = 0x10; //Make sure DMA does not transfer more than sector size

MCF EDMA TCD15 BITER ELINK = 0x0;

MCF\_EDMA\_TCD15\_CSR = 0x0;

while((DRIVE_ALT_STATUS_CONTROL & 0x80) == 0x80);

//wait for BSY bit clear

writeDriveRegister(DRIVE_DEV_HEAD, 0xE0);

//Select Drive 0;

```

ColdFire ATA Host Controller, Rev. 0

ColdFire ATA Host Controller, Rev. 0

Freescale Semiconductor

13

#### How to Reach Us:

**Home Page:**

www.freescale.com

Web Support:

http://www.freescale.com/support

**USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc.

Technical Information Center, EL516

2100 East Elliot Road

Tempe, Arizona 85284

+1-800-521-6274 or +1-480-768-2130

www.freescale.com/support

Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street

Tai Po Industrial Estate

Tai Po, N.T., Hong Kong

+800 2666 8080

support.asia@freescale.com

For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center

P.O. Box 5405

Denver, Colorado 80217

1-800-441-2447 or 303-675-2140

Fax: 303-675-2150

LDCForFreescaleSemiconductor@hibbertgroup.com

Document Number: AN3513 Rev. 0 09/2007 Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics as their non-RoHS-compliant and/or non-Pb-free counterparts. For further information, see <a href="http://www.freescale.com">http://www.freescale.com</a> or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2007. All rights reserved.